соответствующих блоков формирования сигналов проверки группы, адресные выходы блока ввода информации сординрпы с а;фрсньгми входами де1 1ифра1Ора блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1228109A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для сопряжения вычислительной машины с внешними абонентами | 1984 |

|

SU1265784A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

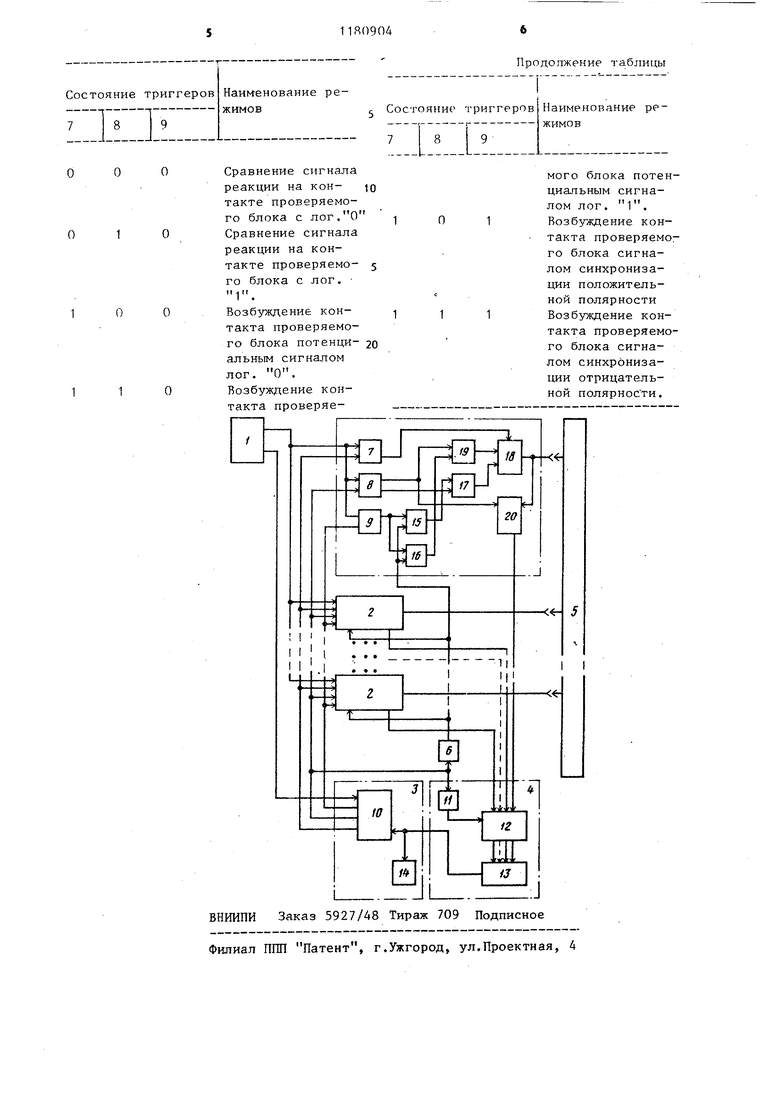

УСТРОЙСТВО ЛЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержапее блок ввода информации, блок регистрации, блок управления и группу блоков формирования сигналов проверки по числу точек контроля контролируемого блока, каждьй из которых включает три триггера, три элемента И, элемент ИЛИ и узел сравнения, причем в каждом блоке формирования сигналов проверки группы инверсный выход первого триггера и выходы первого и второго элементов И соединены с соответствуюпшми входами элемента ИЛИ, выход которого соединен с первым информационным входом узла сравнения и соответствующим вьтодом контролируемого блока, прямой выход второго триггера соединен с первым входом первого элемента И и вторым информационным входом узла сравнения, выходы узлов сравнения блоков формирования сигналов проверки группы соединены с соответствующими информационньми входами группы блока регистрации, отличающееся тем, что, с целью сокращения времени контроля, в него введены элемент задержки, а в каждьй блок формирования сигналов проверки группы - элемент И-НЕ, блок регистрации содержит регистр, элемент задержки и элемент ИЛИ, блок управления - дешифратор и триггер сбоя, причем информационные входы регистра образуют группу информационных входов блока регистрации, выходы регистра блока регистрации соединены с входами элемента ИЛИ, выход которого соединен с единичным входом триггера сбоя и запрещаюпщм входом дешифратора блока управления, первый и второй выходы которого соединены с входами синхронизаи и соответственно первых и вторых триггеров блоков формироваi ния сигналов проверки группы, третий выход дешифратора блока управле(Л ния соединен с входами синхронизации третьих триггеров блоков формирования сигналов проверки группы, в каждом блоке формирования сигналов проверки группы инверсный выход второго триггера соединен с первым входом второго элемента И, прямой выход третьего оо триггера соединен с первыми входами о третьего элемента И и элемента И-НЕ, вькоды которых соединены с вторыми входами второго и первого элементов И соответственно, вторые фь входы элементов И-НЕ и третьих элементов И блоков формирования сигналов проверки группы объединены и соединены с выходом элемента задержки, вход которого соединен с третьим выходом дешифратора блока управления и входом элемента задержки блока регистрации, выход которого соединен с входом записи регистра блока регистрации, информационные выходы блока ввода информации соединены с информационными входами триггеров

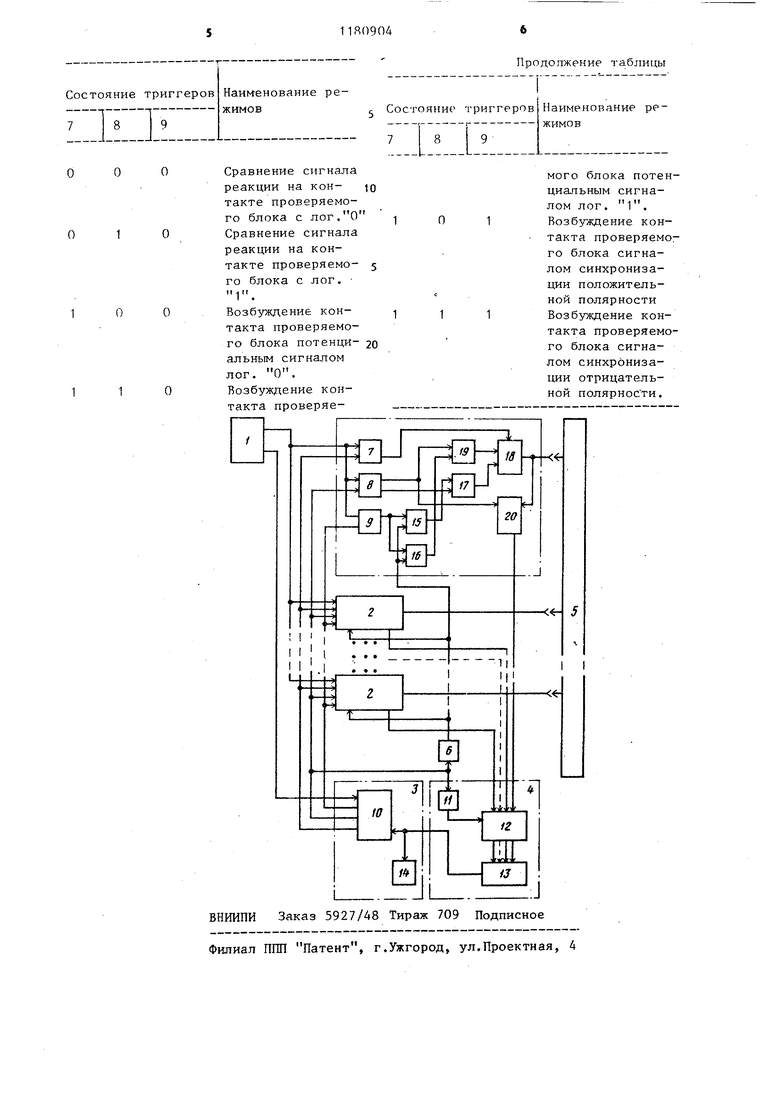

Изобретение относится к вычислительной технике и может быть исполь чопано для тестового контроля цифре bt.ix узлов ЭВМ. Целью изобретения является сокра щешге времени контроля. На чертеже представлено устройст во для контроля логических блоков. Устройство содержит блок 1 ввода информации, группу блоков 2 формиро вания сигналов проверки, блок 3 управления, блок 4 регистрации, контролируемый блок 5, элемент 6 задержки, триггеры 7 - 9, дешифра тор 10 блока управления, элемент 11 задержки блока регистрации, ре- -, гистр 12, элемент ИЛИ 13 блока регистрации, триггер 14 сбоя,узлы входяище в состав блока 2 формирования сигналов проверки группы: третий элемент И 15, элемент И - НЕ 16, второй элемент И 17, элемент ИЛИ 18 первый элемент И 19, узел 20 сравнв ния. Устройство работает следующим образом. Цепи начального сброса условно не показаны. Процесс контроля н чинается с занесения из блока 1 ввода информации в блоки 2 формирования сигналов проверки группы информации о состоянии входов, которая указыва ет, какие контакты проверяемого блока являются входными и выходными Одновременно в блок 3 управления на адресные входы дешифратора 10 с блока 1 ввода подается код, по которому вырабатывается сигнал зане сения состояния входов в блоки 2 формирования сигналов проверки груп пы. в исходном состоянии на выходе элемента ИЛИ 13 блока 4 регистрации логический О, который подается на первый запрещающий вход дешифратора 10 блока 3 управления и разрешает выработку управляющих сигналов. Затем из блока 1 ввода в блоки 2 формирования сигналов проверки группы при помощи сигналов управления с выхода дешифратора 10 блока 3 управления заносится информация, указьшающая тип сигнала на входах контролируемого логического блока 5, и далее из блока 1 ввода подается тест-набор, содержащий сигналы входных воздействий и ожидаемых (эталонных) реакций с проверяемого логического блока 5. При подаче из блока 1 ввода этого тест-набора на третьем выходе дешифратора 10 блока 3 управления вырабатывается сигнал управления, который используется для подачи синхросигнала и для стробирования регистра 12 блока 4 -регистрации. Синхросигнал подается на проверяемый логический блок 5 после окончания переходньгх процессов. Это достигаемся путем включения элемента 6 задержки. При несравнении эталонной реакции с реальной реакцией из блока 5 сигнал несравнения запоминается в регистре 12 блока 4 регистрации и с его выхода логическая 1 блокирует выработку управляющих сигналов в дешифраторе 10 блока 3 управления. По состоянию регистра 12 блока 4 регистрации можно узнать о номере неисправного выхода. В исходном состоянии триггеры 7-9 соответственно состояния входа, включения и синхронизации блоков 2 находятся в состоянии логического О. Информация из .блока 1 ввода считывается и поступает одновременно на входы триггеров 7-9. Одновременно с блока 1 ввода на адресные входы дешифратора 10 подается код и на первом выходе дещифратора появляется сигнал логической 1 по которому 31 происходит занесение информации в триггеры 7 (состояния входов) блоков 2 формирования сигналов проверки группы, т.е. указывается, какие контакты проверяемого блока 5 являются входами, а какие - выходами. Этот процесс происходит один раз в начале операции проверки того или иного блока. Затем из блока 1 ввода подается информация и соответствуюпшй код в дешифратор 10, по которому заносится информация в триггеры 9 (синхронизации), которая указывает тип сигнала на входах проверяемого логического блока 5. Лалее подаются соответствующие тест-наборы в триггеры 8 (включения). Блок 3 вырабатывает при этом на третьем выходе сигнал управления, по которому информация заносится в триггеры 8. Этот же управляюпщй сигнал используется для подачи синхросигнала и для стробирования через элемент 11 задержки регистра 12 блока 4 регистрации. Так как в исходном положении регистр 12 в нулевом состоянии, то на выходе, элемента ИЛИ 13 и триггера 14 сбоя находится логический О и дешифратор 10 не заблокирован. Выработка положительных и отрицательных синхросигналов на выходе блока 2 формирования сигналов провер ки группы происходит следующим образом. Триггеры 7 и 9 находятся в состоя нии логической 1, триггер 8 в .состоянии логического О. Поэтому по сигналу с третьего выхода блока 3 управления, который поступает через элемент задержки на вторые входы третьего элемента И 15-и элемента ИНЕ 16, на их выходах вырабатываются соответственно сигналы положительной и отрицательной поляризации. Так как на инверсном выходе триггера 8 логическая 1, то на выходе элемента И 17 сигнал положительной полярности, который поступает в элемент ИЛИ 18 и далее на входы проверяемого блока 5. Если триггер 8 в состоянии логической 1, то на выходе элемента И 19 появляется сигнал отрицатель ной полярности, которьй поступает на первый вход элемента ИЛИ 18 и в проверяемый блок 5. Таким образом, при 4 помощи одного тест-набора можно вьфабатывать на выходе блока 2 форьшрования сигналов проверки группы синхросигналы положительной и отрицательной полярности. Сравнение эталонное и выходной реакции с блока 5 производится узлом 20 сравнения. Выходы узлов 20 сравнения блоков 2 формирования сигналов проверки группы соединены с информационными входами регистра 12, на вход записи которого подается сигнал с выхода элемента 11 задержки Элемент 11 задержки блока 4 регистрации необходим для того, чтобы информацию в регистре 12 заносить после окончания переходных процессов в проверяемом блоке 5, когда на его выходах имеются устойчивые логические уровни, а также для устранения ложных сигналов несравнения во время действия синхросигналов. При несравнении эталонной реакции с выходной реакцией блока 5 в регистр 12 заносится логическая 1, триггер 14 сбоя устанавливается в 1 и дешифратор 10 заблокирован. Выработка управляюггсих сигналов, таким образом, прекращается. Номер неисправного выхода можно узнать по индикации регистра 12 (элементы индикации не указаны). В зависимости от состояния триггеров 7-9 блоки 2 формирования сигналов проверки могут выполнять один из шести режимов (см. табл.). В режиме сравнения реакции на контакте контролируемого блока 5 с эталонной реакцией, когда на выходе элемента ИЛИ 18 логическая 1, выходные сигналы с элементов 1ШИ 18 образуют с сигналами на контактах блока 5 функцию Йонтажные И. При этом единичные значения сигналов на выходах элементов ИЛИ 18 подавляются выходными сигналами логического О с блока 5. Узлы 20 сравнения необходимы для сравнения сигналов на контактах контролируемого блока 5 с сигналами на выходе триггера 8. Причем осуществляется сравнение как выходных, так и входных сигналов блока 5. Сравнение входных сигналов блока 5 указьгаает возможные замыкания контактов этого блока между собойесли сигнал на выходе блока 2 не совпадает с соответствуюш 1м сигналом на прямом выходе, триггера 8.

| Устройство для контроля дискретных объектов | 1976 |

|

SU642708A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1977 |

|

SU746554A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1983-04-01—Подача