54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1228109A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1180904A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1339568A1 |

| Устройство для поиска перемежающихся неисправностей | 1985 |

|

SU1262502A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для проверки монтажа | 1987 |

|

SU1509937A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для проверки логических схем цифровых узло ЭВМ. Известные устройства l} для кон троля цифровых узлов, содержащие бл ввода, блок памяти, регистр .настрой ки, коммутатор, блоки сравнения, ин дикации и управления и выполняющие подачу на контролируемый объект сиг налов проверки через специальный коммутатор. Недостатком этих устройств является их сложность. Наиболее близким по технической сущности, к изобретению является устройство для контроля логических- 6ЛОКО&, содержащее блок регистрации, блок ввода, блок управления и блоки формирования сигналов проверки по числу точек контро ля логического блока. Выход блока регистрации соединен с первым входом блока управления, первый выход которого сйединен с первыми управляющими входами блоков формирования сигналов проверки, подключенных выходами к соответствующим контрольным точкам логического блока, а информационными входами - к соответствующим выходам блока ввода, управляющий выход которого соединен со вторым .входом блока управления . Каждый 6JiOK формирования сигналов проверки включает элементы И, ИЛИ, триггер состояния входа, триггер включения и схему сравнения, первый вход которой соединен с выходом блока формирования сигналов проверки, информационные входы которого соответственно подключены к информационным входам первого, второго и третьего элементов И, а первый управляющий вход - к управляющим входам первого, второго и третьего элементов и, выход первого элемента И соединен со входом триггера состояния входа, подключенного прямым выходом к первому входу четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ. Выход второго элемента И соединен со входом триггера включения, выход которого подключен ко второму входу четвертого элемента И, первому входу пятого элемента И, соединенного выходом со вторым входом элемента ИЛИ, и вторым входом схемы сравнения.

При проверке этим устройством логических блоков, имеющих элементы памяти, могут возникнуть гоночные явления (наличие в данный момент двух или более нестабильных обратных связей) между элементами памяти Для исключения этих явлений при проверке логических блоков используют противогоночное кодирование таблиц проверки параметров блока. Противогоночное кодирование заключается в учете временных характеристик сигналов возбуждения проверяемого блока в чередукяцихся наборах,т.е. для подавления гонок в одной проверке используются три набора сигналов возбуждакяцих контакты проверяемого блока т оторые отличаются друг от друга тем, что во втором наборе присутствует сигнал искусственйый синхронизации, последний воздействует на те или иные элементы памяти логического блока.

Наличие избыточных наборов при проверке логических блоков, имекадих элементы памяти, увеличивает время проверки.

Целью изобретения является сокращение времени проверки.

Поставленная цель достигается тем, что в предложенном устройстве каждый блок формирования сигйШЬв проверки введены триггер синхронизации и шестой элемент И,соединенный первым входом с выходом схемы сравнения, а вторым - с инверсным выходом триггера синхронизации и третьим взсЬдом четвертого элемента

О 0.

и. Выход третьего - элемента И соединен со входом триггера синхронизации, прямой выход которого подключен ко второму входу пятого эле.чента И. Инверсный выход триггера состояния входа подключен к третьем входу элемента ИЛИ, выход которого соединен с первым входом схемы сравнения. Третий вход пятого элемента и выход шестого элемента И являются соответственно вторым управлякяцим входом и индикаторным выходом блока формирования сигналов проверки, которые соответственно подключены ко второму выходу блока управления и соот1ветствую цему входу блока регистрации .

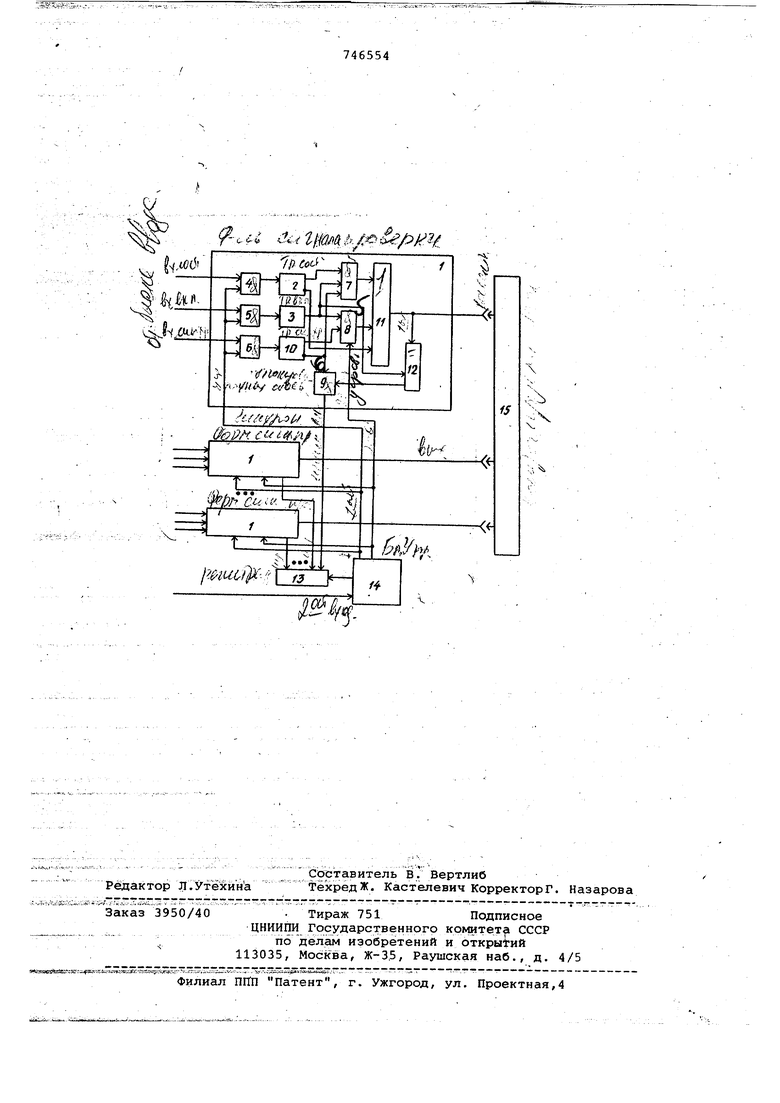

На чертеже показана структурная схема устройства.

Оно содержит блоки 1 формирования сигналов проверки, триггер 2 состояния входа, триггер 3 включения, элементы И 4-9, триггер 10 синхронизации, элемент ИЛИ 11, схему 12 сравнения, блок 13 регистрации, блок 14 управления.

Устройство работает следующим образом.

Блоки возбуждают определенные входные контакты контролируемого блока 15 и производят сравнение реакции схемы в соответствии с поступающими от блока ввода (на чертеже не показан) сигналами тестовой программы и эталонными реакциями.

Сигналами из блока ввода через элементы И 4-6 на триггерах 2,3,10 каналов 1 могут устанавливаться код в соответствии с таблицей.

Режим сравнения сигнала реакции на контакте проверяемого блока с эталонным сигналом О

Режим сравнения сигнала реакции на контакте проверяемого блока с эталонным сигналом 1

возбуждение контакта проверяемого блока сигналом О

Возбуждение контакта проверяемого блока сигналом

Возбуждение контакта проверяемого блока сигналом синхронизации Выходы элементов ИЛИ 11 блоков соединяются с соответствующими контактами блока 15. Если контакты блока 15 являются выходными (нулевое состояние триггеров 2), то выходные сигналы с элементов ИЛИ 11 образуют с сигналами на контактах блока 15 функцию монтажное И .(эле мент дот), При этом единичные значе ния сигналов на выходах элементов ИЛИ 11, обусловленные поступлением на вход элементов ИЛИ 11 единичных сигналов с инверсных выходов триг-геров 2, подавляются значением выходных сигналов реакции блока 15, т.е. на схемы 12 сравнения поступают сигналы реакции блока 15. Временные характеристики синхросигналов определяются сигналами с блока управления 14 на входах пятых элементов И блоков 1. Элементы И 9 блоков 1 блокируют ложные сбои при возбуждении контактов блока 15 синхросигналами. Блоки ровка осуществляется нулевыми значе ниями сигналов, поступающих с инверсных выходов триггеров 10. Схемы 12 сравнения необходимы для сравнения сигналов на контактах блока 15 с эталонными сигналами на прямых выходах соответствующих триг геров 2, причем осуществляется срав нение как выходных, так и входных сигналов проверяемогоблока 15. Сра нение входных сигналов блока 15 показывает возможные замыкания контак тов этого блока между собой. В этом случае входные сигналы с выходов элементов ИЛИ 11 образуют с сигналами замыкания контактов монтажное И, и блок 13 регистрации сбоев фиксирует неисправность в блоке 15. Таким образом, устройство обеспе чивает ускоренный по сравнению с прототипом контроль логических схем Формула Изобретения Устройство для контроля логически блоков, содержащее блок регистрации блок ввода, блок управления и блоки формирования сигналов проверки по числу точек контроля логического блок а ,выход-. блока регистраци.и оединен с первьЕГ ходом блока, управления jje gBbift 1нход::;5ет рого153 инея-тгпервыми управляющйьет входами блоков формирования сигналов проверки/подключенных вы содами к соответствуйщим контрольным точкам логического блока а информационными входами - к соот fSS - - ветствующим выходам блока ввода,управляющий выход которого соединен со втоЕ№1 входом блока управл ения,причем каждый блок формирования сигналов проверки включает элементы И,ИЛИ, триггер состояния входа, триггер включения и схему сравнения, первый вход которой соединен с выходом блока формирования сигналов проверки, информационные входы которого соответственно подключены к информационным входам первого, второго и третьего элементов И, а первый управляющий вход - к управляющим входам первого, второго и третьего элементов И, выход первого элементами соединен со входом триггера состояния входа, подключенного прямым выходом к первому входу четвертого элемента И, выход которого соединен с перйым входом элемента ИЛИ, выход второго элемента И соединен со входом триггера включения, выход которого подключен ко второму входу четвертого элемента И, первому входу пятого элемента И, соединенного выходом со вторым входом элемента ИЛИ, и вторым входом схему сравнения, о т л и ч а ющ ё ё с я тем, что, с цель сокращёНй1й р| ё1 1ёнйпроверки, в каждый блок формирования сигналов проверки введены триггер синхронизации и Шестой элемент И,соединенный первым входом с выходом . схемы сравнения, а вторым - с инверсным выходом триггера синхронизации и третьим входом четвертого элемента И, выход третьего элемента И соединен, со входом триггера синхронизации, прямой выход которого подключен ко второму в-ходу пятого элемента И, инверсный выход триггера состояния входа подключен к третьему входу элемента ИЛИ, выход которого соединен с первым входомчсхемы сравнения, третий вход пятого элемента И и выход шестого элемента И являются соответственно вторым управляю1Цим4 -- входом и индикаторным выходом блока формирования сигналов проверки, которые соотве-гственно подключены ко . второму выходу gjfoilg, управления и соответсУвуквдёну .pST CTрации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 354415, кл. G Об F 11/00, 1970, 2.Авторское свидетельство СССР по заявке № 2382083/18-24, кл, G Об F 15/46, 1976 (прототип).

,.

,i(d. . : p-4fti .(71

I

.:-nJ

1Щ,

Авторы

Даты

1980-07-05—Публикация

1977-08-08—Подача