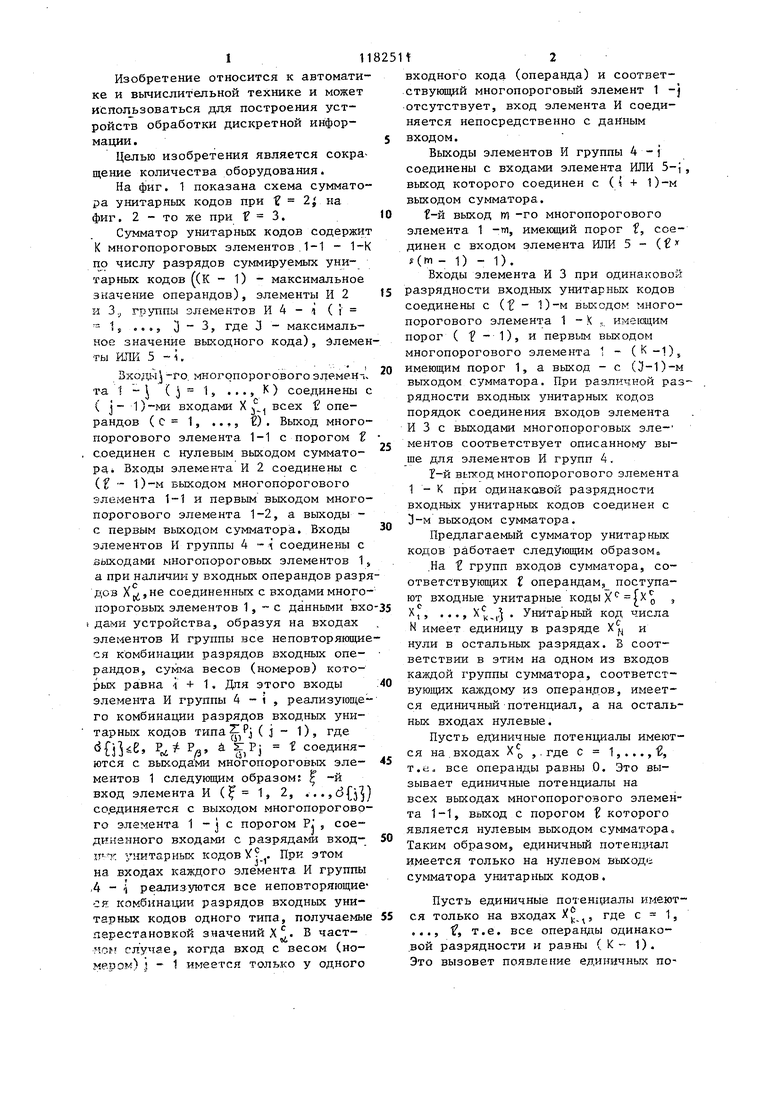

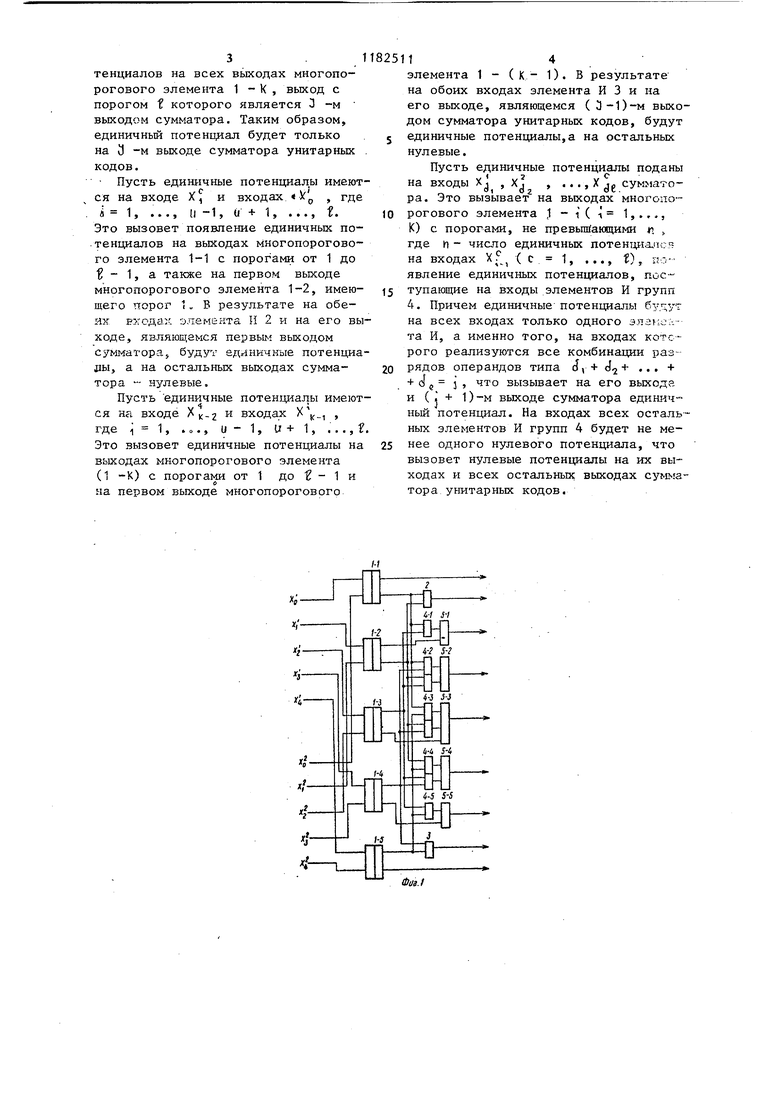

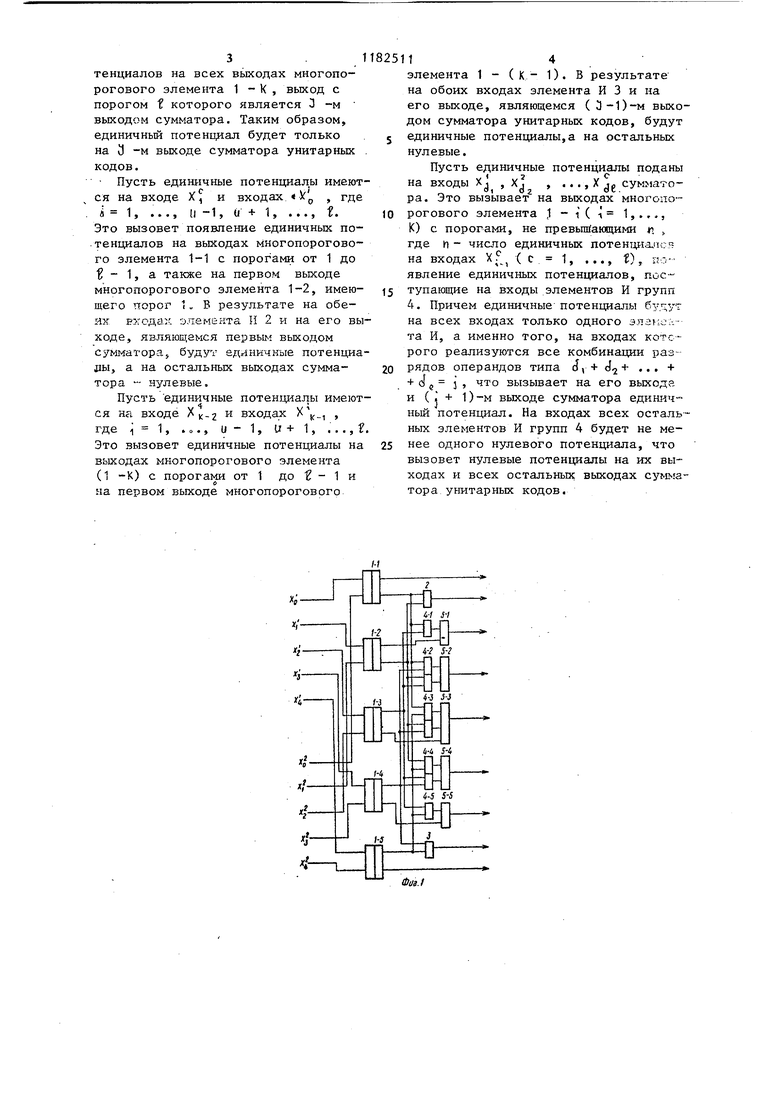

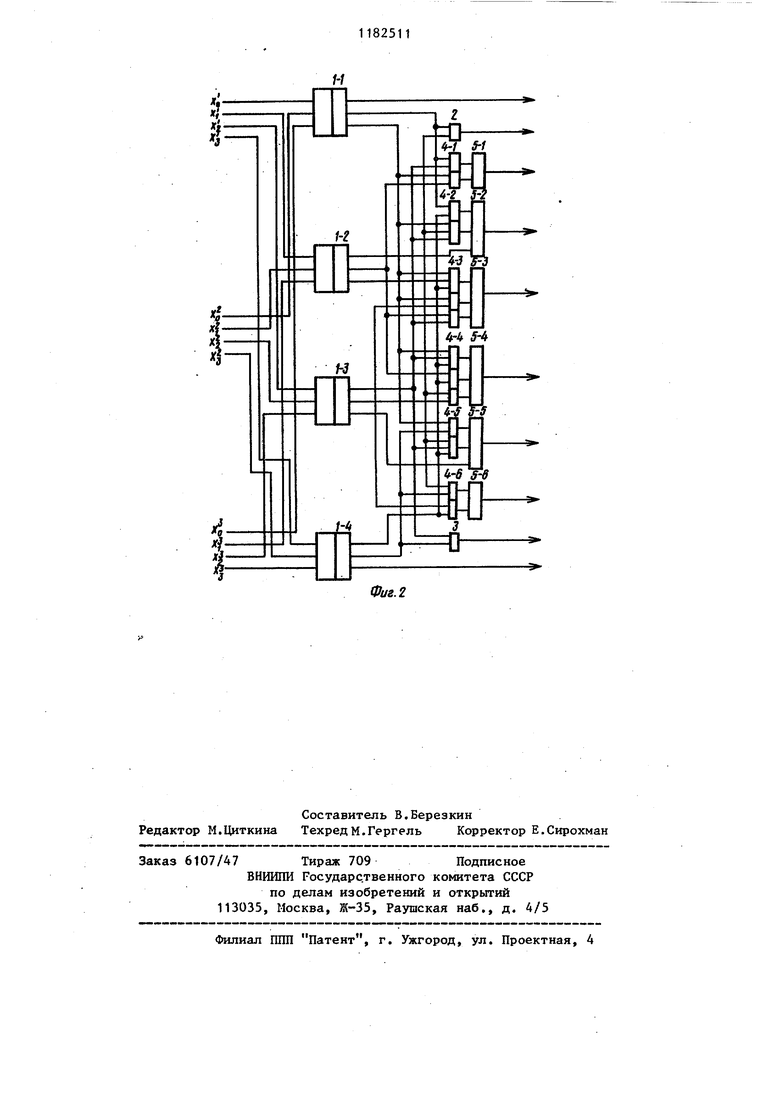

111 Изобретение относится к автоматике и вычислительной технике и может использоваться для построения устройств обработки дискретной информации . Целью изобретения является сокращение количества оборудования. На фиг. 1 показана схема сумматора унитарных кодов при 2 на фиг. 2 - то же при Е 3. Сумматор унитарных кодов содержит К многопороговых элементов . 1-1 - 1-К числу разрядов суммируемых унитарных кодов ((к - 1) - максимальное зкаче ше операндов), элементы И 2 и 3., группы элементов И 4 - i ( i Is ..., 3 3, где 3 - максимальное значение выходного кода), злемен гы ИЛИ 5 -L Входы -го. jviHoronoporoBoro элемен-, та 1 - ( 1, ..., К) соединены с ( J- 1)-ми входами X Д, всех С операндов ( С 1, ..,, к) . Выход многопорогового элемента 1-1 с порогом соединен с нулевым выходом сумматора Входы элемента И 2 соединены с (f - 1)-м выходом многопорогового элемента 1-1 и первым выходом многопорогового элемента 1-2, а выходы с первым выходом сумматора. Входы элементов И группы 4 - i соединены с выходами многопороговых элементов 1, а при наличии у входных операндов разря дов Хр,не соединенных с входами многопороговых элементов 1, с данными вхо i дами устройства, образуя на входах элементов И группы все неповторяющие ся комбинации разрядов входных oneрандов, cyMi-ia весов (номеров) которых равна 1 + 1, Для этого входы элемента И группы 4 -i , реализующего комбинации разрядов входных унитарных кодов ( i - 1), где , Р, Р., & rPj f соединяются с выходами многопороговых эле- ментов 1 следующим образом; -и вход элемента И ( 1, 2, ,. .,d{j соединяется с выходом многопороговрго элемента 1 -j с порогом Р; , соединенного входами с разрядами вход- ;гт: унитарных кодов У . При этом на входах кажд,ого элемента И группы ,4 - реапиззпотся все неповторяющиеся, комбинации разрядов входных унитарных кодов одного типа, получаемые перестановкой значений Х. В част .ои случае, когда вход с весом (номеоом) i - 1 имеется только у одного t2 входного кода (операнда) и соответствующий многопороговьш элемент 1 -j отсутствует, вход элемента И соединяется непосредственно с данным входом. Выходы элементов И группы 4 -j соединены с входами элемента ИЛИ 5-|, выход которого соединен с (( + 1)-м выходом сумматора. f-й выход m -го многопорогового элемента 1 -м, имеющий порог i, соединен с входом элемента ИЛИ 5 - (€ (м - 1) - 1). Входы элемента И 3 при одинаковой разрядности входных унитарных кодов соединены с ( - 1)-м вькодом многопорогового элемента 1 - ( ,, имеющим порог ( f - 1), и первым выходом многопорогового элемента 1 - (), имеющим порог 1, а выход - с (-1)-м выходом сумматора. При различной разрядности входных унитарных кодов порядок соединения входов элемента И 3 с выходами многопороговых элементов соответствует описанному для элементов И групп 4. Г-й выход многопорогового элемента 1 - К при одинаковой разрядности входных унитарных кодов соединен с 3-м выходом сумматора. Предлагаемый сумматор унитарных кодов работает следующим образом .На t групп входов сумматора, соответствующих t операндам, поступают входные унитарные кодыХ Хо , X,, ..., Xjj,, . Унитарный код числа N имеет единицу в разряде У.J. и нули в остальных разрядах. В соответствии в этим на одном из входов каждой группы сумматора, соответствующих каждому из операндов, имеется единичньш потенциал, а на остальных входах нулевые. Пусть единичные потенциалы имеются на . входах Х ,. где с 1, ..., 0, т.е. все операнды равны 0. Это вызывает единичные потенциалы на всех выходах многопорогового элемента 1-1, выход с порогом t которого является нулевым выходом сумматора. Таким образом, единичный потен1.щал имеется только на нулевом выходе сумматора унитарных кодов. Пусть единичные потенциалы имеются только на входах ,, где с 1, ..., f, т.е. все операнды одинако.вой разрядности и равны (К - 1). Это вызовет появление единичных по3 . тенциалов на всех вькодах многопорогового элемента 1 - К , выход с порогом f которого является О -м выходом сумматора. Таким образом, единичньш пoтeнu aл будет только на 3 -м выходе сумматора унитарных кодов. Пусть единичные потенциалы имеют ся на входе X, и входах «V , где i 1, ..., (1-1, О + 1, ..., t. Это вызовет появление единичных потенциалов на выходах многопорогового элемента 1-1 с порогами от 1 до f - 1, а также на первом выходе многопорогового элемента 1-2, имеющего порог 1. в результате на обеих входа;, элемента П 2 и на его вы ходе, являющемся первьм выходом сумматора, будуг единичные потенциа лы, а на остальных выходах сумматора - нулевые. Пусть единичные потенциалы имеют ся на входе X -2 входах XK., , где i 1, . о., U - 1, U + 1, , .. , Это вызовет единичные потенциалы на выходах многопорогового элемента (1 -К) с порогами от 1 до - 1 и на первом выходе многопорогового 14 элемента 1 - (к- 1). В результате на обоих входах элемента И 3 и на его выходе, являющемся ( 3-1)-м выходом сумматора унитарных кодов, будут единичные потенциалы,а на остальных нулевые. Пусть единичные потенциалы поданы (7О на входы Xj , X 1 , ..., X jg сумматора. Это вызывает на выходах многопо™ рогового элемента ,1 - i ( -i 1,.,., К) с порогами, не превышающими ir .. где и - число единичных потенщ1.а.11сгна входах ХР ( с 1, ..., f), появление единичных потенциалов, поступающие на входы элементов И групп 4. Причем единичные потенциалы бу.т;ут на всех входах только одного эламе;-.та И, а именно того, на входах котсрого реализуются все комбинации разрядов операндов типа d, + + cf g 3 , что вызывает на его выходе, и ( 3 + 1) -м выходе сумматора едиш-1ч™ ный потенциал. На входах всех остальных элементов И групп 4 будет не менее одного нулевого потенциала, что вызовет нулевые потенциалы на их выходах и всех остальньк выходах суньгатора унитарных кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом @ | 1981 |

|

SU1027729A1 |

| Многопороговый логический элемент | 1984 |

|

SU1262722A1 |

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Устройство для умножения по модулю К | 1989 |

|

SU1691834A1 |

| Устройство для контроля параллельного двоичного кода по модулю К | 1986 |

|

SU1425676A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1993 |

|

RU2110886C1 |

| Сумматор по модулю К | 1989 |

|

SU1711148A1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2023 |

|

RU2809741C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

СУММАТОР УНИТАРНЫХ КОДОВ, содержащий элементы И и ИЛИ, группы элементов И, причем выход t -го элемента ИЛИ (i 1,...,J- 3, J максимальное значение группы) соединен с

| Устройство для суммирования ОдНОРАзРядНыХ дВОичНыХ чиСЕл | 1979 |

|

SU817700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования @ одноразрядных двоичных чисел | 1981 |

|

SU1068932A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1982-06-15—Подача