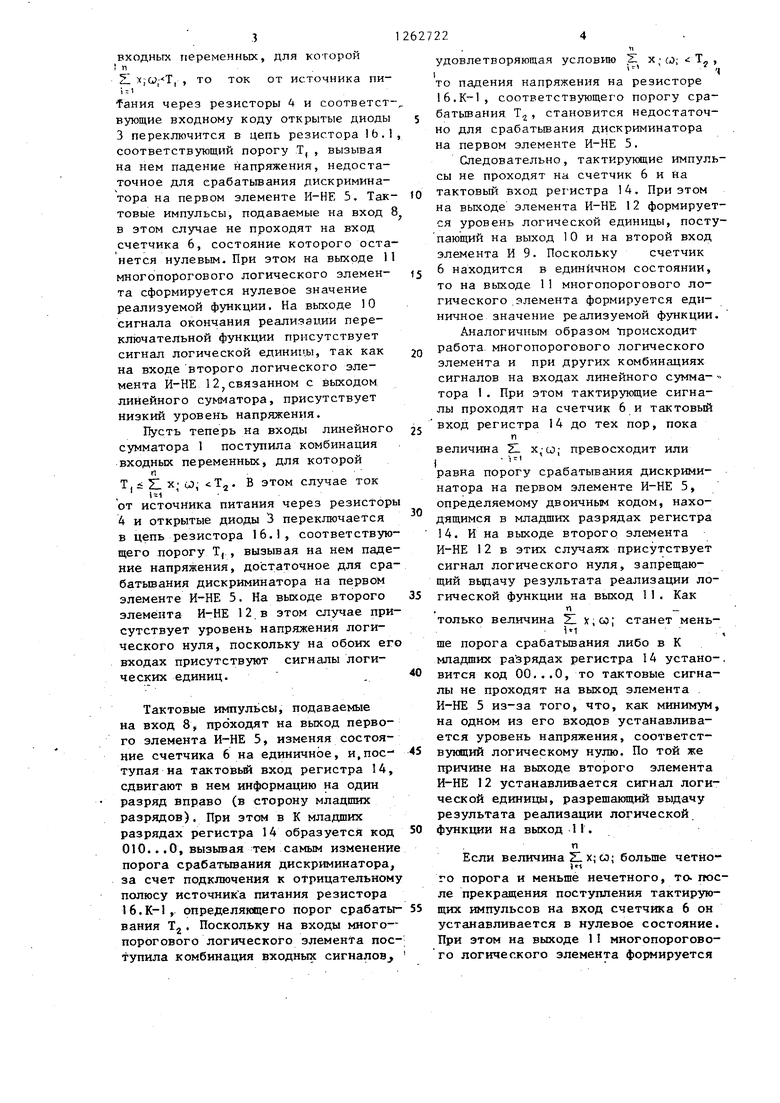

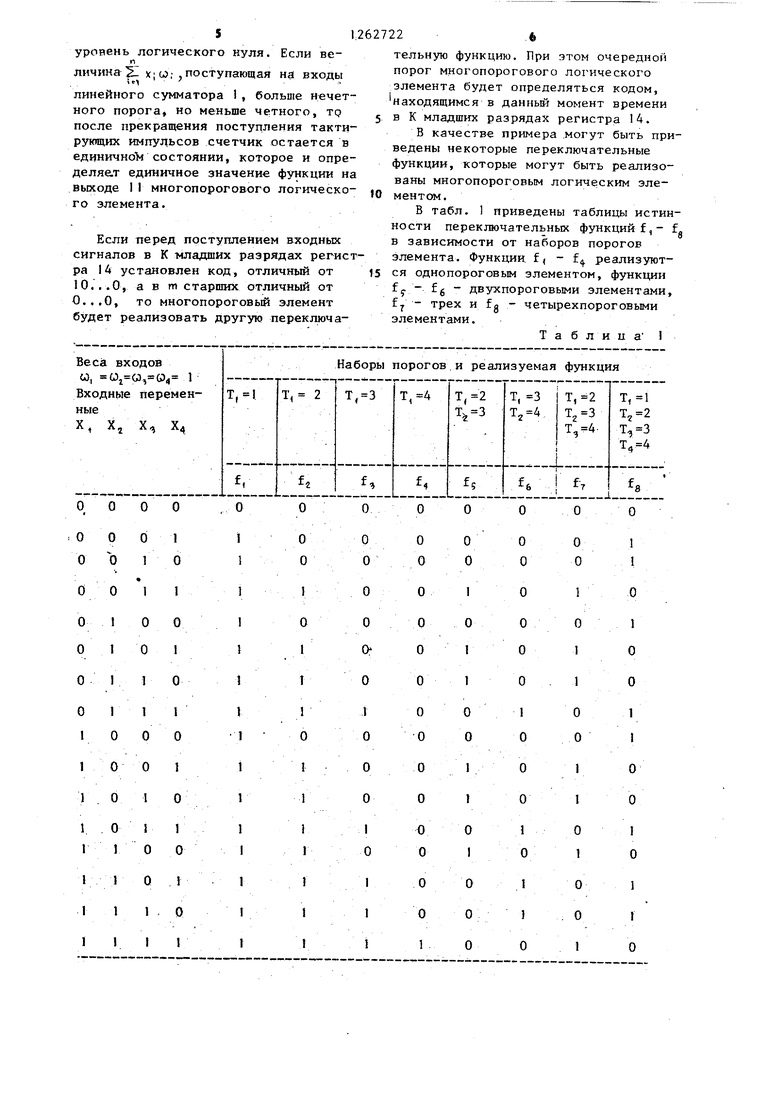

Изобретение относится к ргмпульсной технике, в частности к многопороговым логи-че/ским элементам, и может быть использовано в цифровых устройствах переработки инфop aции. Целью изобретения является расширение функциональньпс возможностей а именно- увеличение числа реализу мых переключательных функций. На чертеже представлена схема многопорогового. логического элемента. Многонороговый логический элемент содержит линейньй сумматор 1, состоящий из входных диодов 2, первые выводы каждого из которых соединены с соответствующими входами линейного сумматора, которые подключены к входам устройства, а вторые подключены к одноименным первым вьгоодам -соответствующих разделитель ных диодов 3 и к первым выводам соответствующих первьгх весовых резист ров 4, вторые вьшоды которых соедин ны с шиной источника питания, вторы выводы разделительных диодов соеди нены с выходом линейного с мматора; выход линейного сумматора подключен к первому входу первого элемента И-НЕ 5, выход которого соединен со счетным входом одноразрядного счетчика 6, а второй и третий входы пер вого элемента 5 соединены соответственно с входом 7 тактирующих импульсов и входом 8 управления началом реализации переключательной функции, выход .одноразрядного счетчика подключен к первому входу элемента И 9, второй вход которого сое динен с выходом 10 признака окончания реализации переключательной фун ции, выход элемента И 9 соед1-шен с выходом 11 устройства. Устройство содержит второй элемент И-НЕ 12, элемент ШШ 13, К+Мразрядньм регистр 14 сдвига и К инверторов 15, выходы которых соедине ны с первыми вьшодами соответствующих вторых весовых резисторов 16, вторые вьшоды которых подклзочены к первому входу первого элемента И-НЕ и к первому входу второго элемента И-НЕ 12, вьЕход которого соединен с вторым 13ХОДОМ элемента И 9, а второ вход подключен к выходу элемента ИЛИ 13 и к четвертому входу первого элемента И-НЕ, входы элемента ИЛИ с единены с входами соответствующих инверторов и подключены к выходам соответствующих К младших разрядов регистра 14 сдвига, К+М входов которого соединены с входами устройства, тактовый вход регистра 14 подключен к выходу первого элемента И-НЕ 5, а Fixoд 17 предварительной записи подключен к входу предварительной записи всего устройства. Многопороговьй логический элемент работает следующим образом. Перед подачей входных сигналов на входы линейного сумматора 1 производится установка одноразрядного счетчика 6 в нулевое состояние и запись в регистр 4 информации путем : подачи двоичного кода на его входы и сигнала записи на вход 17. Двоичный код записьшается в регистр 14, определяет количество и величиньг порогов у многопорогового логического элемента. Двоичный код 10...О, записанньй в К младших разрядах регистра 14, обуславливает появление единичного сигнала на К-м выходе регистра 4 и подключение к отрицательному полюсу источника питания весового резистора 16. К, определяющего порог срабатывания Т, ; код 010...О, записанный в К младших разрядах регистра 14, вызьшает подключение резистора 6. К-1, соответствующего порогу Т((). Двоичный код ПО...О, записанньй в К младщих разрядах регистра 14, вызьюает подключение к отрицательному полюсу источника питания параллельно включенных резисторов 1б.К и 16.К-1, соответствующих порогам Т, и Т, что эквивалентно порогу многопорогового логйческого элемента Т- Т + Tg.После занесения информации в регистр 14 на входы линейного суммато-. ра поступают входные сигналы, которые в произвольных комбинациях запирают входные диоды 2. Сигналы,признаков окончания реализации переключательных функций многопороговыми логическими элементами, связанными с входами линейного сумматора 1 рассматриваемого элемента, поступают на вход 7, единичный сигнал на котором означает, что все входные переменные на входах линейного сумматора сформированы. Положим, что в младшие разряды регистра 14 занесен код 10...О, а в старшие - код 0...0. Если на входах линейного сумматора i присутствует комбинация входных переменных, для которой S- x;( , ТО ТОК ОТ источника пиfaния через резисторы 4 и соответст вующие входному коду открытые диоды 3переключится в цепь резистора Ib. соответствующий порогу Т, , вызывая на нем падение напряжения, недостаточное для срабатьшания дискриминатора на первом элементе И-НЕ 5. Так товые импульсы, подаваемые на вход в этом случае не проходят на вход счетчика 6, состояние которого оста нется нулевым. При этом на выходе 1 многопорогового логического элемента сформируется нулевое значение реализуемой функции. На выходе 10 сигнала окончания реализации переключательной функции присутствует сигнал логической единицы, так как на входевторого логического элемента И-НЕ 12 связанном с выходом линейного сумматора, присутствует низкий уровень напряжения. Пусть теперь на входы линейного сумматора 1 поступила комбинация входных переменных, для которой п, T|i Z1 х; со, Т. В этом случае ток от источника питания через резистор 4и открытые диоды 3 переключается в цепь резистора 16.1, соответствую щего порогу Т, , вызывая на нем паде ние напряжения, достаточное для сра батывания дискриминатора на первом элементе И-НЕ 5. На выходе второго элемента И-НЕ 12 в этом случае при сутствует уровень напряжения логического нуля, поскольку на обоих ег входах присутствуют сигналы логических единиц. Тактовые импульсы, подаваемые на вход 8, проходят на выход первого элемента И-НЕ 5, изменяя состояние счетчика 6 на единичное, и.поступая на тгжтоззый вход регистра 14, сдвигают в нем информацию на один разряд вправо (в сторону младших разрядов). При этом в К младших разрядах регистра 14 образуется код 010...0, вызывая тем самым изменени порога срабатывания дискриминатора, за счет подключения к отрицательном полюсу источника питания резистора 16.К-1, определяющего порог срабаты вания Tj. Поскольку на входы многопорогового Логического элемента пос тупила комбинация входных сигналов удовлетворяющая условию S х Q; Т,, ч то падения напряжения на резисторе 16,К-1, соответствующего порогу срабатьшания Т, становится недостаточно для срабатьшания дискриминатора на первом элементе И-НЕ 5. Следовательно, тактирующие импульсы не проходят На счетчик 6 и на тактовый вход регистра 14. При этом на выходе элемента И-НЕ 12 формируется уровень логической единицы, поступающий на выход 10 и на второй вход элемента И 9. Поскольку счетчик 6 находится в единичном состоянии, то на выходе 11 многопорогового логического .элемента формируется единичное значение реализуемой функции. Аналогичным образом происходит работа многопорогового логического элемента и при других комбинациях сигналов на входах линейного сумма- тора 1. При этом тактирующие сигналы проходят на счетчик 6 и тактовый вход регистра 14 до тех пор, пока п величина 21 х,-со; превосходит или равна порогу срабатывания дискриминатора на первом элементе И-НЕ 5, определяемому двоичным кодом, находящимся в младших разрядах регистра 14. И на выходе второго элемента И-НЕ 12 в этих случаях присутствует сигнал логического нуля, запрещающий вьдачу результата реализации логической функции на выход 11. Как ч только величина Z1 х.оз; станет меньше порога срабатьшания либо в К младших разрядах регистра 14 устано-, вится код 00...0, то тактовые сигналы не проходят на выход элемента . И-НЕ 5 из-за того, что, как минимум, на одном из его входов устанавливается уровень напряжения, соответствующий логическому нулю. По той же причине на выходе второго элемента И-НЕ 12 устанавливается сигнал логической единицы, разрешающий выдачу результата реализации логической функции на выход 11. п Если величина Z х;«: больше четно) го порога и меньше нечетного, то- после прекращения поступления тактирующих импульсов на вход счетчика 6 он устанавливается в нулевое состояние. Бри этом на выходе 11 многопорогово- го логического элемента формируется Если веуровень логического куля личина )(W; .поступающая на входы , линейного сумматора 1, больше нечет кого порога но меньше четного, TQ после прекращений поступления тактирующих импульсов счетчик остается в единично состоянии, которое и определяет единичное значение функции на вькоде 11 многопорогового логического элемента. Если перед поступлением входньк сигналов в К младших разрядах регист ра 14 установлен код, отличный от 10,..О, а в m старших отличный от О...О, то многопороговый элемент будет реализовать другую переключательную функцию. При этом очередной порог многопорогового логического элемента будет определяться кодом, находящимся в данный момент времени в К младших разрядах регистра 14. В качестве примера .могут быть приведены некоторые переключательные функции, которые могут быть реализованы многопороговым логическим элементом. В табл. 1 приведены таблицы истинности переключательных функций f,- f в зависимости от наборов порогов элемента. Функции, f, - f реализуются однопороговым элементом, функции fj. - fg - двухпороговыми элементами, f - трех и fg - четырехпороговыми элементами. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1983 |

|

SU1112564A2 |

| Многопороговый логический элемент | 1980 |

|

SU936427A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Функциональный генератор напряжения | 1976 |

|

SU610129A1 |

| Устройство для сортировки информации | 1986 |

|

SU1386989A2 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

Изобретение может быть использ.овано в цифровых устройствах переработки информации. Цель изобретения расширение ф- нкциональных возможностей. Устройство содержит линейный сумматор 1, элемент И-НЕ 5, одноразрядный счетчик 6, элемент И 9 и К инверторов -15. Введение К + М-разрядного регистра 14 сдвига, элемента И-НЕ 12 и элемента ИЛИ 13 и образование новых связей между элементами устройства позволяет увеличить число реализуемых переключательньк функций. ,2 табл. 1 ил.

1 о

О О

О

I

1 О О

Q

1

о 1

1 I

о о

о о

1 о

о о

1

о о

о о

о о

о 1

I о

1 о

о I

G

о о о

о о о

1

о о 1

1 I о

} о

712627228

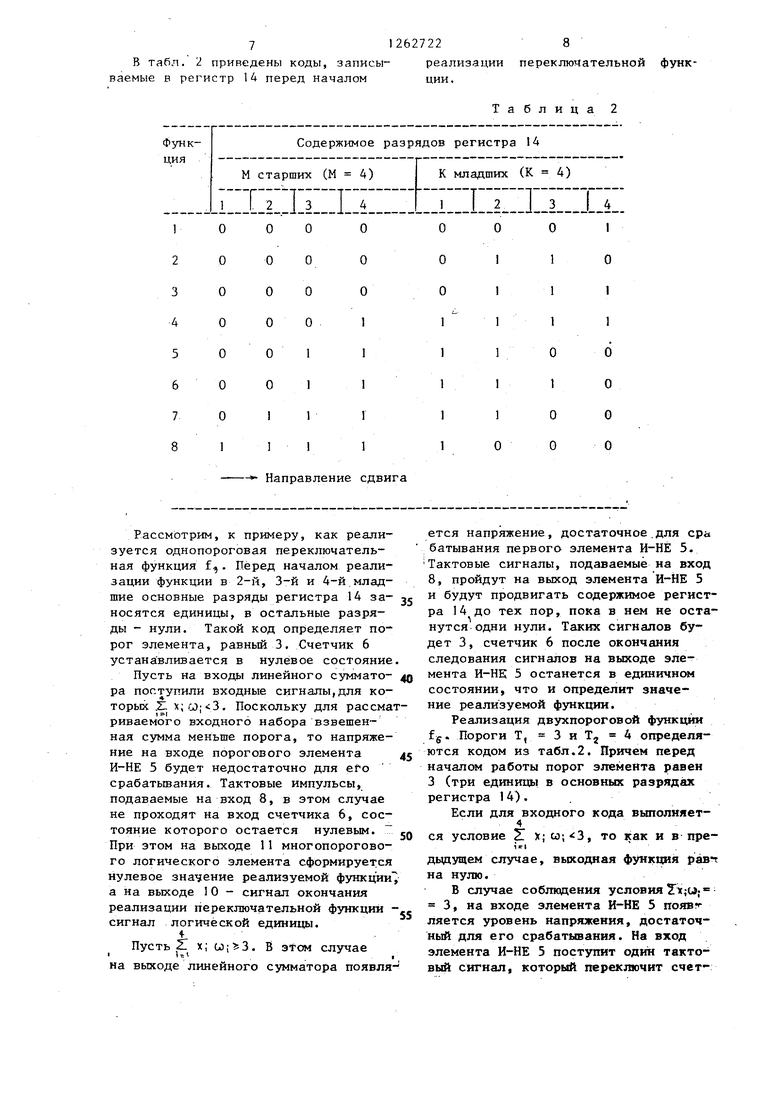

В табл. 2 приведены коды, записы- реализации переключательной функваемые в регистр 14 перед началом ции. Рассмотрим, к примеру, как реализуется однопороговая переключательная функция f,. Перед началом реализации функции в 2-й, 3-й и 4-й.младшие основные разряды регистра 14 заносятся единицы, в остальные разряды - нули. Такой код определяет порог элемента, равный 3. Счетчик 6 устанавливается в нулевое состояние Пусть на входы линейного сумматора поступили входные сигналы,для которых .Z х;.:). Поскольку для рассма риваемого входного набора взвешенная сумма меньше порога, то напряжение на входе порогового элемента И-НЕ 5 будет недостаточно для еРо срабатьтания. Тактовые импульсы, подаваемые на вход 8, в этом случае не проходят на вход счетчика 6, состояние которого остается нулевым. При этом на выходе 11 многопорогового логического элемента сформируется нулевое значение реализуемой функции а на выходе 1 О - сигнал окончания реализации переключательной функции сигнал логической единицы. 1-. Пусть 21 х; (. В 3toM случае - - . на выходе линейного сумматора появля ется напряжение, достаточное.для ера батывания первого элемента И-НЁ 5. Тактовые сигналы, подаваемые иа вход 8, пройдут на выход элемента И-НЕ 5 и будут продвигать содержимое регистра I4 до тех пор, пока в нем не останутся одни нули. Таких сигналов будет 3, счетчик 6 после окончания следования сигналов на выходе элемента И-НЕ 5 останется в единичисм состоянии, что и определит значение реализуемой функции. Реализация двухпороговой функции fg Пороги Т, 3 и Tj 4 определяются кодом из табл.2. Причем перед началом работы порог элемента равен 3 (три единицы в основных разрядах регистра 14). Если для входного кода выполняет4ся условие Z X; , то как и в предьщущем случае, выходная функция равт на нулю. В случае соблюдения условия -x;U; 3, на входе элемента И-НЕ 5 появг ляется уровень напряжения, достаточный для его срабатывания. На вход элемента И-НЕ 5 поступит один тактовый сигнал, который переключит счетчик 6 в единичное состояние и сдвине Р1нформацию в регистре 14 на один раз ряд вправо. При этом все младшие раз ряды регистра 14 будут заполнены еди ницами, что приведет к установке нового порога Т„ 4. Поскольку в рассматриваемом случае 51x;fj; 3, то потенциала на входе первого элемента И-НЕ 5 недостаточно для его срабатывания и на выходе 11 формируется единичное значение функции. Пусть 51 v;W; 4. На входе элемента |U, И-НЕ 5 появляется высокий уровень напряжения, которьй обеспечивает его срабатывание. Тактовые сигналы, пода ваемые на вход 8, будут проходить на выход элемента И-НЕ 5, изменять состояние счетчика 6 и сдвигать информацию в регистре 10 до тех пор, пока в нем не останутся одни нули. Число таких сигналов будет равно шес ти. Следовательно, после прохождения тактовых сигналов триггер перек.лючит ся в нулевое состояние, что и опреде лит нулевое значение функции f g .. Аналогичным образом реализуются и другие переключательные функции. Формула изобретени О Многопороговый логический элемен содержаддай линейный сумматор, состо щий из входных диодов, первые вьшоды каждого из которых соединены с соответствующими входами линейного сумматора, которые подключены к входам устройства, а вторые подключены к одноименным первым вьгеодам соответствующих разделительных диодов и к первым вьшодам соответствующих пе вых весовых резисторов, вторые выво- ды которых соединены с шиной источника питания, вторые ньгооды разделительных диодов соединены с выходом линейного сумматора, выход линейного сумматора подключен к. первому входу первого элемента И-НЕ, выход которого соединен со счетным входом одноразрядного счетчика, а второй и третий входы первого элемента И-НЕ соединены соответственно с входом тактирующих импульсов и входом управления началом реализации переключательной функции, выход одноразрядного счетчика подключен к первому входу элемента И, второй вход которого соединен с выходом признака окончания реализации переключательной функции, выход элемента И соединен с выходом устройства, о т л и ч а Ющ и и с я тем, что, с целью расширения функциональных возможностей, в него введены второй элемент И-НЕ, элемент ИЛИ, К+М-разрядный регистр сдвига и К инверторов, выходы которых соединены с первыми выводами соответствующих вторьгх весовых резисторов , вторые выводы подключены к первому входу первого элемента И-НЕ и к первому входу второго элемента И-НЕ, выход которого соединен с вторым входом элемента И, а второй вход подключен к выходу элемента ИЛИ и к четвертому входу первого элемента И-НЕ, входы элемента ИЛИ соединены с входами соответствующих инверторов и подключены к выходам соответствующих К младших разрядов регистра сдвига, К+М входов которого соединены с входами устройства, тактовый вход регистра подключен к выходу первого элемента И-НЕ, а вход предварительной записи подключен к входу предварительной записи всего устройства.

| Многопороговый логический элемент | 1980 |

|

SU936427A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многопороговый логический элемент | 1983 |

|

SU1112564A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-07—Публикация

1984-11-06—Подача