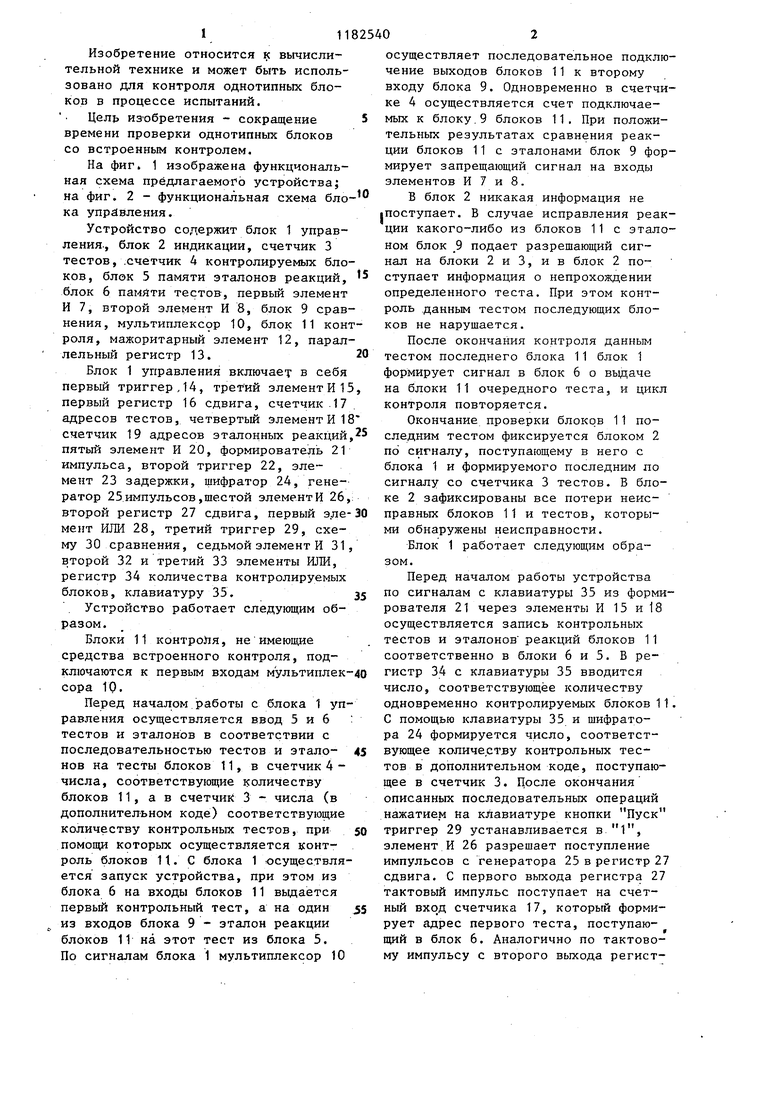

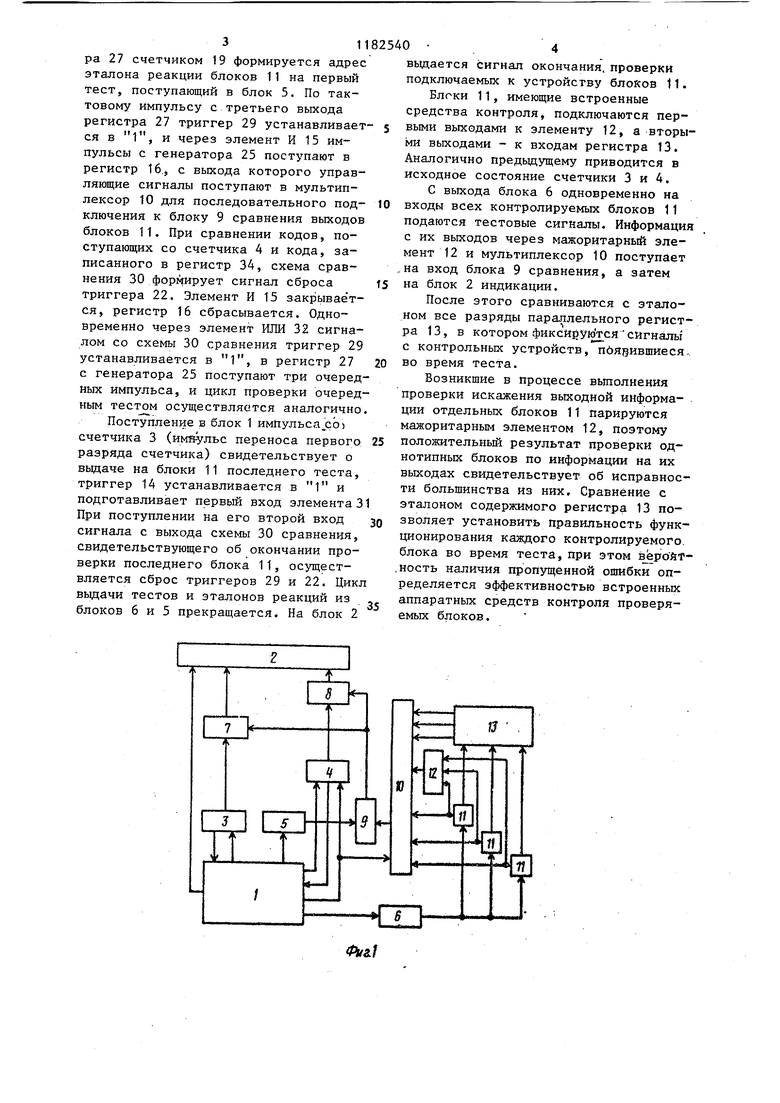

111 Изобретение относится к вычислительной технике и может быть использовано для контроля однотипных блоков в процессе испытаний. Цель изобретения - сокращение времени проверки однотипных блоков со встроенным контролем. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока управления. Устройство содержит блок 1 управления., блок 2 индикации, счетчик 3 тестов, .счетчик 4 контролируемых блоков, блок 5 памяти эталонов реакций, блок 6 памяти тестов, первый элемент И 7, второй элемент И 8, блок 9 сравнения, мультиплексор 10, блок 11 конт роля, мажоритарный элемент 12, параллельный регистр 13. Блок 1 управления включает в себя первый триггер,14, третий элементИ15 первый регистр 16 сдвига, счетчик .17 адресов тестов, четвертый элемент И 18 счетчик 19 адресов эталонных реакций пятый элемент И 20, формирователь 21 импульса, второй триггер 22, элемент 23 задержки, шифратор 24, генератор 2 5 импульсов, шее той элемент И 26, второй регистр 27 сдвига, первый элемент ИЛИ 28, третий триггер 29, схему 30 сравнения, седьмой элемент И 31 второй 32 и третий 33 элементы ИЛИ, регистр 34 количества контролируемых блоков, клавиатуру 35. Устройство работает следующим образом. Блоки 11 контроля, не имеющие средства встроенного контроля, подключаются к первым входам мультиплексора 10. Перед начал ом работы с блока 1 управления осуществляется ввод 5 и 6 тестов и эталонов в соответствии с последовательностью тестов и эталонов на тесты блоков 11, в счетчик 4числа, соответствующие количеству блоков 11, а в счетчий 3 - числа (в дополнительном коде) соответствующие количеству контрольных тестов, при помощи которых осуществляется контроль блоков 1t. С блока 1 осуществляется запуск устройства, при этом из блока 6 на входы блоков 11 выдается первый контрольный тест, а на один из входов блока 9 - эталон реакции блоков 11 на этот тест из блока 5. По сигналам блока 1 мультиплексор 10 0 осуществляет последовательное подключение выходов блоков 11 к второму входу блока 9. Одновременно в счетчике 4 осуществляется счет подключаемых к блоку.9 блоков 11. При положительных результатах сравнения реакции блоков 11 с эталонами блок 9 формирует запрещающий сигнал на входы элементов И 7 и 8. В блок 2 никакая информация не поступает. В случае исправления реакции какого-либо из блоков 11 с эталоном блок 9 подает разрешающий сигнал на блоки 2 и 3, и в блок 2 поступает информация о непрохождении определенного теста. При этом контроль данным тестом последующих блоков не нарушается. После окончания контроля данным тестом последнего блока 11 блок 1 формирует сигнал в блок 6 о выдаче на блоки 11 очередного теста, и цикл контроля повторяется. Окончание проверки блоков 1 1 последним тестом фиксируется блоком 2 по сигналу, поступающему в него с блока 1 и формируемого последним по сигналу со счетчика 3 тестов. Б блоке 2 зафиксированы все потери неисправных блоков 11 и тестов, которыми обнаружены неисправности. Блок 1 работает следующим образом. Перед началом работы устройства по сигналам с клавиатуры 35 из формирователя 21 через элементы И 15 и 18 осуществляется запись контрольных тестов и эталонов реакций блоков 11 соответственно в блоки 6 и 5. В регистр 34 с клавиатуры 35 вводится число, соответствующее количеству одновременно контролируемых блоков 11. С помощью клавиатуры 35 и шифратора 24 формируется число, соответствующее количеству контрольных тестов в дополнительном коде, поступающее в счетчик 3. Цосле окончания описанных последовательных операций нажатием иа клавиатуре кнопки Пуск триггер 29 устанавливается в 1, элемент И 26 разрешает поступление импульсов с генератора 25 в регистр 27 сдвига. С первого выхода регистра 27 тактовый импульс поступает на счетный вход счетчика 17, который формирует адрес первого теста, поступающий в блок 6. Аналогично по тактовому импульсу с второго выхода регистpa 27 счетчиком 19 формируется адрес эталона реакции блоков 11 на первый тест, поступающий в блок 5. По тактовому импульсу с третьего выхода регистра 27 триггер 29 устанавливается в 1, и через элемент И 15 импульсы с генератора 25 поступают в регистр 16., с выхода которого управляющие сигналы поступают в мультиплексор 10 для последовательного подключения к блоку 9 сравнения выходов блоков 11. При сравнении кодов, поступающих со счетчика 4 и кода, записанного в регистр 34, схема сравнения 30 формирует сигнал сброса триггера 22. Элемент И 15 закрывается, регистр 16 сбрасывается. Одновременно через элемент ИЛИ 32 сигналом со схемы 30 сравнения триггер 29 устанавливается в 1, в регистр 27 с генератора 25 поступают три очередных импульса, и цикл проверки очередным тестом осуществляется аналогично

Поступление в блок 1 имйульса.со) счетчика 3 (имйульс переноса первого разряда счетчика) свидетельствует о выдаче на блоки 11 последнего теста, триггер 14 устанавливается в 1 и подготавливает первый вход элемента 3 При поступлении на его второй вход сигнала с выхода схемы 30 сравнения, свидетельствующего об окончании проверки последнего блока 11, осуществляется сброс триггеров 29 и 22. Цикл выдачи тестов и эталонов реакций из блоков 6 и 5 прекращается. На блок 2

выдается сигнал окончания, проверки подключаемых к устройству блоков 11.

Блоки 11, имеющие встроенные средства контроля, подключаются первыми выходами к элементу 12, а вторыми выходами - к входам регистра 13. Аналогично предыдущему приводится в исходное состояние счетчики 3 и 4.

С выхода блока 6 одновременно на входы всех контролируемых блоков 11 подаются тестовые сигналы. Информация с их выходов через мажоритарный элемент 12 и мультиплексор 10 поступает ,на вход блока 9 сравнения, а затем на блок 2 индикации.

После этого сравниваются с эталоном все разряды параллельного регистра 13, в котором фиксй5У1отсясигналь с контрольных устройств, пбядившиеся.. во время теста.

Возникшие в процессе вьтолнения проверки искажения выходной информации отдельных блоков 11 парируются мажоритарным элементом 12, поэтому положительный результат проверки однотипных блоков по информации на их выходах свидетельствует об исправности большинства из них. Сравнение с эталоном содержимого регистра 13 позволяет установить правильность функционирования каждого контролируемого, блока во время теста, при этом веройт.ность наличия пропущенной ошибки определяется эффективностью встроенных аппаратных средств контроля проверяемых блоков.

.4&T

/f(bm)S/t.4

.G

5.S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1980 |

|

SU943733A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Система для контроля сложных релейных распределителей | 1987 |

|

SU1522209A2 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ, содержащее блок управления , первый выход которого соединен с первым входом блока индикации, первый вход и второй выход подключены соответственно к выходу переноса первого разряда и счетному входу счетчика тестов, выход которого подключен к первому входу первого элемента И, соединенного выходом с вторым входом блока индикации,второй вход первого элемента И соединен с вторым входом второго элемента И и выходом блока сравнения, первый вход которого подключен к выходу блока памяти эталонов, соединенного . входом с третьим выходом блока уп- . равления, четвертый выход которого подсоединен к установочному входу счетчика контролируемых блоков, подключенного первым выходом к первому входу второго элемента И,, выход которого соединен с третьим входом блока индикации,- второй выход счетчика контролируемых блоков подключен к второму входу блока управления, пятый выход которого подсоединен к счетному входу счетчика контролируеMbtx блоков и управляющему входу ;Йультиплексора,выход которого под-i. ключен к второму входу блока сравнения, шестой выход блока управления соединен с входом блока памяти тестов , выход которого соединен с выхосл дом устройстваj отличавдщеес с я тем, что, с целью сокращения времени проверки однотипных блоков с встроенным контролем, в устройство введены мажоритарный элемент и регистр, входы которого соединены с первыми входами устройства, вторые 00 входы которого подключены к первым ю информационным входам мультиплексоQ1 ра и входам мажоритарного элемента, «lik выход которого соединен с вторым информационным входом мультиплексора, третьи информационные входы которого соединены с выходами регистра.

HSjf.S

Уиз.ё

| УСТАНОВКА ДЛЯ ПЕРЕМЕЩЕНИЯ И РЕЗКИ ЗАГОТОВОК ДРЕНАЖНЫХ ТРУБ | 0 |

|

SU300331A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство ССГ.т | |||

| Устройство для контроля цифровых блоков | 1980 |

|

SU943733A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1983-12-26—Подача