.. 1 .

Изобретение относится к вычислительной технике, может быть использовано в системе контроля, обеспечивая увеличение достоверности и сокращение времени проверки партий однотипных блоков.

Известно устройство, содержащее блок памяти тестов, блок управления, блок индикации, блок сравнения, соединенный с блоком индикации, выходы блока управления соединены со входами блока памяти тестов и блока индикации D1

Недостатком устройства является (значительные аппаратурные затраты на проверку эталонной схемы, а также низкая производительность, обеспечивающая контроль не более двух схем.

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок индикации, блок управления, блок памяти эталонных реакций, блок сравнения, коммутатор, блок памяти тестов, причем первый выход блока памяти эталонных реакций подключен к первому входу блока сравнения, второй вход которого подключен к выходу коммутатора, вход которого подключен к первому выходу блока управления ХС

Недостатком известного устройства является невозможность контролировать N однотипных блоков. При серийном производстве характерно повторение одинаковых ошибок при монтаже однотипных блоков.

Целью изобретения является расширение области применения, за счет осуществления контроля Функционирования N однотипных блоков.

Поставленная цель достигается тем, что в устройство, содержащее блок индикации, счетчик тестов, блок памя|ти эталонных реакций, блок сравнения, коммутатор, блок управления, блок

Iпамяти тестов, причем первый выход

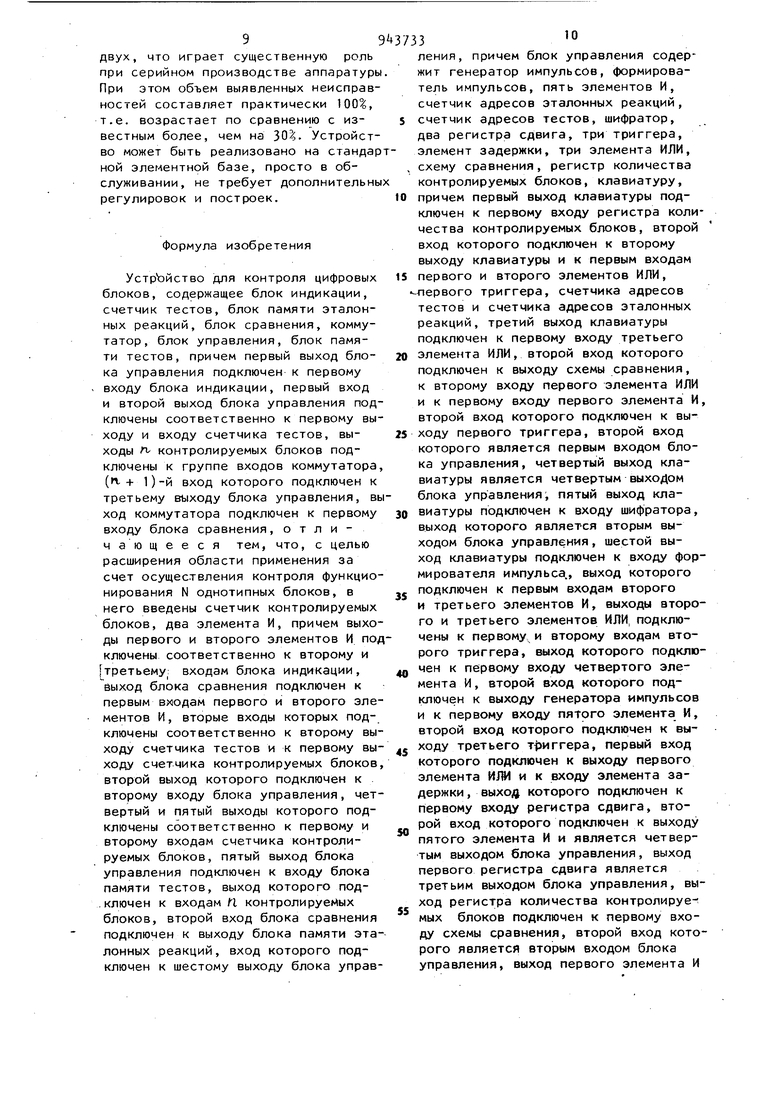

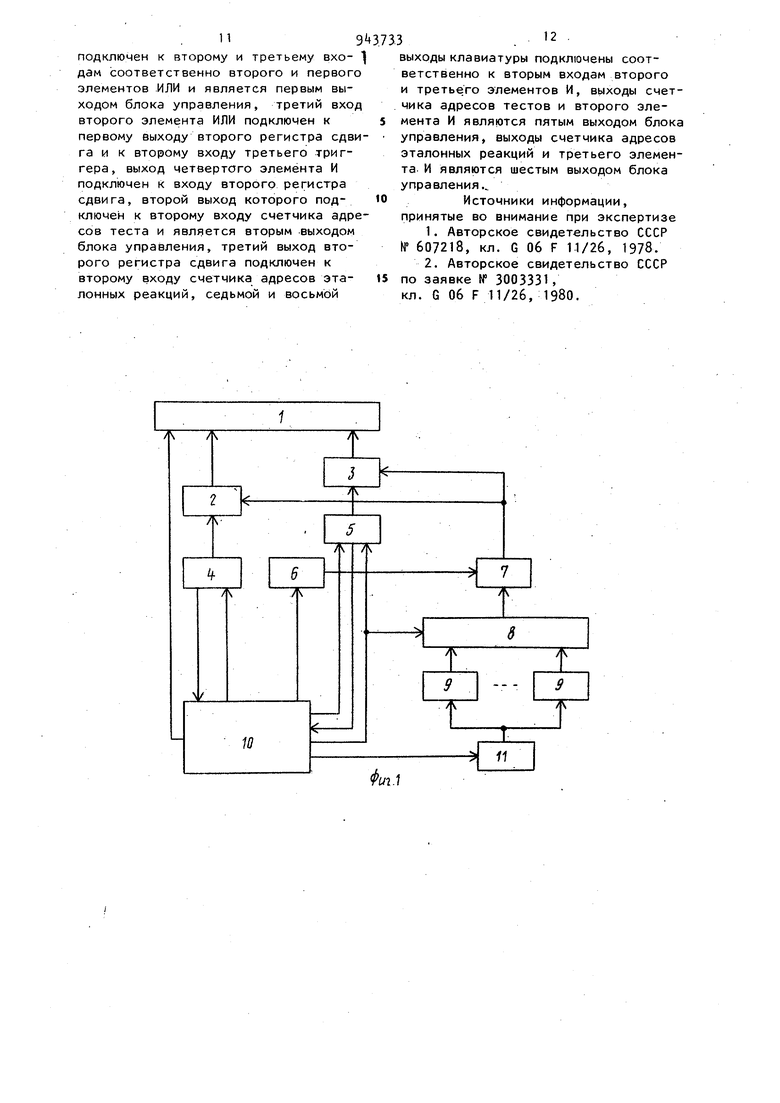

I блока управления подключен к первому входу блока индикации, первый вход и второй выход блока управления подклю ены соответственно к первому выходу и входу счетчика тестов, выходы П контролируемых блоков подключены к группе входов коммутатора, {П+1)-й вход которого подключен к третьему выходу блока управления, выход коммутатора подключен к первому входу блока сравнения, введены счетчик контролируемых блоков, два элемента И, причем выходы первого и второго элементов И подключены соответственно ко второму и третьему входам блока индикации, выход блока сравнения подключен к первым входам первого и второго элементов И, вторые входы которых подключены соответственно ко второму выходу счетчика тес тов к первому выходу счетчика контролируемых блоков, второй выход которого подключен ко второму входу блока управления, четвертый и пятый выходы которого соответственно к первому и второму входам счетчика контролируемых блоков, пятый выход блока управления подключен ко входу блока памяти тестов, выход которого подключен ко входам контролируемых блоков, второй вход блока сравнения подключен к выходу блока памяти эталонных реакций, вход которого подклю чен к шестому выходу блока управления, причем блок управления содержит генератор импульсов, формирователь импульсов, пять элементов И, счетчик адресов эталонных реакций, счетчик адресов тестов, шифратор, два регист ра сдвига, три триггера, элемент задержки, три элемента ИЛИ, схему срав нения, регистр количества контролируемых блоков, клавиатуру, причем первый выход клавиатуры подключен к первому входу регистра количества контролируемых блоков, второй вход которого подключен ко второму выходу клавиатуры и к первым входам первого и второго элементов ИЛИ, первого триггера, счетчика адресов тестов и счетчика адресов эталонных реакций, третий выход клавиатуры подключен к первому входу третьего элемента ИЛИ второй вход которого подключен к выходу схемы сравнения, ко второму входу первого элемента ИЛИ и к перво му входу первого элемента И, второй вход которогоподключен к выходу первого триггера, второй вход которо го является первым входом блока упра ления, четвертый выход клавиатуры является четвертым выходом блока управления., пятый выход клавиатуры подключен ко входу шифратора, выход которого является вторым выходом блока управления, шестой выход клавиатуры подключен ко входу формирователя импульсов, выход КОТОРОГО подключен к первым входам второго и третьего элементов И, выходы второго и третьего элементов ИЛИ подключены к первому и второму входам второго триггера , выход которого подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу генератора импульсов и к первому входу пятого элемента И, второй вход которого подключен к выходу третьего триггера, первый вход которого подключен к выходу первого элемента ИЛИ и к входу элемента задержки , выход которого подключен к первому входу регистра сдвига, второй вход которого подключен к выходу пятого элемента И и является четвертым выходом блока управления, выход первого регистра сдвига является третьим выходом блока управления, выход регистра количества контролируемых блоков подключен к первому входу схемы сравнения, второй вход которого является вторым входом блока управления, выход первого элемента И подключен ко второму и третьему входам соответственно второго и первого элементов ИЛИ и является первым выходом блока управления, третий вход второго элемента ИЛИ подключен к первому выходу второго регистра, сдвига и ко второму входу третьего триггера, выход четвертого элемента И подключен ко входу второго регистра сдвига, второй выход которого подключен к второму входу счетчика адресов теста и является вторым выходом блока угюавления, третий выход второго регистра сдвига подключен ко второму входу счетчика адресов эталонных реакций, седьмой и восьмой выходы клавиатуры подключены соответственно ко вторым входам второго и третьего элементов И, в)1ходы счетчика адресов тестов и второго элемента И являются пятым выходом блока управления, выходы счетчика, адресов эталонных реакций и третьего элемента И являются шестым выходом блока управления. На фиг. 1 приведена структурная схема устройства; на фиг. 2 (Структурная схема блока 10 упра ления. Устройство (фиг. 1) состоит из блока 1 индикации, элемента 2 И, эл мента 3 И, счетчика Ц тестов, счетчика 5 контролируемых блоков, блока 6 памяти эталонов реакций, блока 7 сравнения, коммутатора 8, нескольких контролируемых блоков 9, блока 10 управления, блока 11 памяти тестов. Блок управления (фиг. 2) состоит из триггера 12, логического элемента И 13, регистра сдвига 14, счетчика 15 адресов тестов, логического элемента И 16, счетчика 17 адресов эталонных реакций, логического элемента И 18, формирователя 19 импуль са, триггера 20, элемента задержки 21, шифратора 22, генератора импульсов 23, логического элемента И 2k, регистра сдвига 25, логического элемента ИЛИ 26, триггера 27, схемы сравнения 28, логического эле мента И 29, логических элементов 30 /и 31, регистра 32 количества контро лируемых блоков, клавиатуры 33. Блок 1 индикации предназначен дл регистрации результатов контроля пр веряемых блоков и их визуального отображения. Блок 1 в общем случае может быть построен на базе стандартных приборов. Так, например, в качестве блока 1 может быть испол зован телеграфный аппарат или алфавитно-цифровое печатающее устройство. Для удобства оператора в состав блока может быть введен индика тор на вакуумных люминесцентных или других индикаторных элементах. Элемент И 2 предназначен для ком мутации канала выдачи на индикатор номеров тестов, не прошедших через контролируемые блоки. Элемент И 3 предназначен для ком мутации канала выдачи на индикатор номеров неисправных контролируемых блоков. Счетчик тестов k представляет со бой суммирующий счетчик с одним вхо дом и предназначен для подсчета тес тов, выданных на контролируемые бло ки. Счетчик 5 контролируемых блоков представляет собой суммирующий счет чик с одним Входом и предназначен для счета контролируемых блоков. Блок б памяти эталонов реакций состоит из запоминающих элементов. 3 предназначенных для хранения и выдачи эталонов, предназначенных для хранения и выдачи эталонов реакций. Блок 7 сравнения представляет собой логическую схему совпадения, назначение которой состоит в выявлении факта совпадения или несовпадения реакции на тест, выдаваемой контролируемым блоком с ее эталонным значением, полученным из блока 6. Коммутатор 8 представляет сЬбой набор ключей на базе логических элементов И и ИЛИ, обеспечивающий выдачу на блок 7 сравнения реакций на контролирующие тесты с контролируемых блоков. Блоки 9 - контролируемые блоки. Блок 10 управления предназначен для выработки управляющих сигналов и синхронизации работы всего устройства. Блок 11 памяти тестов состоит из запоминающих элементов, предназначенных для хранения и выдачи тестов . на контролируемые блоки 9Устройство работает следующим образом. Перед началом работы с блока 10 управления осуществляется ввод в блоки 11 и 6 памяти тестов и эталонов реакций в соответствии с последовательностью тестов и эталонов реакций на тесты контролируемых блоков, в счетчик 5 контролируемых блокоа-числа, соответствующего количеству контролируемых блоков, а в счетчик Ц тестов-числа (в дополнительном коде), соответствующего количеству контрольных тестов при помощи которых осуществляется контроль блоков. С блока 10 управления осуществляется запуск устройства, при этом- из блока 11 памяти на входы контролируемых блоков выдается первый контрольный тест, а на один из входов блока 7 сравнения эталон реакции контролируемых блоков на этот тест из блока 6 памяти. По сигналам блока 10 управления коммутатор 8 осуществляет последовательное подключение выходов контролируемых блоков ко второму входу блока 7 сравнения. Одновременно в счетчике 5 осуществляется счет подключаемых к блоку 7 сравнения контролируемых блоков. При положительных результатах сравнения реакций контролируемых блоков с эталонами блок 7 формирует запрещающий сигнал на управляющих входах групп логических элементов И 2 и 3 В результате со счетчиков k и 7 в блок 1 индикации никакая информация не поступает. В случае несрав нения реакции какого-либо контролируемого блока о эталоном блок 7 срав нения подает разрешающий сигнал на группы логических элементов И 2, 3 и в блок 1 индикации поступает информация о непрохождении определенного теста.При этом контроль данным тестом последующих блоков не нарушается. После окончания контроля данным тестом последнего контролируемого блока блок 10 управления формирует сигнал в блок 11 памяти .о выдаче на контролируемые блоки 9 очередного теста и цикл контроля повторяется. Окончание проверки контролируемых блоков 9 последним тестом фиксируется блоком 1 индикации по сигналу, поступающему в него с блока 19 управления и формируемого последним по сигналу со счетчика Ц тестов. Таким образом, цикл контроля подключенных к устройству контролируемы блоков 9 всеми контрольными тестами завершен. В.блоке 1 индикацни зафик сированы все номера неисправных кон ролируемых блоков и тестов, которы ми обнаружены неисправности. Поиск конкретных .мест неисправностей в выявленных неисправных блоках осуществ ляется по диагностическим таблицам. Блок 10 управления работает следующим образом. Перед началом работы устройства по сигналам с клавиатуры 33 из формирователя 19 импульса через логичес кие элементы И 16 и 18 осуществляется запись контрольных тестов и эталонов реакций контролируемых блоков 9 соответственно в блоки 11 и 6 В регистр 32 с клавиатуры 33 вводится число, соответствующее количеству одновременно контролируемых блоков. С помощью клавиатуры 33 и шифратора 22 формируется число, соответствующее количеству контрольных тестов в дополнительном коде, поступающее в счетчик . После окончания описанных последо вательных операций нажатием на клавиатуре 33 кнопки Пуск триггер 27 устанавливается в 1, логический элемент И 2 разрешает поступление импульсов с генератора 23 в регистр сдвига 25. С первого выхода регистра 25 тактовый импульс поступает на |8 счетный вход счетчика 15, который формирует адрес первого теста, поступающий в блок 11 памяти тестов. Аналогично по тактовому импульсу со второго выхода регистра 25 счетчиком 17 формируется адрес эталона реакции контролируемых блоков на первый тест, поступающий в блок 6 памяти эталонов реакций. По тактовому импульсу с третьего выхода регистра 25 сдвига триггер 20 устанавливается в 1 и через логический элемент И 13 импульсы с генератора 23 начинают поступать в регистр k сдвига, с выхода которого управляющие сигналы выдаются на коммутатор 8 для последовательного подключения к блоку 7 сравнения выходов, контролируемых блоков 9 При сравнении кодов, поступающих со счетчика 5 контролируемых блоков и кода, записанного в регистре 32 количества контролируемых блоков, схема сравнения 28 формирует сигнал сброса триггера 20. Логический элемент И 1-3 закрывается, регистр 14 сдвига сбрасывается. Одновременно через логический элемент ИЛИ 30 сигналом со схемы сравнения 28 триггер ,27 устанавливается в 1, в регистр 25 сдвига с генератора 23 поступают три очередных импульса и цикл проверки контролируемых блоков 9 очередным тестом осуществляется аналогично. При поступлении в блок 10 управления сигнала со счетчика t тестов (импульс переноса первого разряда счетчика), свидетельствующего о выдаче на контролируемые блоки 9 последнего теста, триггер 12 устанавливается в 1 и подготавливает первый вход логического элемента И 29При поступлении на его .второй вход сигнала с выхода схемы сравнения. 28, свидетельствующего об окончании проверки последнего контролируемого блока, осуществляется сброс триггеров 27 и 20. Цикл выдачи тестов и эталонов реакций из блоков 6 и 11 памяти прекращаются. На блок 1 индикации выдается сигнал окончания проверки подключенных к устройству контролируемых блоков 9. Таким образом, предлагаемое устройство имеет большую производительность, так как позволяет осуществлять контроль функционирования одновременно N однотипных блоков вместо двух, что играет существенную роль при серийном производстве аппаратуры При этом объем выявленных неисправностей составляет практически 100, т.е. возрастает по сравнению с известным более, чем на 30. Устройство может быть реализовано на стандар ной элементной базе, просто в обслуживании, не требует дополнительны регулировок и построек. Формула изобретения УстрЪйство для контроля цифровых блоков, содержащее блок индикации, счетчик тестов, блок памяти эталонных реакций, блок сравнения, коммутатор, блок управления, блок памяти тестов, причем первый выход блока управления подключен к первому входу блока индикации, первый вход и второй выход блока управления под ключены соответственно к первому вы ходу и входу счетчика тестов, выходы контролируемых блоков подключены к группе входов коммутатора (п, + 1)-й вход которого подключен к третьему выходу блока управления, вы ход коммутатора подключен к первому входу блока сравнения, отличающееся тем, что, с целью расширения области применения за счет осуществления контроля функционирования N однотипных блоков, в него введены счетчик контролируемых блоков, два элемента И, причем выходы первого и второго элементов И под ключены соответственно к второму и третьему: входам блока индикации. ВЫХОД блока сравнения подключен к первым входам первого и второго элементов И, вторые входы которых подключены соответственно к второму выходу счетчика тестов и к первому выходу счетчика контролируемых блоков второй выход которого подключен к . второму входу блока управления, четвертый и пятый выходы которого подключены соответственно к первому и второму входам счетчика контролируемых блоков, пятый выход блока управления подключен к входу блока памяти тестов, выход которого под.ключен к входам П контролируемых блоков, второй вход блока сравнения подключен к выходу блока памяти эталонных реакций, вход которого подключен к шестому выходу блока управления, причем блок управления содержит генератор импульсов, формирователь импульсов, пять элементов И, счетчик адресов эталонных реакций, счетчик адресов тестов, шифратор, два регистра сдвига, три триггера, элемент задержки, три элемента ИЛИ, схему сравнения, регистр количества контролируемых блоков, клавиатуру, причем первый выход клавиатуры подключен к первому входу регистра количества контролируемых блоков, второй вход которого подключен к второму выходу клавиатуры и к первым входам первого и второго элементов ИЛИ, лервого триггера, счетчика адресов тестов и счетчика адресов эталонных реакций, третий выход клавиатуры подключен к первому входу третьего элемента ИЛИ, второй вход которого подключен к выходу схемы сравнения, к второму входу первого элемента ИЛИ и к первому входу первого элемента И, второй вход которого подключен к выходу первого триггера, второй вход которого является первым входом блока управления, четвертый выход клавиатуры является четвертым выходом блока управления, пятый выход клавиатуры подключен к входу шифратора, выход которого является вторым выходом блока управления, шестой выход клавиатуры подключен к входу формирователя импульса., выход которого подключен к первым входам второго и третьего элементов И, выходы второго и третьего элементов ИЛИ, подключены к первому и второму входам второго триггера, выход которого подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу генератора импульсов и к первому входу пятого элемента И, второй вход которого подключен к выходу третьего триггера, первый вход которого подключен к выходу первого элемента ИШ и к входу элемента задержки , выход которого подключен к первому входу регистра сдвига, второй вход которого подключен к выходу пятого элемента И и является четвертым выходом бгюка управления, выход первого регистра сдвига является третьим выходом блока управления, выход регистра количества контролируем мых блоков подключен к первому входу схемы сравнения, второй вход которого является вторым входом блока управления, выход первого элемента И

подключен к второму и третьему вхо- дам соответственно второго и первого элементов ИЛИ и является первым выходом блока управления, третий вход второго элемента ИЛИ подключен к первому выходу второго регистра сдвига и к второму входу третьего триггера , выход четвертого элемента И подключен к входу второго регистра сдвига, второй выход которого подключен к второму входу счетчика адресов теста и является вторым выходом блока управления, третий выход второго регистра сдвига подключен к второму входу счетчика адресов эталонных реакций, седьмой и восьмой

выходы клавиатуры подключены соответственно к вторым входам второго и третьего элементов И, выходы счетчика адресов тестов и второго элемента И являются пятым выходом блока управления, выходы счетчика адресов эталонных реакций и третьего элемента И являются шестым выходом блока управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 607218, кл. G 06 F 11/26, 1978.

2.Авторское свидетельство СССР по заявке № 3003331,

кл. G 06 F 11/26, 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1182540A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

Авторы

Даты

1982-07-15—Публикация

1980-12-26—Подача