мационные входы и вход разревюния приема числа индексного регистра соединены с информационными выходами коммутатора, второй управляющий выход которого соединен с входом разрешения приема числа в регистр текущего адреса, третий управляющий выход коммутатора соединен с входами, третьей группы блока элементов И,

выходы которого соединены с разрядными входами первой группы сумматора, разрядные пходы второй группы которого соединены с разрядными выходами индексного регистра, четвертый управляющий выход коммутатора соединен со входом установки в нулевое состояние блока формирования остатка адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1259262A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ НА ЦИЛИНДРИЧЕСКИХ МАГНИТНЫХ ДОМЕНАХ, содержащее индексный регистр, регистр базового адреса, сумматор, коммутатор, регистр текущего адреса, блок элементов И, причем разрядные выходы регистра базового адреса соединены с выходами первой группы блока элементов И, выходы сумматора соединены с информационными входами регистра текущего адреса, выходы которого являются адресными выходами устройства и соединены с информационными входами первой группы коммутатора, первый управляющий вход которого является первым переключающим входом устройства, отличающееся тем, что, с целью расширения области применения устройства путем реализации различных режимов адресации страниц и повьщ1ения его быстродействия, оно содержит блок формирования остатка адреса, счетчик физических адресов, элемент И-НЕ и элемент И, причем первый управляющий вход блока формирования остатка адреса является. первым входом синхронизации устройства и соединен со счетным входом счетчика физических адресов, вход установки в нулевое состояние которого является входом сброса устройства и соединен со вторым управлякмцим входом коммутатора, второй управляющий вход блока формирования остатка адреса является вторым переключающим входом устройства, первый вход, элемента И соединен с первым управляющим входом коммутатора, а второй вход элемента И - с входами установки в нулевое состояние индексного регистра и регистра текущего адреса, с входами второй группы блока элементов И и подключен к выходу элемента И-НЕ, входы которого соединены с разряднь1ми выходами счетчика физических адресов, информационными входами второй группы коммутатора и первым управляющим выходом коммутатора, третий управляющий вход ко00 ел торого подключен к первому управляющему входу блока формирования отстат00 ка адреса, четвертый управляющий вход коммутатора является вторым ел входом синхронизации устройства, пятый управляннций вход коммутатора соединен с выходом переноса блока формирования остатка адреса, первый и второй информационные выходы которого соединены с информационными входами третьей группы коммутатора, шестой управляющий вход которого соединен с выходом переноса счетчика физических адресов, седьмой управляющий вход коммутатора - с входом входного переноса сумматора и подключен к выходу элемента И, инфор

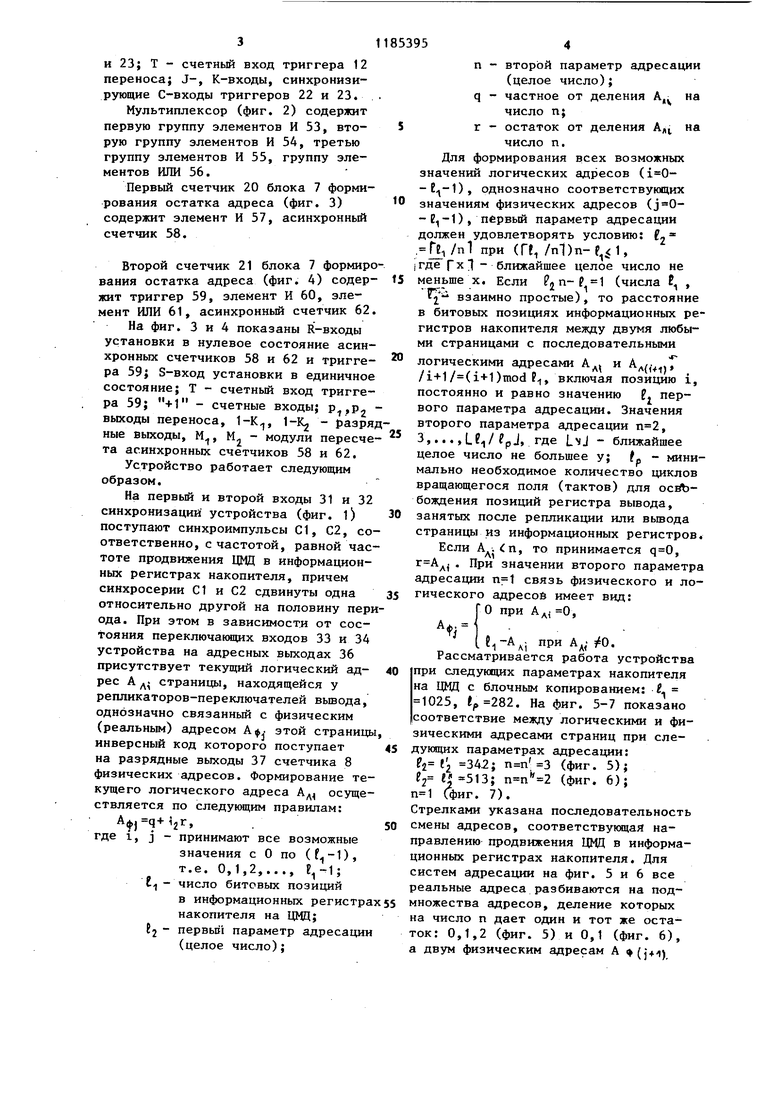

Изобретение относится к вычисли.тельной технике, в частности к устройствам для адресации памяти и может быть использовано в запоминающих устройствах на цилиндрических магни ных доменах (ЦМД), в которых для сокращения времени доступа и повышения скорости передачи данных из нако пителя при считывании -или записи нескольких страниц применяется их логическая адресация, для формирования текущего адреса в логической форме. Целью изобретения является расширение области применения устройства путем реализации различных режимов адресации страниц и повышение его быстродействия. На фиг. 1 представлена функциональная схема устройства; на фиг. 2мультиплексора, на фиг. 3 - то же, первого счетчика блока формирования остатка адреса; на фиг. 4 - то же, второго счетчика блока формиро;вания остатка адреса; на фиг. 5 - 7 соотношение между физическими и логическими -адресами страниц в накопителе на ЦНЦ. Устройство для адресации памяти на ЦМД (фиг. 1) содержит индексный регистр 1, регистр 2 базового адреса сумматор 3, коммутатор 4, регистр 5 текущего адреса, блок 6 элементов И блок 7 формирования остатка адреса, счетчик 8 физических адресов, элемент И-НЕ 9, элемент И 10. Коммутатор 4 (фиг. 1) содержит мультиплексор 11, триггер 12 переноса, элементы И 13-15, элементы ИЛИ I IS, элемент НЕ 19. Блок 7 формирования остатка адреса (фиг. 1) содержит первый счетчик 20, второй счетчик 21, триггеры 22 и 23, элементы И 24 и 25, элементы ИЛИ 26 и 27, элемент НЕ 28. На фиг. 1 показаны шина 29 с потенциалом логической единицы, шина 30 нулевого потенциала, первьй 31 и второй 32 входы синхронизации устройства, первый 33 и второй 34 переключающие входы устройства, вход 35 сброса устройства, адресные выходы 36 устройства, разрядные выходы 37 счетчика физических адресов, первьй 38 и второй 39 информационные выходы блока формирования остатка адреса, информационные выходы 40 коммутатора, второй 41, третий 42 и четвертьш 43 управляющие выходы коммутатора, выход 44 переноса блока формирования остатка адреса, выход 45 переноса счетчика физических адресов, вход 46 входного переноса сумматора, первый 47, второй 48 управляющие входы мультиплексора, выход 49 переноса первого счетчика, выход 50 переноса второго счетчика, вход 51 разрешения счета второго счетчика, вход 52 разрешения счета первого счетчика, На фиг, 1 показаны также А, А,..,,А , - разрядные входы первой группы сумматора 3; В, В, ..,, В гп-1 разрядные входы второй группы сумматора 3; Sg, S ,. .., S,,- выходы сумматора 3 (га - разрядность сумматора; О - старший, (m-i) - младший разряды); S - входы начальной установки в единичное состояние; R - входы начальной установки в ну- левое состояние триггеров 2, 22 и 23; Т - счетный вход триггера 12 переноса; J-, К-входы, синхронизирующие С-входы триггеров 22 и 23. Мультиплексор (фиг. 2) содержит первую группу элементов И 53, вторую группу элементов И 54, третью группу элементов И 55, группу элементов ИЛИ 56. Первый счетчик 20 блока 7 формирования остатка адреса (фиг. 3) содержит элемент И 57, асинхронный счетчик 58. Второй счетчик 21 блока 7 формиро вания остатка адреса (фиг. 4) содержит триггер 59, элемент И 60, элемент ИЛИ 61, асинхронньй счетчик 62. На фиг. 3 и 4 показаны R-входы установки в нулевое состояние асинхронных счетчиков 58 и 62 и триггера 59; S-вход установки в единичное состояние; Т - счетный вход триггера 59; +1 - счетные входы; Р,Р2 выходы переноса, 1-К, I-K - разря ные выходы, М, Mj - модули пересче та асинхронных счетчиков 58 и 62. Устройство работает следующим образом. На первьй и второй входы 31 и 32 синхронизации устройства (фиг. l) поступают синхроимпульсы С1, С2, со ответственно, с частотой, равной час тоте продвижения ЦНЦ в информационных регистрах накопителя, причем синхросерии С1 и С2 сдвинуты одна относительно другой на половину пер ода. При этом в зависимости от состояния переключающих входов 33 и 34 устройства на адресных вькодах 36 присутствует текущий логический адрее А д- страницы, находящейся у репликаторов-переключателей вьюода, однозначно связанный с физическим (реальным) адресом Аф- этой страниц инверсный код которого поступает на разрядные выходы 37 счетчика 8 физических адресов. Формирование текущего логического адреса А., осущемствляется по следующим правилам: A j q+i2r, . где 1, j - принимают все возможные значения с О по (), т.е. 0,1,2,..., С. - число битовых позиций в информационных регистра накопителя на ЦМЦ; 2 первый параметр адресации (целое число); второй параметр адресации (целое число); частное от деления А, на число п; остаток от деления на число п. Для формирования всех возможных значений логических адресов (), однозначно соответствующих значениям физических адресов (), первый параметр адресации должен удовлетворять условию: t . rei /nl при ( /n1)n- f 1, где pxl - ближайшее целое число не меньше X. Если (числа Р, , f взаимно простые), то расстояние в битовых позициях информационных регистров накопителя между двумя любыми страницами с последовательными логическими адресами Ад и Ад,., /i+1/(i+1)mod , включая позицию i, постоянно и равно значению f, Ч перЗначениявого параметра адресации, второго параметра адресации . 3,...,, где ближайшее целое число не большее у; р минимально необходимое количество циклов вращающегося поля (тактов) для осйЪбождения позиций регистра вывода, занятых после репликации или вьтода страницы из информационных регистров. Если Ад. п, то принимается , ( . При значении второго параметра адресации связь физического и логического адресов имеет вид: О при Ад(0, при Ад /0. Рассматривается работа устройства при следующих параметрах накопителя на ЦМД с блочным копированием: 1. 1025, . На фиг. 5-7 показано соответствие между логическими и физическими адресами страниц при следующих параметрах адресации: 2 ti 342; 3 (фиг. 5); е2 (фиг. 6); (фиг. 7). Стрелками указана последовательность смены адресов, соответствующая направлению продвижения ЦМЦ в информационных регистрах накопителя. Для систем адресации на фиг. 5 и 6 все реальные адреса разбиваются на подмножества адресов, деление которых на число п дает один и тот же остаток: 0,1,2 (фиг. 5) и 0,1 (фиг. 6), а двум физическим адресам А (j+i) и АФ-, /j + 1/(j + 1)mod 1 внутри этих подмножеств соответствуют логически адреса такие, что разность их значе ний равна п, причем значения первых логических адресов (0,1,2 - на фиг. 5; 0,1 - на фиг. 6) совпадают со значением соответствующего остат ка. Для системы адресаций при (фиг. 7) сумма физического и логиче кого адресов, кроме О, равна константе . С учетом изложенног в устройстве формируется текущий логический адрес. Сумматор 3 (фиг. 1) является т-разрядным параллельным комбинацио ным сумматором, где m - число разря дов, необходимое для представления числа без знака ( при Р, 102 Модуль пересчета счетчика 20 равен М Р 342 (счет с О по 341, сигнал переноса - на 342-ом синхроимпульсе С1). Модуль пересчета счет чика 21 равен M,j Р - 2 -1 170, чтобы сигнал переноса на выходе 50 (фиг. 1) возникал на 513-ом синхроимпульсе С1: при возникновении переноса на выходе 49 первого счетчика 20 и сигнала логического О на втором переключающем входе 34 устройства на выходе элемента И 24 возникает сигнал логической 1 и триггер 59 (фиг. 4) по входу 51 разрешения счета переводится в сост яние 1, на выходе 52 блокировки счета - уровень О и синхроимпульсы С1 не проходят на счетный вход счетчика 58 (фиг. 3). Поскольку сигнал логической 1 на единичном выходе триггера 59 воз никает после окончания действия сиг нала переноса на выходе 49 счетчика 20 (триггер 59 - двухступенчатый то счет начинается не с 342-го синхроимпульса С1 на входе 31, а с 343-го. Поэтому модуль пересчета равен не 171, а 170, т.е. Bi, М,+М . При появлении сигнала переноса на выходе 50 триггер 59 по R-входу устанавливается в О, на выходе 52 - уровень 1 (сигнал блокировки счета снимается и по сле дующему синхроимпульсу С1 начинаетс отсчет с О по 341 в счетчике 20, в то время как счетчик 21 находится в нулевом состоянии). Модуль пересчета счетчика 8 физических адресов равен (счет с О по 1024, сигнал переноса на 1025-ом синхроимпульсе С1). Перед началом работы устройства или.в определенный момент времени, например, после считывания страницы с адресным маркером, когда у репликаторов-переключателей вывода находится страница, адреса которой (физический и логический) должны быть равны О (абсолютный адрес), на вход 35 сброса устройства (фиг.1) подается логическая 1. При этом счетчик 8 физических адресов переводится -в нулевое состояние (на выходах 37 - инверсный код 11... 11), триггер 12 переноса по S-входу переводится в единичное состояние, сигналом логического О на выходе элемента И-НЕ 9 индексный регистр 1, регистр 5 текущего адреса по входам установки в нулевое состояние обнуляются, на выходах блока 6 элементов И - уровни логических О. Сигналом логической 1 с выхода элемента ИЛИ 16 переводятся в нулевое состояние счетчики 20 и 21, триггеры .22 и 23 - сигналом 1 с выхода элемента ИЛИ 26. Устройство гото-, во к работе. Сигнал 1 с входа 35 сброса снимается (с приходом первого синхроимпульса С1 на вход 31 триггер 12 по R-входу устанавливается в нулевое состояние). В зависимости от состояния переключающих входов 33, 34 и содержимого регистра 2 базового адреса осуществляются режимы выработки текущего логического адреса,представленные в таблице. При параметрах V 342 и п 3 адресация осуществляется в соответствии с фиг. 5. В регистр 2 базового адреса заносится число . Значение остатка присутствует на выходах 38, 39 триггеров 22 и 23 блока 7 формирования остатка адреса (фиг. 1.). На триггерах 22 и 23 образован счетчик с переменным модулем пересчета. При наличии на втором переключающем входе 34 уровня 1 модуль пересчета равен трем (счет с О по 2), так как на R-входе триггера 23 присутствует логический О. При наличии на втором переключающем входе 34 логического О (на выходе элемента ИПИ 26 ) триггер 23 постоянно находится в нулевом состоянии, пересчет на два осуществляется триггером 22. Если работа устройства начинается с нулевого (абсолютного адреса), то до прихода 342-го синхроимпульса С 1 на вход 31 значение остатка равно нулю. Формирование текущего логического адреса внутри зоны с одним и тем же остатком осуществл ется путем сложения логического адр са, образованного в предьщущем .такте, с константой п, находящейся в регистре 2 базового адреса, в сум маторе 3 и заносится в регистр 5 текущего адреса по синхроимпульсу С проходящему через элемент ИЛИ 18 на выход 41 коммутатора 4 и вход разрешения приема регистра 5. Логический адрес, полученньй в предьщущем такте, заносится в индексный регистр 1 по синхроимпульсу С2 на входе 32 через мультиплексор 11 с адресных выходов 36 устройства, причем на управляющем входе 48 мультиплексора 11 присутствует при этом логическая 1 (на выходе элемента И 13 - 1). Прием числа в индексный регистр 1 разрешен в то случае, если на одном из управляющих входов 46 - 48 мультиплексора 1 присутствует 1 (фиг. 2). До тех пор, пока счетчик 8 физических адресов находится в нулевом состоянии, на адресных выходах 36 присутствует нулевой логический адрес. С приходом первого синхроимпульса С1 на вход 31 содержимое счетчика 8 физичес1у х адресов становится отличным от нуля (физический адрес равен 1), триггер 12 переноса устанавливается в нулевое состояние, на выходе элемента И-НЕ логическая 1, на выходе 42 коммутатора - также уровень 1. Через элементы И 6 число п 3 проходит на входы сумматора 3 и складывается с содержимым индексного регистра 1, который до этого бьш обнулен. При этом на входе 46 входного переноса сумматора 3 постоянно сохраняется логический О (на входе 33 - О) Таким образом, формируется логический адрес, равный трем (фиг. 5), ко торый по синхроимпульсу С2 заноситс в индексный регистр 1. Аналогично формируются текущие логические адре са 6,9,,1020,1023 (остаток равен О). С приходом на вход 31 342 го синхроимпульса С1 на выходе 49 п реноса первого счетчика 20 формируется сигнал переноса (1), который через элементы И 25, ИЛИ 27 поступает на С-входы триггеров 22 и 23, формируется новое значение остатка 1. Через выход 44 блока 7 формирования остатка адреса сигнал переноса через элементы И 14, ИЛИ 17 коммутатора 4 поступает на Т-вход триггера 12 и запоминается в нем. При этом на управляющем входе 47 мультиплексора 11 уровень 1 и новое значение остатка с выходов 38 и 39 заносится в индексный регистр 1, На выходе 42 коммутатора 4 - сигнал О, на выходах элементов И 6 логические О, а на входе 41 разрешения приема в регистр 5 текущего адреса - 1, в регистр 5 заносится логический адрес, равный 1. С приходом следующего синхроимпульса С1 на вход 31 сигналом логической 1 на R-входе (выход элемента И 15) триггер 12 переноса вновь переводится в нулевое состояние. Формирование логических адресов 4, 7, 10,..., 1021, 1024 осуществляется также суммированием адреса, сформированного В предьщущем такте, с константой . Формирование остатка 2 и адресов 2, 5, 8, 11, ..., 1019, 1022 осуществляется аналогично. С приходом 1025-го синхроимпульса С 1 на вход 31 при содержимом счетчика 8 физических адресов, равном 1024, и логическом адресе 1022 наадресных выходах 36 счетчик 8 обнуляется (на выходах 37 - код 11.... 11). На выходе 45 переноса счетчика 8 возникает сигнал переноса .(1), поступающий через элемент ШШ 16 коммутатора 4 на выход 43 блока 7 формирования остатка адреса, и обнуляет счетчики 20, 21 и триггеры 22,23. Через элемент ИЛИ 17 сигнал переноса проходит на Т-вход триггера 12 переноса и запоминается в нем до прихода следующего синхроимпульса С1. Логическая 1 с выхода триггера 12 поступает на вход элемента И-НЕ 9, и лишь после этого на выходе элемента И-НЕ 9 появляется логический О, поступаюпшй на входы установки в нулевое состояние регистров 1 и 5. На адресных выходах 36 формируется нулевой (абсолютный) адрес. Таким образом, запоминание сигнала переноса с выхода 45 счетчика 8 и строби ование сигналом 1 с единичного выхода триггера 12 элемента И-НЕ 9 исключают ложное появление О на его выходе, которое может быть вызвано переходными процессами в счетчике 8, и непредусмотренное обнуление регистров 1 и 5. С приходом синхроимпульсов С1 процесс формирования текущих логичес ких .адресов протекает.аналогично опи санному. При параметрах .3 и п 2 адресация осуществляется в соответст вии с фиг. 6. В регистр 2 базового адреса заносится число п 2. На вто ром переключающем входе 34 - уровень О (формируемые значения остат ка О и 1). Формирование текущего логического адреса осуществляется аналогично его формированию при и p7 f2 однако образование значения остатка 1 и логического адреса, равного 1, происходит при поступле нии на вход 31 513-го синхроимпульса С1. В этом режиме сигнал переноса с выхода 49 счетчика 20 блока 7 формирования остатка адреса (фиг. 1) через, элемент И 24 поступает на вход 51 разрешения счета счетчика 2 (счет в счетчике 20 блокируется сигналом О на входе 52). Сигнал переноса на выходе 50 счетчика 21 возникает на 513-ом синхроимпульсе С1 (счетчик 21 обнуляется, на входе 52 разрешения счета счетчика появляется логическая 1). Сигнал переноса через элемент ИЛИ 27 поступает на С-вход триггера 22, перевод его в единичное состояние, и на выход 44 переноса блока 7 формировани остатка адреса. Таким образом, формируются значения остатка 1 и логического адреса 1. Далее образую ся текущие логические адреса 3,5, 7,....1021,1023. При поступлении 1025-го синхроимпульса 01 на вход 31 счетчик 8 физических адресов обнуляется, обра зуется нулевой адрес на выходах 36 аналогично режиму адресации при и 2. Vj. С приходом последующих синхроимпульсов С1 текущие логические адреса формируются аналогично описанному. При наличии сигнала логической на первом переключающем входе 33 и формирование текущего логичес кого адреса, кроме равного .О, осуществляется путем суммирования константы 1025, заносимой в регистр 2 базового адреса, с текущим физическим адресом, заносимым в индексный регистр 1, представленным в дополнительном коде (на входе 46 входного переноса сумматора 3 присутствует сигнал логической 1 с выхода элемента И 10, используется инверсный код физического адреса на выходах 37 счетчика 8). Результат сложения может быть только неотрицательным числом, поэтому знаковый разряд в сумматоре не нужен. При этом состояние второго переключающего входа 34 безразлично, так как прохождение сигнала переноса с выхода 44 блока 7 формирования остатка адреса через элемент И 14 на вход элемента ИЛИ 17 коммутатора 4 блокируется сигналом О на выходе элемента НЕ 19. Кроме того, в этом режиме до возникновения переноса на выходе 45 счетчика 8 возможна коммутация лишь группы выходов 37 коммутатора 4 на его выходы 40, поскольку на управляющих входах 47 и 48 - логические О (на выходах элементов И 14, ИЛИ 17 , триггер 12 переноса - в нулевом состоянии; на выходе элемента И 13 - О). Адресация осуществляется в соответствии с фиг. 7. С приходом первого синхроимпульса С1, если счетчик 8 -находился в нулевом состоянии,в счетчике 8 фиксируется текущий физический адрес 1.На выходе элемента И-НЕ 9 появляется уровень логической 1,сигналы установки в нулевое состояние регистров 1 и 5 снимаются. На выходы блока 6 элементов И проходит содержимое регистра 2 базового адреса () так как на выходе 42 коммутатора 4 - 1. Через мультиплексор 11 в индексный регистр 1 заносится инверсньй код физического адреса 11....10 (на управляющем входе мультиплексора 11 и входе 46 сумматора 3 - логическая 1) и выполняется вычитание физического адреса из константы 2. Полученный логический адрес 1024 заносится в регистр 5 текущего адреса, поступает на адресные выходы 36 и остается неизменным до прихода следующего синхроимпульса С1. Так же формируются текущие логические адре-. са 1023, 1022,...,1 (фиг. 7). С приходом 1025-го синхроимпульса С1 на вход 31 счетчик 8 физических адресов обнуляется, переводятся в нулевое сос.тояние регистры I и 3, формируется адрес О.

Режимы адресации страниц

О О 1

Во всех режимах адресации сигнал разрешения приема числа в регистр 5 текущего адреса на выходе Д1 коммутатора формируется либо по синхроимпульсу С I на входе 31 ,либо по сигналу на единичном выходе триггера 12 переноса.

п 3

0; 1; 2

о п 2

О; 1 Р 1023

t

9

5

/

20

w

50

Эв

п

/

И

34

2д

43

3

39

71

3

23

с /f

f5

к

4

гй

/б

35

J

J2

4ГЭ

47 45

;/

4

В

о

/;г-/

VT:

/77-/

:i

з/х:

i

1 т

Т

J5м

/2

г

L I

4

46

/1

X

5f

/«г

3/ГТ

Г -Г/ .

36 37393ff

/

u

ФигЛ

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования исполнительных адресов | 1980 |

|

SU888121A1 |

Авторы

Даты

1985-10-15—Публикация

1984-04-13—Подача