Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин и контроллеров с микропрограммным управлением.

Цель изобретения - расширение функциональных возможностей путем реализации режима ожидания и режима возврата по запросам на прерывание.

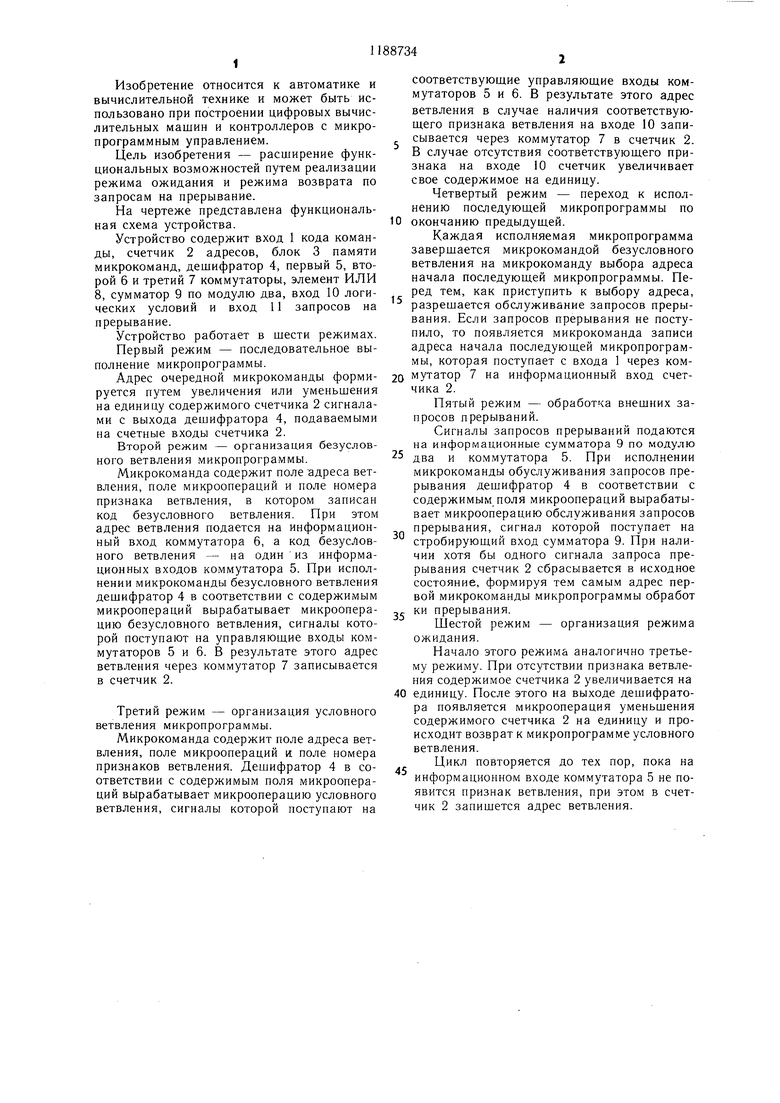

На чертеже представлена функциональная схема устройства.

Устройство содержит вход 1 кода команды, счетчик 2 адресов, блок 3 памяти микрокоманд, дешифратор 4, первый 5, второй 6 и третий 7 коммутаторы, элемент ИЛИ 8, сумматор 9 по модулю два, вход 10 логических условий и вход 11 запросов на прерывание.

Устройство работает в шести режимах.

Первый режим - последовательное выполнение микропрограммы.

Адрес очередной микрокоманды формируется путем увеличения или уменьшения на единицу содержимого счетчика 2 сигналами с выхода дешифратора 4, подаваемыми на счетные входы счетчика 2.

Второй режим - организация безусловного ветвления микропрограммы.

Микрокоманда содержит поле адреса ветвления, поле микроопераций и поле номера признака ветвления, в котором записан код безусловного ветвления. При этом адрес ветвления подается на информационный вход коммутатора 6, а код безусловного ветвления - на один из информационных входов коммутатора 5. При исполнении микрокоманды безусловного ветвления дешифратор 4 в соответствии с содержимым микроопераций вырабатывает микрооперацию безусловного ветвления, сигналы которой поступают на управляюшие входы коммутаторов 5 и 6. В результате этого адрес ветвления через коммутатор 7 записывается в счетчик 2.

Третий режим - организация условного ветвления микропрограммы.

Микрокоманда содержит поле адреса ветвления, поле микроопераций и поле номера признаков ветвления. Дешифратор 4 в соответствии с содержимым поля микроопераций вырабатывает микрооперацию условного ветвления, сигналы которой поступают на

соответствующие управляющие входы коммутаторов 5 и 6. В результате этого адрес ветвления в случае наличия соответствующего признака ветвления на входе 10 записывается через коммутатор 7 в счетчик 2. В случае отсутствия соответствующего признака на входе 10 счетчик увеличивает свое содержимое на единицу.

Четвертый режим - переход к исполнению последующей микропрограммы по окончанию предыдущей.

Каждая исполняемая микропрограмма заверщается микрокомандой безусловного ветвления на микрокоманду выбора адреса начала последующей микропрограммы. Перед тем, как приступить к выбору адреса, разрешается обслуживание запросов прерывания. Если запросов прерывания не поступило, то появляется микрокоманда записи адреса начала последующей микропрограммы, которая поступает с входа 1 через коммутатор 7 на информационный вход счетчика 2.

Пятый режим - обработка внешних запросов прерываний.

Сигналы запросов прерываний подаются на информационные сумматора 9 по модулю 5 два и коммутатора 5. При исполнении микрокоманды обуслуживания запросов прерывания дешифратор 4 в соответствии с содержимым поля микроопераций вырабатывает микрооперацию обслуживания запросов прерывания, сигнал которой поступает на стробируюший вход сумматора 9. При наличии хотя бы одного сигнала запроса прерывания счетчик 2 сбрасывается в исходное состояние, формируя тем самым адрес первой микрокоманды микропрограммы обработ , ки прерывания.

Шестой режим - организация режима ожидания.

Начало этого режима аналогично третьему режиму. При отсутствии признака ветвления содержимое счетчика 2 увеличивается на 0 единицу. После этого на выходе дешифратора появляется микрооперация уменьшения содержимого счетчика 2 на единицу и происходит возврат к микропрограмме условного ветвления.

Цикл повторяется до тех пор, пока на информационном входе коммутатора 5 не появится признак ветвления, при этом в счетчик 2 запишется адрес ветвления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для микропрограммногоупРАВлЕНия | 1979 |

|

SU822186A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1211724A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее счетчик адресов, три коммутатора, дешифратор и блок памяти микрокоманд, причем информационный вход первого коммутатора является входом логических условий устройства, управляющий вход первого коммутатора соединен с выходом кода анализируемых логических условий блока памяти микрокоманд, выход кода типа микрокоманды которого соединен с входом дещифратора, первый и второй выходы которого соединены соответственно с первым и вторым стробирующими входами первого коммутатора и с первым и вторым управляющими входами второго коммутатора, выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого является входом кода команды устройства, третий и четвертый выходы дешифратора соединены соответственно с первым управляющим входом третьего коммутатора и вычитающим входом счетчика адресов, выход которого соединен с адресным входом блока памяти микрокоманд, выход кода адреса которого соединен с информационным входом второго коммутатора, п выходов третьего коммутатора соединены с информационными входами счетчика адресов (где п - разрядность адреса блока памяти микрокоманд), (п+П-й выход третьего коммутатора соединен с входом управления режимом записи-счета счетчика адресов, отличающееся тем, что, с целью расширения функциональных возможностей путем реализации режима ожидания и режима возврата по запросам на прерывание, оно дополнительно содержит элемент ИЛИ и сумматор по i модулю два, причем пятый и шестой выходы дещифратора соединены соответственно с (Л первым входом элемента ИЛИ и стробирующим входом сумматора по модулю два, информационный вход которого является входом запросов на прерывание устройства, выход сумматора по модулю два соединен с входом сброса счетчика адресов, суммирующий вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с инверсным выходом первого коммутатора, прямой выход которого соединен с 00 00 вторым управляющим входом третьего коммутатора. со 4

| МИКРОПРОГРАЛ\АШОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 0 |

|

SU291201A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для микропрограммногоупРАВлЕНия | 1979 |

|

SU822186A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1983-12-07—Подача