второго элемента.и, второй вход которого объединен с выходом переполнения блока формирования адресов и подключен к прямому вьпсоду второго триггера, инверсньй выход которого подключен к второму входу третьего элемента И, вход управления образова нием кода блока формирования адреса подключен к входу элемента НЕ и вторым входам элементов И первой группы выходы элементов НЕ второй группы 1 4 подключены к первым входам элементов И второй группы, вторые входы которых объединены и подключены к выходу элемента НЕ, выходы элементов И второй группы подключены к первым входам элементов ИЛИ группы, к вторым входам которых подключены выходы элементов И первой группы, выходы элементов РШИ группы подключены к неуправляемому выходу блока формирования, адре са. ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Устройство для поиска данных | 1988 |

|

SU1564648A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для контроля перемещения подвижных объектов | 1989 |

|

SU1652965A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

ЦИФРОВОЙ ГЕНЕРАТОР ПЕРИОДИЧЕСКИХ СИГНАЛОВ, содержащий генератор импульсов, делитель частоты, регистр кода, счетчик, преобразователь код-аналог, причем выход гене- . ратора импульсов подключен к входу делителя частоты, вход предварительной .установки которого подключен к входу генератора, отличающ и и с я тем, что, с целью увеличения быстродействия, в него введены блок формирования адресов, схема сравнения и блок памяти, причем выход делителя частоты подключен к счетному входу счетчика, выход счетчика подключен к первому входу схемы сравнения, второй вход которой подключен к выходу старших разрядов ре истра кода, выход младшего разряда которого подключен к входу управления . образованием кода блока формирования адресов, выход схемы сравнения подключен к объединенным входу сброса счетчика и входу приращения блока формирования адресов, управляемый выход которого подключен к адресному входу блока памяти, выход которого подключен к входу регистра кода, неуправляемый выход блока формирования адресов подключен к входу данных преобразователя код-аналог, 1вход управления полярностью сигнала которого подключен к выходу переполнения блока формирования адресов, выход преобразователя код-аналог подключен к выходу генератора, причем блок формирования адресов содержит шесть элементов И, две группы элементов НЕ, группу элементов ИЛИ, элемент НЕ, два триггера, две группы элементов И, два ключа, реверсивный счетчик, причем выход реверсивного счетчика подключен поразрядно к входам элементов НЕ первой и второй групп, первым входам элементов И первой группы, входам первого элемента И и к управляемому выходу блока фор(Л мирования адреса, а выход первого элемента И подключен к входу первого ключа, выход которого подключен к входу S первого триггера, R-вход которого объединен с первыми входами второго и третьего элементов И и подключен к выходу четвертого элемента ;о И, входы которого подключены к выходам элементов НЕ первой группы, пря;О мой и инверсный выходы первого триг& гера подключены к первым входам пятого и шестого элементов И соответственно, вторые входы которых объединены и подключены к входу приращения блока формирования адреса, выход пятого элемента И подключен к входу прямого счета реверсивного счетчика, вход обратного счета которого подключен к выходу шестого элемента И, вйход третьего элемента И подключен к входу второго ключа, выход которого подключен к S входу второго триггера, R-вход которого подключен к выходу

1

Изобретение относится к автоматике и вычислительной технике и может найти применение в системах контроля электро- и радиоэлектронного оборудования, а также в моделирующих- стендах для генерации электрических сигналов, представляющих собой периодические функции времени различной формы.

Цель изобретения - увеличение быстродействия устройства при высокой точ кости воспроизведения заданных функций времени.

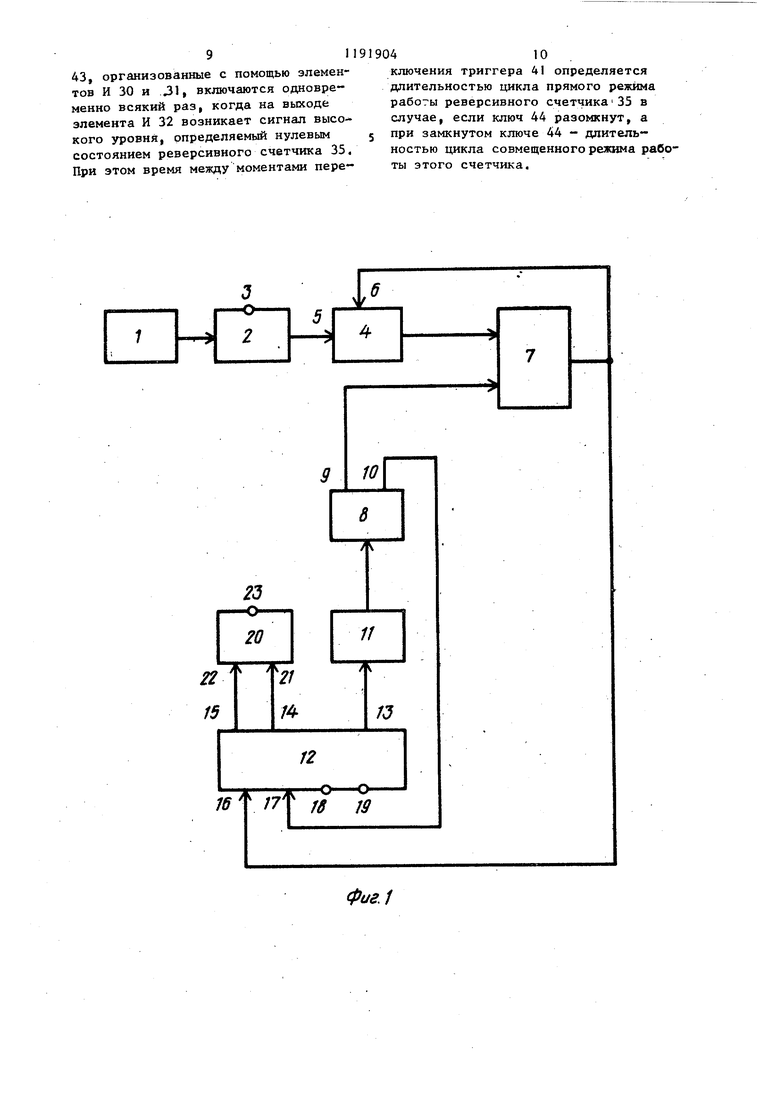

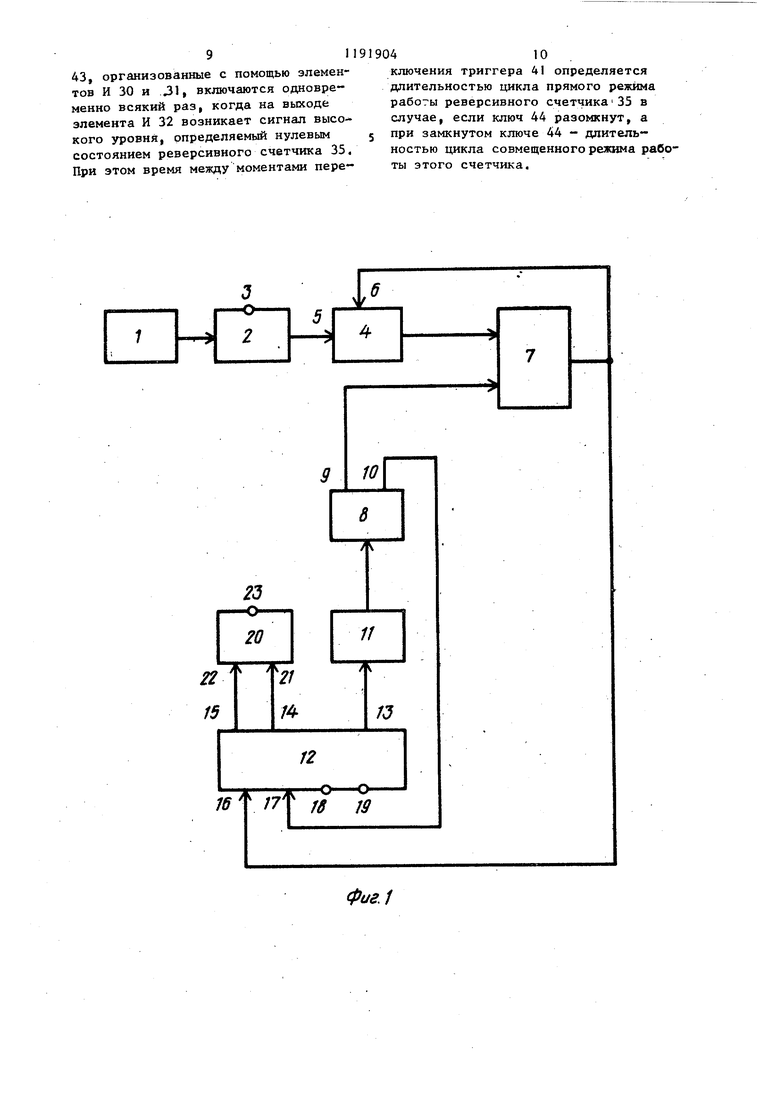

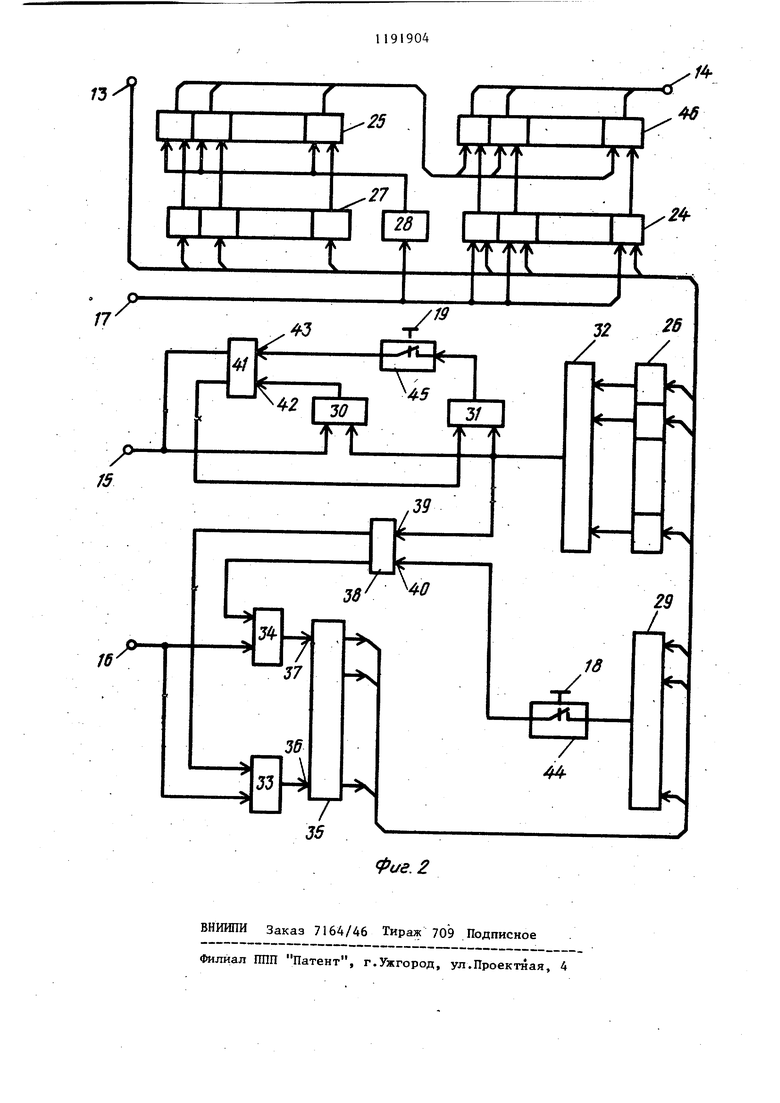

На фиг. 1 представлена структурная схема цифрового генератора периодических сигналов; на фиг. 2 - схема блока формирования адресов.

Цифровой генератор период ических сигналов содержит генератор 1 импульсов, делитель 2 частоты с входом 3 предварительной установки переменного коэффициента деления, счетчик 4 со счетным 5 и сбросовым 6 входами, схему 7 сравнения, регистр 8 кода с первым 9 и вторым 10 выходами, блок 11 памяти, блок 12 формирования адресов с первьм 13, вторым 14 и третьим 15 выходами, первым-четвертым 16-19.входами, преобразователь коданалог 20 с первым 21, вторым 22 входами и выходом 23, который одно- . временно является выходом цифрового генератора периодических сигналов.

Блок формирования адресов 12 содержит следующие узлы: первую и вторую группы элементов И 24 и 25 соответственно, первую и вторую группы элементов .НЕ 26 и 27 соответственно, элемент НЕ 28, первый - шестой элементы И 29-34 соответственно, реверсивный счетчик 35 с входами

прямого 36 и обратного 37 счета, первый триггер 38 с R-входом 39 и S-входом 40, второй триггер 41 с R-входом 42 и S-входом 43, первый и второй ключи 44 и 45 соответственно, группу элементов ИЛИ 46.

Делитель частоты 2 с входом 3 для установки переменного коэффициента деления представляет собой счетчик с предварительной установкой, рабртающий в циклическом режиме. Этот счетчик формирует на своем выходе сигнал всякий раз, когда количество импульсов, поданных на его вход, становится кратным коэффициенту деления. Для этого на триггерных ячейках счетчика устанавливается фиксированное число, дополняющее коэффициент деления до числа 2, где п - количество двоичных разрядов счетчика. Установка триггерных ячеек счетчика в необходимое положение осуществляется через вход 3. Делитель частоты выполнен по известной схеме.

Блок 11 памяти представляет собой совокупность адресуемых запоминающих элементов, которая совместно с регистром 8 кода и реверсивным счетчиком 35 образует перепрограм- мируемое постоянное запоминающее устройство. При этом реверсивный счетчи 35, содержимое которого воспроизводится на выходе 13, выполняет функции регистра адреса, а регистр 8 кода является регистром выходных данных t

Преобразователь код -аналог 20 позволяет менять полярность сигнала на выходе 23 благодаря тому, что его 3 выходным элементом является переклю чатель полярности, управляемый сигналом переполнения, поступающим с выхода 15 блока 12 на вход 22. Блок 12 формирования адресов вое производит на своем выходе 14 посту пакицие на этот выход данные как в прямом, так и в обратном двоичном коде. Для управления формированием на выходе 14 прямого или обратно го кода воспроизводимого числа, используется один разряд каждого из двоичных слов, хранящихся в блоке 11, Остальные разряды каждого из этих слов хранят код интервала времени меязду узлами квантования выход ного сигнала цифрового генератора. При вьшоде указанных слов на регистр 8 содержимое разрядов, отобра жающих интервал времени, воспроизво дится на выходе 9 этого регистра, а состояние разряда, управляющего образованием прямого или обратного кода данных, фиксируется на выходе 10 того же регистра. Цифровой генератор периодических сигналов работает следующим образом .Принцип, на котором основана работа цифрового генератора, формирующего на своем выходе 23 сигнал сту пенчатой формы, заключается в том, что позиционные двоичные.коды на выходах 13 и 14 блока 12 получают единичные приращения в моменты времени, которые соответствуют моментам равномерного по уровню квантова ния воспроизводимой функции. При этом на выходе 13 блока 12 формируются коды адресов ячеек памяти блока 1 в которых хранятся коды интервалов времени между узлами квантования выходного сигнала, отображающего нг выходе 23 периодическую функцию вре мени. Одновременно с образованием на выходе 13 того или иного кода равный или обратный ему код формируется на вьпсоде 14, который в каждьй текущий момент времени определяет абсолютную величину воспроизво димой функции. Цифровой генератор периодических сигналов функционирует в двух режимах, определяемых настройкой реверсивного счетчика 35: прямом и со мещенном. В прямом режиме реверсивный счет чик 35 ведет непрерывный счет импульсов, воздействующих на вход 04. 4 16, последовательно изменяя свое содержимое от нуля до максимально возможной величины, многократно повторяя эти действия. Совмещенный режим работы реверсивного счетчика 35 реализует непрерывное чередование прямого .счета импульсов, воздействующих на вход 16, с обратным, В этомслучае содержимое реверсивного счетчика 35 циклически меняется от нуля до предельного значения и от него до нуля, Для обеспечения правильного функционирования цифровой генератор периодических сигналов должен быть настроен на воспроизведение определенной функции с заданной частотой. Эта настройка заключается в выполнении следующих операций. Занесение информации в ячейки памяти блока 1 I. Эта операция осу ществляется по известной технологии ввода данных, в перепрограммируемые постоянные запоминающие устройства. Установка коэффициента деления частоты на делителе 2 частоты. Эта операция выполняется для обеспечения заданной частоты воспроизведения известной функции. Установка ключа 44 в одном из двух фиксированных положений для организации прямого или совмещенного .режима работы реверсивного счетчика 35. При разомкнутом положении ключа 44 реализуется прямой режим работы при замкнутом - совмещенный. Установка ключа 45 в одно из двух фиксированных положений для управления полярностью выходного сигнала цифрового генератора. При разомкну том ключе 45 обеспечивается постоянство полярности выходного сигнала,, при замкнутом ключе 45 полярность выходного сигнала периодически изменяется, В этом случае изменение знака выходного сигнала происходит в моменты, когда содержимое счетчика 35 равно нулю, а время между этими моментами зависит от состояния ключа 44, При разомкнутом ключе 44 это время равно длительности цикла прямого режима, а при замкнутом - совмещенного режима. Цифровой генератор.периодических сигналов начинает работу при нулевом содержимом счетчика 4 и реверсивного счетчика 35 после выполнения настроечных операций. При этом

на выходе 13 фиксируется нулевой код, а содержимое нулевой ячейки :блока 11, определяющее время до -первого квантования выходного сигна ла, выводится на регистр 8. Запуск генератора импульсов 1 обеспечива.ет поступление сигналов на счетный вход 5 счетчика 4 с частотой, равной отношению частоты импульсов генератора 1 к коэффициенту деления частоты, установленному на делителе 2

В момент совпадения содержимого счетчика 4 с кодом на выходе 9 реги стра 8 схема 7 формирует импульс, воздействующий на сбросовый вход 6 счетчика 4 и на вход приращения 16 блока 12. Вследствие этого содержимое счетчика 4 вновь становится равным нулю, а на выходе 13 блока 12 . устанавливается код, равный единице, что приводит к вьшоду на регистр 8 содержимого первой ячейки блока 1I.

Далее указанный процесс многократно повторяется с той разницей, что время между последующими импульсами на вьпсоде схемы 7 определяется содержимым других ячеек памяти блока 11.

При этом адреса возбуждаемых ячеек памяти блока 11 меняются в соотвётствии с назначенным режимом работы реверсивного счетчика 35, поскольку его содержимое воспроизводится на выходе 13.

Прямой режим работы реверсивного счетчика 35 определяется разомкнутым состоянием ключа 44. В этом случае при нулевом исходном состоянии ревер сивного счетчика 35 сигналы прямых выходов всех разрядов этого счетчика пройдя через соответствующие элемен- ты НЕ группы 26, вызывают появление сигнала высокого уровня на выходе элемента И 32. Этот сигнал, поступая на R-вход триггера 38, ставит его в нулевое состояние. Поскольку цепь воздействия на S-вход 40 этого триггера разомкнута ключом 44, то тригге 38 и впредь остается в нулевом положении. Следовательно, триггер 38 при этом постоянно воздействует на один из входов элементов И 33 и 34 сигнаг лами низкого и высокого уровней соответственно. Импульсы, воздействукяцие при этом на вход 16 приращения, чере элемент И 33 проходят на вход 36 прямого счета реверсивного счетчика 35, вызывая циклическое изменение содержимого этого счетчика от нуля до максимума. Соответственно этому адресуются ячейки блока 11.

Совмещенный режим работы реверсивного счетчика 35 Имеет место при замкнутом ключе 44. В этом случае на реверсивном счетчике 35 последовательно реализуется прямой и обратный счет шпульсов, поступающих на вход 16. Поскольку ключ 44 замкнут, то к моменту завершения прямого счета, когда на реверсивном счетчике 35 установится максимальное число, кодируемое единицами во всех разрядах, на S-вход 40 приходит сигнал высокого уровня, возникающий при этом на выходе элемента И 29. Одновременно с этим на R-вход 39 триггера 38 со стороны элемента И 32 поступает сигнал низкого уровня. Вследствие этого триггер 38 переходит иЗ нулевого состояния в едй ничное, а сигналы на его выходах меняют свою полярность. Следовательно, импульсы, воспринимаемые входом 16 приращения в этом случае возбуждают вход 37 обратного счета реверсивного счетчика 35, поступая на него через элемент И 34. Счетчик 35 последовательно уменьшает свое содержимое до нуля. Нулевое содержимое реверсивного счетчика 35 вызывает изменение полярности сигналов на входах 39 и 40 триггера 38, что изменяет его состояние и приводит к повторению цикли, характеризующего совмещенный режим.

При совмещенном режиме работы ре-, версивного счетчика 35 возбуждаемые адреса ячеек памяти блока 11 циклически повторяются, а внутри каждого цикла они последовательно меняются от нулевого значения до максимального, а затем от максимального до нулевого. Такая адресация ячеек памяти в сочетании с возможностью изменения полярности сигнала на выходе 23 генератора позволяет генерировать сигналы, воспроизводящие четные и нечетные симметричные функции, например гармонические. При зтом минимизируется объем применяемых запоминающих элементов для блока 11.

Одновременно с изменением кода на вьпсоде 13, которое выполняется йнкрементно, инкрементно изменяется и сигнал на выходе 14. При зтом обеспечивается формирование на выходе 14 позиционного двоичного кода, равного или обратного коду на выходе 13. Это необходимо, например, для генерации релаксационных колебаний и воспроизведения функций, имеющих на интервале прямого цикла два сбпря- женных .монотонных участка с разными знаками производной. Управление образованием кода на выходе 14 выполняется по бинарному сигналу, поступающему с выхода 10 регистра 8 на вход 17 управления образованием кода блока 12, и осуществляется следующим образом. Код, сформированный реверсивным счетчиком 35 и воспроизводимый на выходе 13, поступает также и на груп пу элементов И 24. Группа 25 воспринимает зтот код поразрядно, использу при этом один из входов каждого свое го элемента И. Благодаря этому при высоком уровне сигнала на входе 17, который воздействует на другие входы элементов И группы 24, выходы послед ней дублируют содержимое счетчика 35. При этом на выходах группы элементов И 25 формируются сигналы низкого уровня, поскольку на один из входов каждого элемента этого блока воздействует сигнал низкого уровня; Этот сигнал низкого уровня поступает с выхода элемента НЕ 28, который инвертирует сигнал высокого уровня, воздействующий на вход 17. Следовательно, в этом случае груп па 46 элементов ИЛИ, передавая на Ёыход 14 состояние элементов И группы 24, воспроизводящих содержимое реверсивного счетчика 35, обеспечива ет совпадение кодов на выходах 13 и 14., Низкий уровень сигнала на входе 17 приводит к формированию на выходе 14 кода, обратно коду на выходе 13 Это происходит благодаря тому, что, с одной стороны, сигнал низкого уровня входа 17, воздействуя на элементы И группы 24, приводит к формированию на вьпсодах элементов этой группы сигналов низкого уровня, с другой стороны-, сигнал высокого уровня, образуемый на выходе элемента НЕ 28, поступает на вход -каждого элемента И группы 25, благодаря чему эта группа элементов дублирует на выходах своих элементов выходные сигналы элементов группы 27. Поскольку реверсивный счетчик 35 поразрядно соединен с элементами НЕ гр5шпы 27, то выход последнего, а значит и выход группы -25, отображает код, обратный зафиксированному реверсивным с.четчиком 35. В результате логического сложения бинарных сигналов группы 25 и сигналов низкого уровня группы 24, выполняемого элементами ИЛИ группы.46, на выходе последней образуется код, обратный зафиксированному реверсив-ным счетчиком 35 и коду на выходе 13. Полярность периодического сиг-и: нала на выходе 23 цифрового генератора определяется уровнем сигнала на выходе 15 триггера 41. Управление уровнем сигнала на выходе 15 осуществляется ключом 45. При разомкнутом кгаоче 45 цифровой генератор периодических сигналов работает с неизменной полярностью выходного сигнала. Это происходит потому, что при исходном состоянии, реверсивного счетчика 35, когда его содержимое равно нулю, на выходе элемента И 32 возникает сигнал высокого уровня. Если при этом триггер 41 находится в единичном состоянии, то сигнал его пряWoro выхода 5, воздействуя вместе с сигналом высокого уровня элемента И 32 на входы элемента И 30, вызыва- ет на выходе этого элемента сигнал высокого уровня. Этот сигнал, возбуждая R-вход 42 триггера 41, переводит его в нулевое состояние. Если же при исхо.цном положении реверсивного счетчика 35 триггер 41 находится в нулевом состоянии, то оно не претерпевает изменения. Нулевое состояние триггера 41 при разомкнутом ключе 45, а значит и полярность сигнала на выходе 23 остаются неизменными и впредь, так как разомкнутый ключ 45 исключает какое-либо воздействие на S-вход 43 триггера 41. При замкнутом ключе 45 состояние триггера 41, а значит и полярность сигнала на выходе 23 изменяются всякий раз, когда содержимое реверсивного счетчика 35 принимает нулевое значение, вызьшая сигнал переполнения блока 12. Это происхоит потому, что перекрестные обратые связи прямого и обратного выхоов триггера 41 с его входами 42 и 43, организованные с помощью элементов И 30 и 31 включаются одновре менно всякий раз, когда на выходе элемента И 32 возникает сигнал высокого уровня, определяемый нулевым состоянием реверсивного счетчика 35, При этом время между моментами пере1410 . ключения триггера 41 определяется длительностью цикла прямого режима работы реверсивного счетчика35 в случае, если ключ 44 разомкнут, а при замкнутом ключе 44 - длительностью цикла совмещенного режима работы этого счетчика.

W д

J

0

1

22

21 /4

15

;7t

16

18 19

фиг.1

| Информационный листок ВИМИ , № 83-2022 | |||

| М., 1983 | |||

| Гененратор функций | 1973 |

|

SU475614A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-15—Публикация

1984-05-23—Подача