1

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, например для измерительных систем.

Целью изобретения является повышение быстродействия сумматора.

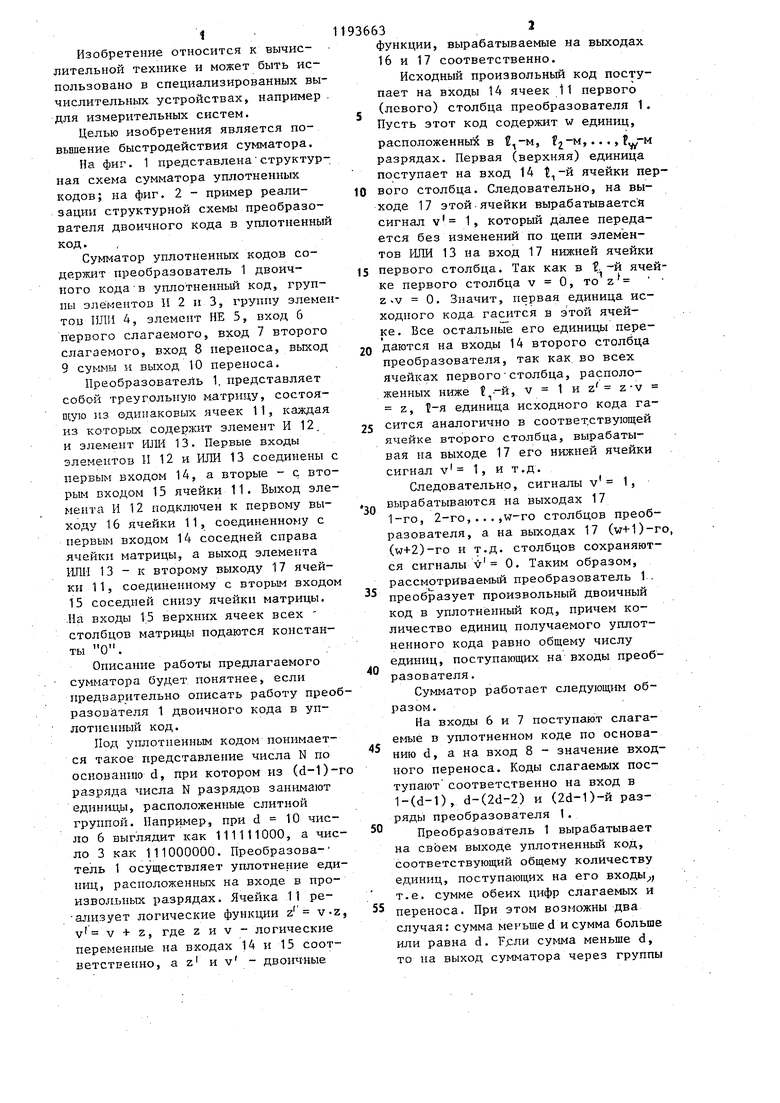

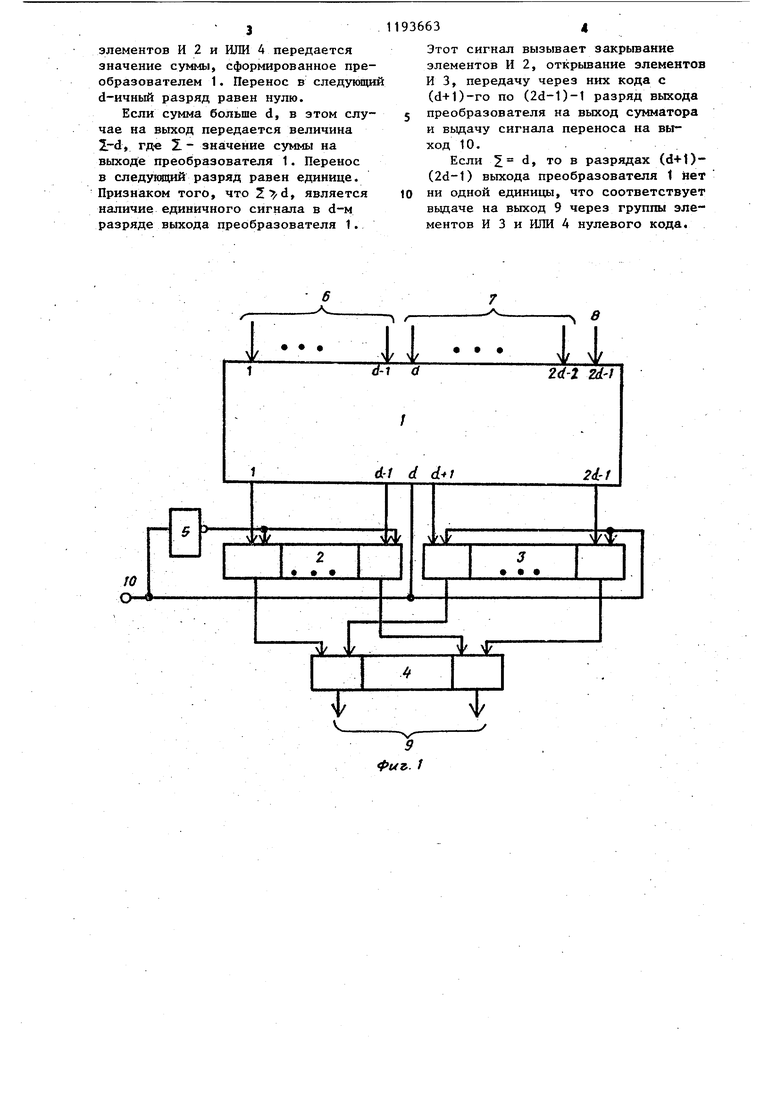

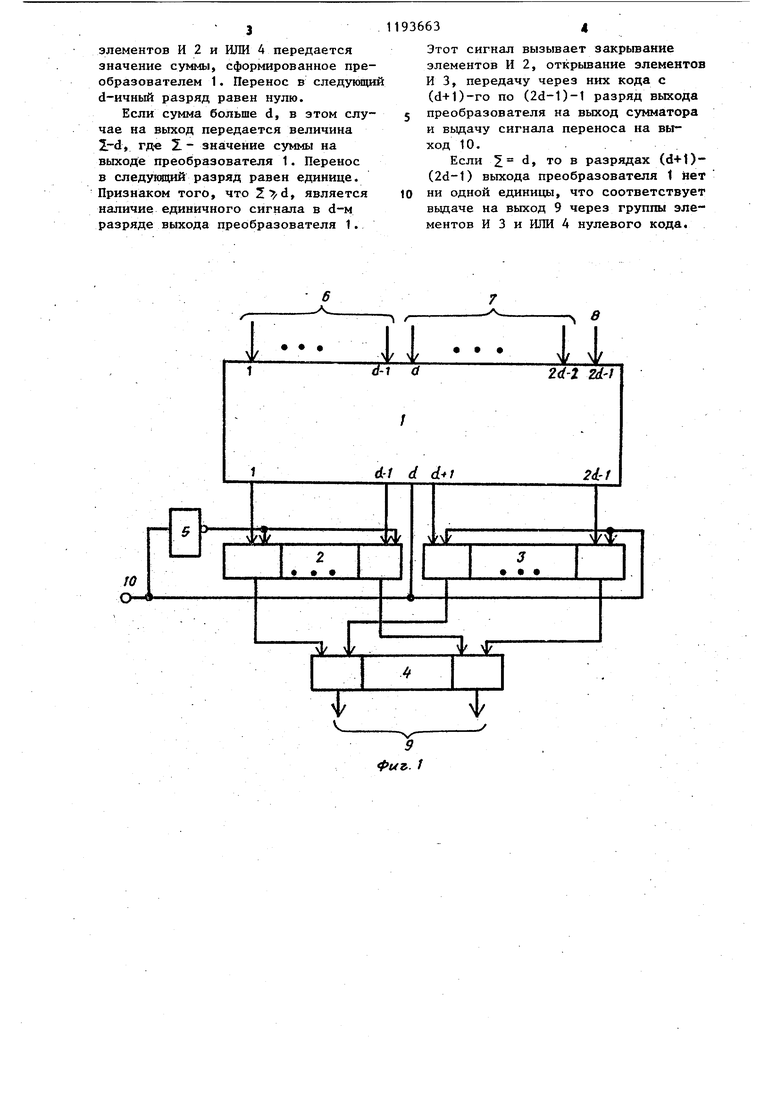

На фиг. 1 представлена;структурная схема сумматора уплотненных кодов; на фиг. 2 - пример реализации структурной схемы преобразователя двоичного кода в уплотненный код. ,

Сумматор уплотненных кодов содержит преобразователь 1 двоичного кодаВ уплотненньш код, группы элементов И 2 и 3, группу элеметов ИЛИ А, элемент НЕ 5, вход 6 первого слагаемого, вход 7 второго слагаемого, вход 8 переноса, выход 9 суммы и выход 10 переноса.

Преобразователь 1, представляет собой треугольную матрицу, состоящую из одинаковых ячеек 1I, каждая из которых содержит элемент И 12, и элемент ШШ 13. Первые входы элементов И 12 и 1-1ПИ 13 соединены первым входом 14, а вторые - с вторым входом 15 ячейки 11. Выход элемента И 12 подключен к первому выходу 16 ячейки 11, соединенному с первым входом 14 соседней справа ячейки матрицы, а выход элемента ИДИ 13 - к второму выходу 17 ячейки 1 1 , соединенному с вторым входо 15 соседней снизу ячейки матрицы. .На входы 15 верхних ячеек всех столбцов матрицы подаются константы О.

Описание работы предлагаемого сумматора будет понятнее, если предварительно описать работу преоразователя 1 двоичного кода в уплотненный код.

Под уплотненным кодом понимается такое представление числа N по основанию d, при котором из (d-l)разряда числа N разрядов занимают единицы, расположенные слитной группой. Например, при d 10 число 6 выглядит как 111111000, а число 3 как 111000000. Преобразователь 1 осуществляет уплотнение единиц, расположенных на входе в произвольных разрядах. Ячейка 11 реализует логические функции z v-z v V + z, где z и V - логические переменные на входах 14 и 15 соответственно, а z и v - двоичные

93663 ,2

функции, вырабатываемые на выходах 16 и 17 соответственно.

Исходный произвольньй код поступает на входы 14 ячеек 11 первого (левого) столбца преобразователя 1. Пусть этот код содержит w единиц,

расположенных в ,-M, -м,..., разрядах. Первая (верхняя) единица поступает на вход 14 t., -и ячейки первого столбца. Следовательно, на выходе 17 этой.ячейки вырабатываете сигнал v 1, который далее передается без изменений по цепи элементов ИЛИ 13 на вход 17 нижней ячейки

15 первого столбца. Так как в t -и ячейке первого столбца v О, то z z«V 0. Значит, первая единица исходного кода гасится в этой ячейке. Все остальные его единицы передаются на входы 14 второго столбца преобразователя, так как во всех ячейках первогостолбца, расположенных ниже t -и, V 1 и z z-v

t-я единица исходного кода гаZ ,

5 сится аналогично в соответствующей ячейке второго столбца, вырабатывая на выходе 17 его нижней ячейки сигнал v 1, и т.д.

Следовательно, сигналы v 1,

- вырабатываются на выходах 17

1-го, 2-го,...,w-ro столбцов преобразователя, а на выходах 17 (w+1)-ro, (w+2)-ro и т.д. столбцов сохраняются сигналы v 0. Таким образом, рассмотрИваемый преобразователь 1.

преобразует произвольный двоичный код в уплотнённый код, причем количество единиц получаемого уплотненного кода равно общему числу единиц, поступающих на входы преобразователя.

Сумматор работает следующим образом.

На входы 6 и 7 поступают слагаемые в уплотненном коде по основанию d, а на вход 8 - значение входного переноса. Коды слагаемых поступают соответственно на вход в 1-(d-1), d-(2d-2) и (2d-1)-й разряды преобразователя 1.

Преобразователь 1 вырабатывает на своем выходе уплотненньпЧ код, соответствующий общему количеству единиц, поступающих на его входы, т.е. сумме обеих цифр слагаемых и

5 переноса. При этом возможны два случая: сумма меньше d и сумма больше или равна d. Ррли сумма меньше d, то на выход сумматора через группы

элементов И 2 и ИЛИ А передается значение суммы, сформированное преобразователем 1. Перенос в следукици d-ичный разряд равен нулю.

Если сумма больше d, в этом случае на выход передается величина X-d гд« Z. - значение суммы на выходе преобразователя 1. Перенос в следуняций разряд равен единице. Признаком того, что , является наличие единичного сигнала в d-м разряде выхода преобразователя 1.

Этот сигнал вызывает закрьшание элементов И 2, открьшание элементов И 3, передачу через них кода с (d+1)-ro по (2d-1)-1 разряд выхода преобразователя на выход сумматора и вьздачу сигнала переноса на выход 10.

Если 5 d, то в разрядах (d+1 )(2d-1) выхода преобразователя 1 нет ни одной единицы, что соответствует выдаче на выход 9 через группы элементов И 3 и ИЛИ 4 нулевого кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования М-чисел | 1987 |

|

SU1545216A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1984 |

|

SU1171787A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

СУММАТОР УПЛОТНЕННЫХ КОДОВ, содержащий две группы элементов И, группу элементов ИЛИ и элемент НЕ, 6 тлич ающийс я тем, что, с целью повышения быстродействия, он содержит преобразователь двоичного кода в уплотненный код, причем входы преобразователя двоичного кода в уплотненный код с первого по (с1-1)-й, где eJ - основание системы счисления, подключены к разрядам входа первого слагаемого сумматора, входы с d по ()-й подключены к разрядам входа второго слагаемого сумматора, а

о

i 1 J/ J/

7 /ч.

f/г. /

«jT

/ff

/«

fid-f)

//

/5

/7

.

4

19

/

IS

/«

/

//

n

I

.

/fX

/

/4.

/5

16

i-

//

//

4

r/;/ ;

«e. 2

13

17 Ч

J/

16

//

(2d-1)

| Оптоэлектронный сумматор | 1978 |

|

SU742936A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU796845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1983-10-21—Подача