1

Изобретение относится к области вычислительной техники и может быть использовано, в частности, для ап1паратной реализации операции деления в специализированных цифровых вычислительных машинах, работаюадих в двоичной системе счисления с фиксированной запятой.

Известно устройство для деления, содержащее блок анализа значка псевдочастного, выход которого соединен с первым входом первого и второго сумматорОВ-вычитателей, выходы которых подключены соответственно к информационным входам накопительных сдвиговых регистров, упра1вляющие входы которых связаны соответственно с первым и вторым выходами блока управления, причем выходы накопительных сдвиговых регистров соединены соответственно с вторыми входами сумматоров-:вычитателей, а выход знакового разряда второго накопительного сдвигового регистра подключен к входу блока анализа знака псевдочастного.

Недостатком известного устройства является большое время выполнения операции деления, а также сложность структуры устройства.

Целью настояш.его изобретения является увеличение быстродействия выполнения операции деления.

Поставленная цель достигается введением блока анализа сходимости процесса, вход которого соединен с дополнительным выходом второго накопительного сдвигового регистра,

а выход - с входом блока сброса, выход которого связан с входом блока управления, первый и второй дополнительные выходы которого соединены соответственно с входами блока формирования констант и рециркуляционного сдвигового регистра, выходы которых подключены соответственно к третьим входагм 1сумматоров-1вычитателей.

Такое конструктивное решение позволяет сократить время вычисления благодаря введению блоков анализа сходимости процесса и сброса, а также упрош,ает структуру устройства.

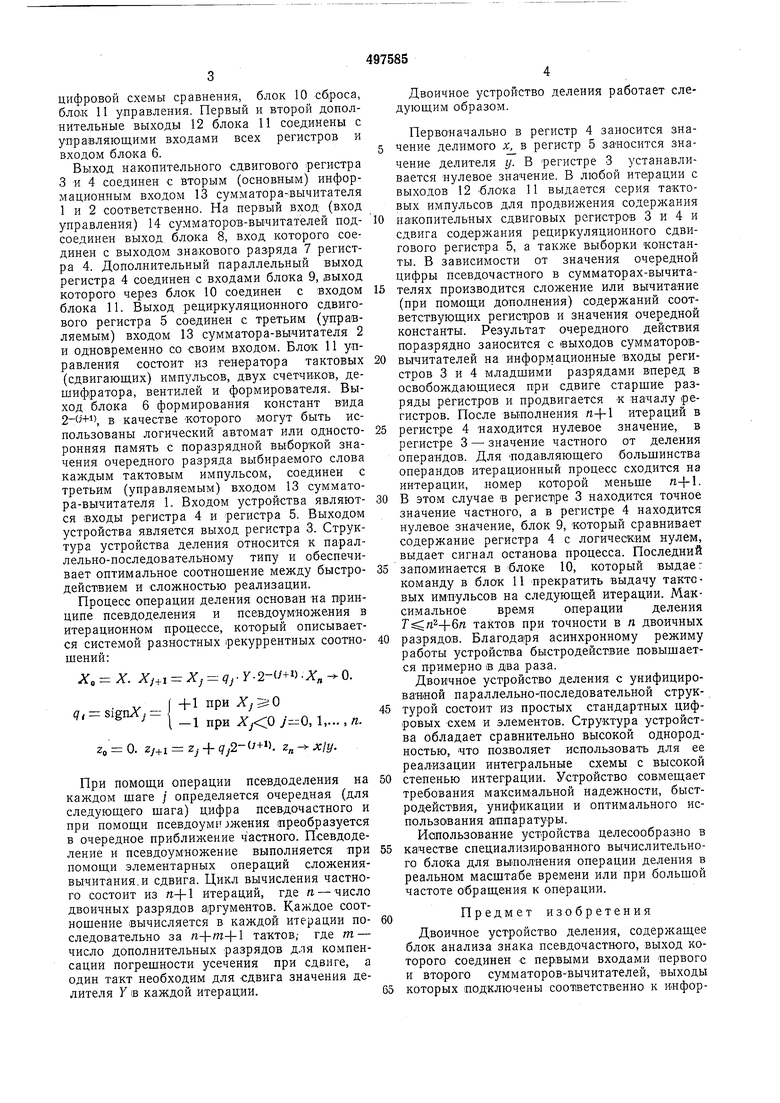

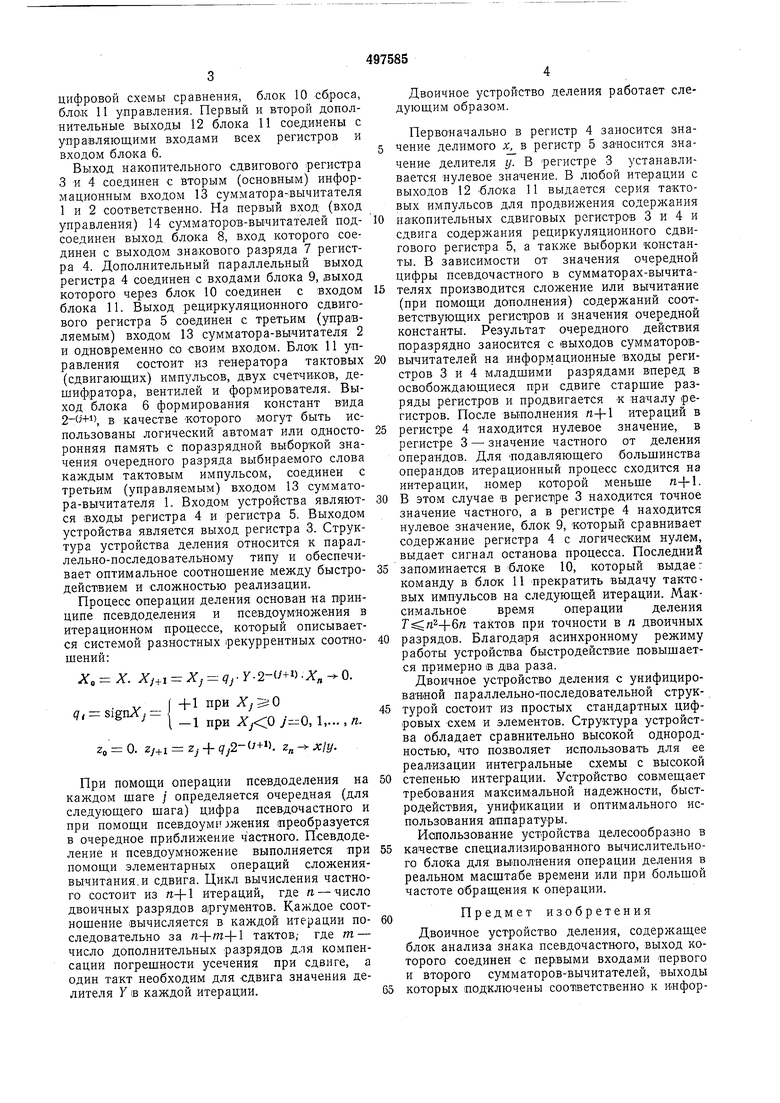

На чертеже представлена блок-схема двоичного устройства деления.

Устройство содержит два одноразрядных сумматора-вычитателя I и 2 комбинационного типа, два накопительных сдвиговых регистра 2 и 4, рециркуляционный сдвиговый регистр 5, блок 6 формирования констант,

знаковый разряд 7 второго накопительного сдвигового регистра 4, блок 8 анализа знака тсевдочастного, выполненный, например, в ЗИде триггера с вентилем, блок 9 анализа сходимости процесса, выполненный в виде 3 цифровой схемы сравнения, блок 10 сброса, блок 11 управления. Первый и второй дополнительные выходы 12 блока 11 соединены с управляющими входами всех регистров и входом блока 6.5 Выход накопительного сдвигового регистра 3 и 4 соединен с вторым (основным) информационным входом 13 сумматора-вычитателя 1 и 2 соответственно. На первый вход (вход управления) 14 сумматоров-вычитателей под-10 соединен выход блока 8, вход которого соединеи с выходом знакового разряда 7 регистра 4. Дополнительный параллельный выход регистра 4 соединен с входами блока 9, выход которого через блок 10 соединен с входом15 блока 11. Выход рециркуляционного сдвигового регистра 5 соединен с третьим (управляемым) входом 13 сумматора-вычитателя 2 и одновременно со своим входом. Блок 11 управления состоит из генератора тактовых20 (сдвигающих) импульсов, двух счетчиков, дешифратора, вентилей и формирователя. Выход блока 6 формирования констант внда 2-W+1), в качестве которого могут быть использованы логический автомат или односто-25 ронняя память с поразрядной выборкой значения очередного разряда выбираемого слова каждым тактовым импульсом, соединен с третьим (управляемым) входом 13 сумматора-вычитателя 1. Входом устройства являют-30 ся входы регистра 4 и регистра 5. Выходом устройства является выход регистра 3. Структура устройства деления относится к параллельно-последовательному типу и обеспечивает оптимальное соотношение между быстро-35 действием и сложностью реализации. Процесс операции деления основан на принципе п сев до деления и псевдоумножения в итерационном процессе, который описывается системой разностных рекуррентных соотно-40 щений: X -X X -X - а Y-i-a+ -X 0 о- 1+1- } - 4j- я f +1 при X yQ (7i - sigiiA I 45 1 при У-О, ,. .я. 2 о Z - Z - -i72-(+) Z - xlii 0- }+1 jTHj п 1У При помощи операции псевдоделения на50 каждом щаге / определяется очередная (для следующего щага) цифра псевдочастного и при помощи псевдоуми жжения (преобразуется в очередное приближение частного. Псевдоделение и псевдоумножение выполняется при55 помощи элементарных операций сложениявычитания.и сдвига. Цикл вычисления частного состоит из п+1 итераций, где п - число двоичных разрядов аргументов. Каждое соотношение 1вычисляется в каждой итерации по-60 следовательно за п- -т-}- тактов,- где т- число дополнительных разрядов для компенсации погрешности усечения при сдвиге, а один такт необходим для сдвига значения делителя У IB каждой итерации.G5 4 Двоичиое устройство деления работает следующим образом. Первоначально в регистр 4 заносится значение делимого х, в регистр 5 заяосится значение делителя у. В регистре 3 устанавливается иулевое значение. В любой итерации с выходов 12 блока 11 выдается серия тактовых импульсов для продвижения содержания на1копительных сдвиговых регистров 3 и 4 и сдвига содержания рециркуляционного сдвигового регистра 5, а также выборки константы. В зависимости от значения очередной цифры псевдочастного в сумматорах-вычитателях производится сложение или вычитание (при помощи дополнения) содержаний соответствующих регист ров и значения очередной константы. Результат очередного действия поразрядно заносится с выходов сумматороввычитателей на информационные входы регистров 3 и 4 младщими разрядами вперед в освобождающиеся при сдвиге старщие разряды регистров и продвигается к началу регистров. После выполнения n-f-1 итераций в регистре 4 находится нулевое значение, в регистре 3 - значение частного от деления операндов. Для -подавляющего больщинства операндов итерационный процесс сходится на интерации, номер которой меньше л-{-1. В этом случае в регист|ре 3 находится точное значение частного, а в регистре 4 находится нулевое значение, блок 9, который сравнивает содержание регистра 4 с логическим нулем, выдает сигнал останова процесса. Последний запоминается в блоке 10, который выдав: команду в блок И прекратить выдачу тактевых им-пульсов на следующей итерации. Максимальное время операции деления тактов при точности в п двоичных разрядов. Благодаря асинхронному режиму работы устройства быстродействие повыщается примерно в два раза. Двоичное устройство деления с унифицировавной параллельно-последовательной структурой состоит из простых стандартных цифровых схем и элементов. Структура устройст обладает сравнительно высокой однородностью, что позволяет использовать для ее реализации интегральные схемы с высокой степенью интеграции. Устройство совмещает требования максим-альной надежности, быстродействия, унификации и оптимального использования аппаратуры, Иопользование устройства целесообразно в качестве специализированного вычислительного блока для выполнения операции деления в реальном масштабе времени или при большой частоте обращения к операции, Предмет изобретения Двоичное устройство деления, содержащее блок анализа знака псевдочастного, выход которого соединен с первыми входами первого и второго сумматоров-вычитателей, выходы которых подключены соответственно к информационным входам накопительных сдвиговых perHCTpoiB, управляющие входы которых связаны соответственно с первым и вторым выходами блока управления, причем выходы накопительных сдвиговых регистров соединены соответственно с вторыми входами сумматоров-вычитателей, а выход знакового разряда второго накопительного сдвигового регистра подключен к входу блока анализа знака псевдочастного, отличающееся тем, что, с целью увеличения быстродействия, в устройство введен блок анализа сходимости процесса, вход которого соединен с дополнительным выходом второго накопительного сдвигового регистра, а выход - с входом блока

сброса, выход которого связан с входом блока управления, первый и второй дополнительные выходы которого соединены соответственно с входами блока формирования констант и рециркуляционного сдвигового регистра, выходы .которых подключены соответственно к третьим входам сумматоров-вычитателей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления элементарных функций | 1973 |

|

SU546890A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для умножения | 1975 |

|

SU579615A1 |

Авторы

Даты

1975-12-30—Публикация

1974-01-02—Подача