1

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации логических и арифметических операций и устройств.

Известны вычислительные автоматы, построенные на основе однородных структур (вычислительных сред). Однако соединение ячеек этих структур по принципу близкого действия накладывает ограничения на методы синтеза устройств, приводит к существенным затратам ячеек на реализацию соединительных каналов, что снижает эффективность использования однородных структур и построенных на их основе устройств.

Предлагаемое устройство отличается тем, что выходы коммутирующих элементов каждой строки матрицы объединены с соответствующим выходом блока памяти чисел и соединены с входами соответствующего многофункционального модуля, выход которого соединен с соответствующей вертикальной щиной матрицы коммутирующих элементов, выходы всех многофункциональных модулей соединены с входами блока управления, блока памяти чисел и с выходами устройства.

Это позволяет повысить эффективность и расщирить область применения устройства.

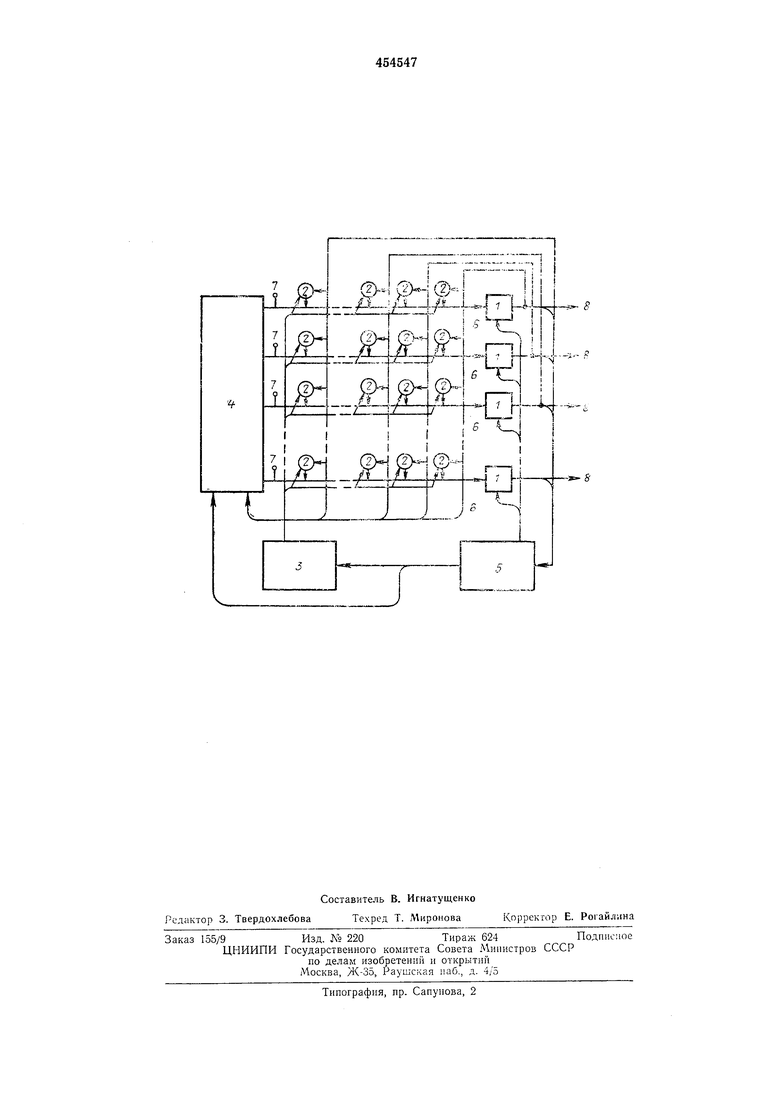

На чертеже изображена схема предлагаемого автомата.

Устройство содержит многофункциональные модули 1, матрицу коммутирующих элементов (КЭ) 2, блок настройки 3, блок памяти чисел 4, блок управления 5.

Многофункциональные модули 1 по сигналам настройки, подаваемым на управляющие входы 6 из блока управления 5, выполняют некоторые логические функции из заданного набора. Предусматривается возможность настройки модулей либо на выполнение одной и той же операции, либо на выполнение разных операций. Матрица коммутирующих элементов 2 предназначена для организации связей между логическими элементами. Матрица

содержит вертикальные и горизонтальные щины, в точках пересечения которых расположены коммутирующие элементы 2. Подключение КЭ к щинам таково, что при возбуждении КЭ сигналом, прищедшим на его управляющий

вход, КЭ пропускает сигналы с вертикальных щин на горизонтальные, но не наоборот. Вертикальные щины соединены с выходами модулей 1, а горизонтальные - с входами модулей. Такое построение коммутирующей матрицы позволяет соединять выход любого модуля с входами любых других модулей. Управляющие входы КЭ соединяются с выходами блока настройки 3, в котором хранятся коды связей между модулями или коды реализуемых структур.

Горизонта„тьные шины коммутирующей матрицы соединяют входы модулей с выходами блока памяти чисел 4, хранящего числа, над которыми выполняются операции схемой из модулей 1 и КЭ 2. Кроме того, чтобы числа можно было подавать в вычислительный автомат извне, горизонтальные Шины матрицы соединены с входными полюсами автомата 7. Результаты выполнения операций автомата снимаются с выходов 8, которые соединены с выходами модулей 1.

Для проведения многоптаговых вычислений промежуточные результаты записываются на хранение в блок 4. Для этого выходы модулей 1 соединены с входами блока 4.

По результатам анализа заданной для решения задачи определяется схема нз модулей I, соответствующим образом (но надежности, быстродействию) приспособленная для решения именно этой задачи. Соответствующая данной схеме система связей между модулями кодируется квадратной двоичной матрицей, которая записывается в блок настройки 3. Перед началом работы вычислительного автомата блок управления 5 считывает эти коды из блока 3, сигналы с выходов этого блока поступают на управляющие входы КЭ2. Те КЭ, на которые пришел единичный управляющий сигнал, возбуждаются и становятся способными передавать сигналы с вертикальных шин матрицы на горизонтальные. Это эквивалентно установлению связей между логическими элементами, а значит, и созданию искомой схемы устройства.

Далее блок управления 5 организует нодачу на входы созданного устройства чисел, предназначенных для обработки. Входами предлагаемого устройства являются входы некоторых модулей 1. Числа подаются на них через горизонтальные шины матрицы из блока

памяти чисел 4 или извне через входные полюса автомата 7.

Результат, полученный на выходах модулей 1 после прохождения обрабатываемых чисел через созданную схему, блок управления 5 выдает либо только на выходные полюса автомата, либо записывает еще и в блок памяти чисел 4 для использования в вычислениях на следующем этапе.

Вычисления следуюплего этапа проводит лнбо созданная ранее схема (если вычислительный процесс является итерационным), либо новая схема, которая создается блоком управления из модулей 1 я КЭ 2 путем считывания из блока настройки 3 кодов этой новой схемы.

Предмет изобретения

Универсальный вычислительный автомат,

содержащий матрицу коммутирующих элементов, входы которых соединены с соответствующими вертикальными и горизонтальными шинами, соединенными с выходами блока настройки, входы которого соединены с выходами блока управления, с которыми соединены также входы блока памяти чисел и управляющие входы многофункциональных модулей, отличающийся тем, что, с целью повышения эффективности и расширения области применения,, выходы коммутирующих элементов каждой строки матрицы объединены с соответствующим выходом блока памяти чисел и соединены с входами соответствующего многофункционального модуля, выход

которого соединен с соответствующей вертикальной шиной матрицы коммутирующих элементов, выходы всех многофункциональных модулей соединены с входами блока управления, блока памяти чисел и с выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное вычислительное устройство | 1977 |

|

SU696446A1 |

| Запоминающий модуль для матричных блоков памяти | 1978 |

|

SU746728A1 |

| ЭЛЕМЕНТ ОДНОРОДНОЙ СТРУКТУРЫ | 1970 |

|

SU287115A1 |

| УНИВЕРСАЛЬНЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ ЭЛЕМЕНТ | 1966 |

|

SU188146A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Устройство для определения минимальных членов при синтезе структур дискретных автоматов | 1977 |

|

SU680174A1 |

| ПРОГРАММИРУЕМЫЙ АВТОМАТ | 1973 |

|

SU397911A1 |

| ПРОГРЛЛАМИРУЕМЬШ АВТОМАТ | 1973 |

|

SU394788A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU641499A1 |

Авторы

Даты

1974-12-25—Публикация

1972-12-28—Подача