Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного процессора в составе многопро-г цессорных вычислительных систем.

Цель изобретения - увеличение быстродействия.

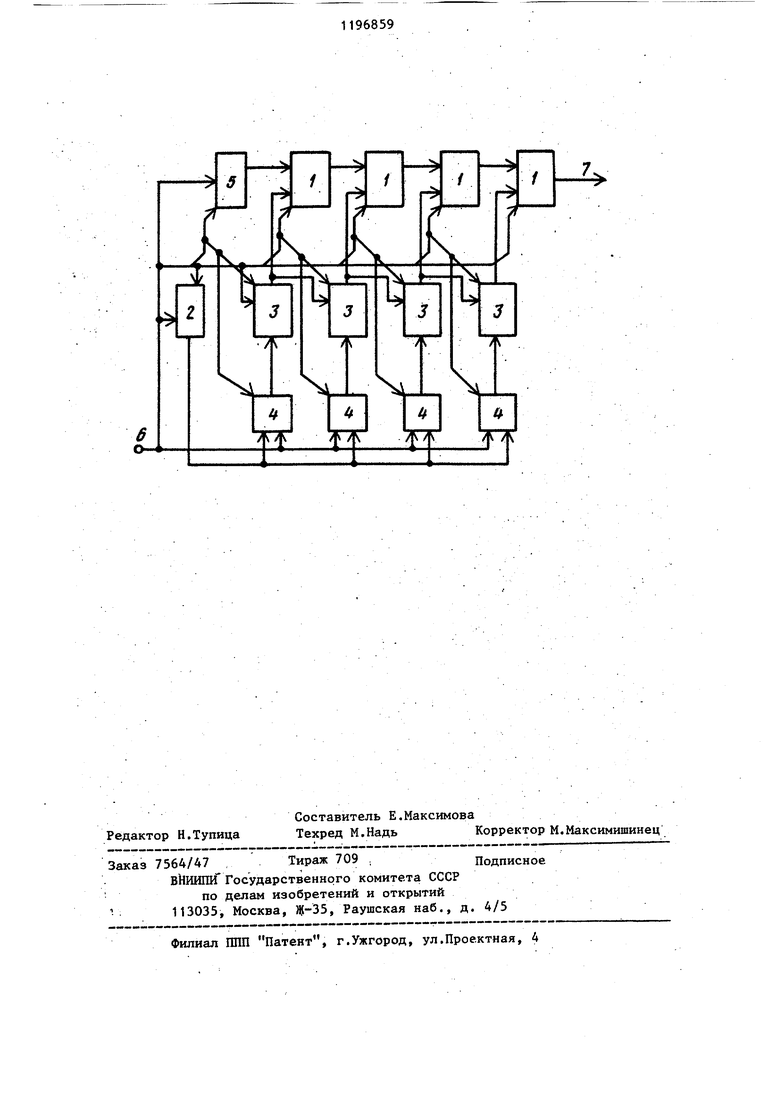

;На чертеже показана схема цифроBofp параллельного устройства для возведения в куб.

Предлагаемое цифровое параллельное устройство содержит п-1 сумматоров 1, гл-й сумматор 2, п-2 сумматоров-вычитателей 3, п-1 коммутаторов 4, ключ 5, входную 6 и выходную 7 .шины устройства.

Цифровое устройство для возведения в куб произвольного числа х, т.

. у xS(1)

происходит следующим образом.

Представим выражение (1) в разрядной форме как

г V V

V

XXX

у

где

разрядные векторы, представлякяцие со- зо бой разрядное изображение чиселх и yj

информируют следующие разрядные векторы

s«

VUI VU),

Представляют выражение (1) с учетом выражения (2) как

2Vx 4

9-CV XXX

(3)

, -..

(3) следующие

Вводят в равенство обозначения

) 2-vt,p

0-1 „(ИЗ

п-г

2 L 2- 2 х X .

Тогда значение у может числено по следуюи м реку зависимостям

V

, -ь.2-.,

V

0;

У«

у;-+ 2-n«i,

(4)

Уг

,., 2-(. 17, 3-,

V

у

ч- ft,

V V V У УП У п--,

т-гч

де

vH формируются как 2 Х-,

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Параллельное устройство для решения квадратного уравнения | 1984 |

|

SU1249532A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Устройство для деления | 1986 |

|

SU1381492A1 |

| Матричный вычислитель логарифмов | 1981 |

|

SU1012251A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для аппроксимации нелинейных зависимостей | 1984 |

|

SU1259287A1 |

| Матричное вычислительное устройство | 1984 |

|

SU1233141A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

ЦИФРОВОЕ ПАРАЛЛЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КУБ, содержащее два сумматора, отличающ е ее я тем, что, с целью увеличения быстродействия, в него введены п-2 сумматора, п-1 сумматоров-вычитателей, п-1 коммутатор и ключ (п разрядность устройства), причем выходы каждого i-ro сумматора (i 1,2,...,п-1) соединение входами первой группы (i+1)-ro сумматора, выходы каждого i-ro сумматора-вычитателя подключены к входам второй группы i-ro сумматора и со сдвигом .на один разряд в сторону младших разрядов к входам первой группы (i+t)-ro сумматора-вычитателя,-входы первой группы п-го сумматора соединены с информационными входами первых групп коммутаторов с второго по (п-1)-и информационными входами первого коммутатора и подключены к входной шине устройства, которая соединена с входами второй группы п-го сумматора со сдвигом на один разряд в сторону старших разрядов, выходы п-го сумматора соединены с информационными входами вторьк групп коммутаторов с второго по i (п-1)-и и с информационными входами первой группы первого коммутатора, (Л входы первой группы первого сумматора-вычитателя подключены со сдвигом на два разряда в сторону мпадших разрядов к входной шине устройства, (i+1)-й разряд которой соединен с управляющими входами i-ro сумматора, (i+1)-ro .сумматора-вычитасо теля и (i+1)-ro коммутатора, старО) ший разряд входной шины соединен с 00 управлякяцими входами ключа, первоСП го сумматора-вычитателя и первого со коммутатора, выходы (n-l)-ro сумматора соединены с выходной шиной устройства.

3

разрядная матрица, представляющая собой разрядные изображения х при количестве разрядов представления информации.

Записывают произведение матрицы X на вектор х в развернутом виде

(2)

i-l

2-1 5(Я+ 2- 5

(5)

,Mv. при 1

3-2

, 2-2(2) 1

(M.

при 2-25i«) 2-Ч l.vci-., 3-2-2

1-1

X

(M

при

) V (i-1) .2i V

j-1

X - 2 X

X 0

Цифровое параллельное устройство для возведения в куб функционирует следующим образом.

В исходном состоянии на входную шину устройства 6 подается значение

V Г1 It I п Н X X X ... X , которое поступает на информационный вход ключа 5, первый вход п-го сумматора 2, со сдвигом на один разряд в сторону старших разрядов на второй вход п-го сумматора 2, со сдвигом на два разряда в сторону младших разрядов, на первый вход первого сумматора-вьтитателя 3, на первые входы всех коммутаторов 4, начиная с второго и на второй вход первого коммутатора 4. Кроме того, значение старшего разряда X исходного вектора х подается на управляющие входыключа 5, первого суммат9ра-вычитателя 3 и первого коммутатора 4, а значение каждого (i+1)-ro разряда х исходного вектора подается соответственн на управляющие входы i-ro сумматора 1, (i+O-ro сумматора-вычитателя 3 и (i+1)-ro коммутатора 4. После это го в схеме устройства протекает пер ходной процесс, после окончания которого на выходе п-го сумматора 2 образуется значение Зх,которое подается на вторые входы коммутаторов 4, начиная с второго, и на первый вход первого коммутатора 4. Если значение первого разряда х вектора х равно единице , то значение х поступает через ключ 5 со сдвигом на два р-азряда в сторону младших разрядов на первый вход первого сумматора 1, первый суммато вычитатель 3 настраивается на сложе ние, благодаря чему на выходе его по выражению (5) вычисляется значение ( 2- и, которое подается на второй вход первого сум матора 1, а первый коммутатор 4 настраивается на передачу информаци с второго входа на выход, при этом значение х поступает на второй вход первого сумматора-вычитателя 3 со сдвигом на четыре разряда в сторону младших разрядов. Когда , то 5 закрыт, первьй сумматор-вычитатель ,3 настра ивается на вычитание, а коммутатор 4 - на передачу информации с первог входа на выход. Далее, если х 1, то первый сумматор 1 настраивается на сложение, второй сумматор-вычита тель - на сложение, второй коммутатор 4 - на передачу информации с второго входа на выход. Когда х О то первый сумматор 1 настраивается на передачу информации с первого входа на вькод, второй сумматор-вычитатель 3 - на вычитание, а второй коммутатор - на передачу информации с первого входа на выход. При этом с выхода второго коммутатора 4 значения X или Зх подается со сдвигом 94 на шесть разрядов в сторону младших разрядов на второй вход второго сумматора-вычитателя 3, на первый вход кот.орого подается значение 2 х из выхода первого сумматора-вычитателя 3. Во втором сумматоре-вычитателе 3 по выралсению (5) вычисляется значение 2 х, поступающее на второй вход второго сумматора 1. В первом сумматоре 1 по выражению (4) определяется значение у у + 2 , которое поступает на первый вход второго сумматора 1. Аналогично в зависимости от значения i-ro разряда х вектора х, равному х 1 или X О, (1-1)-й сумматор 1 настраивается на сложение или передачу информации с первого входа на выход, i-й сумматор-вычитатель 3 настраивается на сложение или вычитание и i-й коммутатор 4 на передачу информации с второго или первого входов на выход. Благодаря этому значение х или Зх поступает со сдвигом на 2(i+1) разряда в сторону младших разрядов с выхода i-ro коммутатора и на второй вход i-го-сумматора-вычитателя 3. В i-M сумматоре-вычитателе 3 по выражению (6) вычисляется значение , поступающее на второй вход i-ro сумматора 1. В (i-l)-M сумматоре 1 по выражению (4) определяется очередное значение у- , поступающее на первый вход i-ro сумматора 1. В зависимости от значения n-i , п- ., младшего разряда х 1, х О на выходе (n-l)-ro коммутатора 4 образуется значение х или Зх, поступающее на второй вход (h-l)-ro сумматора-вычитателя 3. В (п-1)-м сумматоре по выражению (6) вычисляется значение , поступанлцее на второй вход (п-1)-гс сумматора 1. При х 1 (п-1)-й сумматор 1 настраивается на сложение, когда i О - на величину информации из первого входа на выход. При этом в (п-1)-м сумматоре 1 по выражению (4) вычисляется искомое значение У У УП.Л + ) $, которое поступает на выходную шину устройства 7 . Вычислительный процесс организован параллельно и время решения в устройстве равно задержке сигнала между входом и выходом устройства..

| Устройство для возведения в куб | 1980 |

|

SU924704A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в куб | 1979 |

|

SU868755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-28—Подача