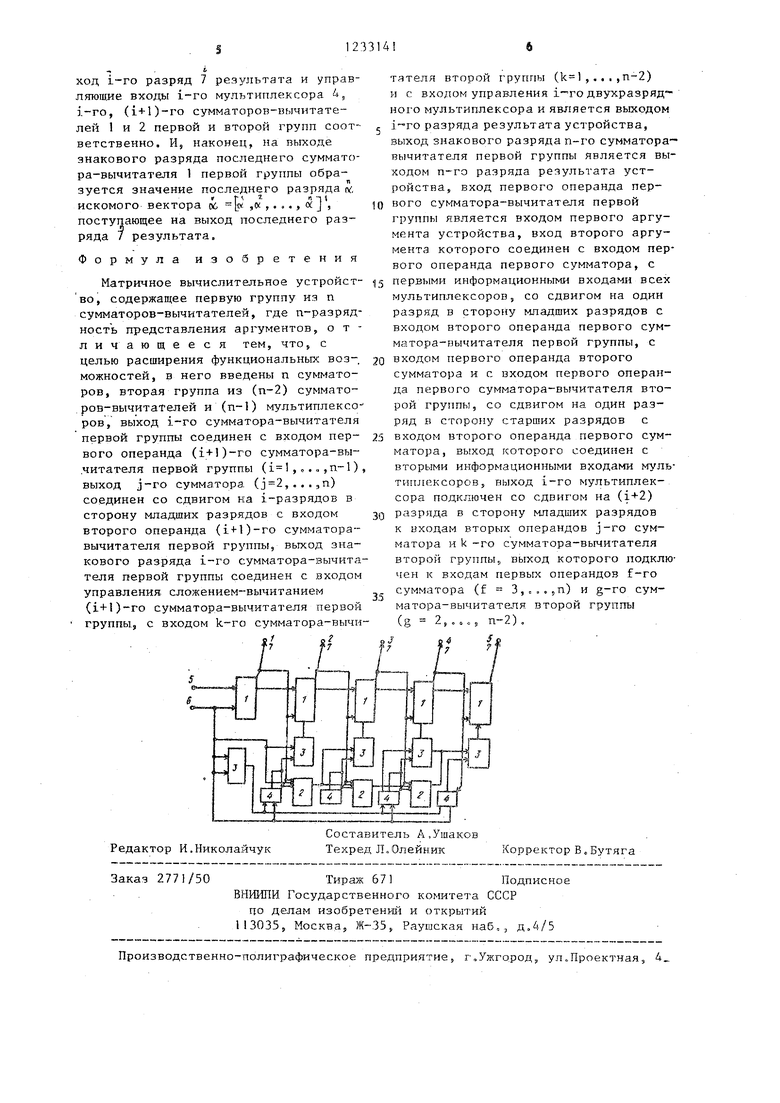

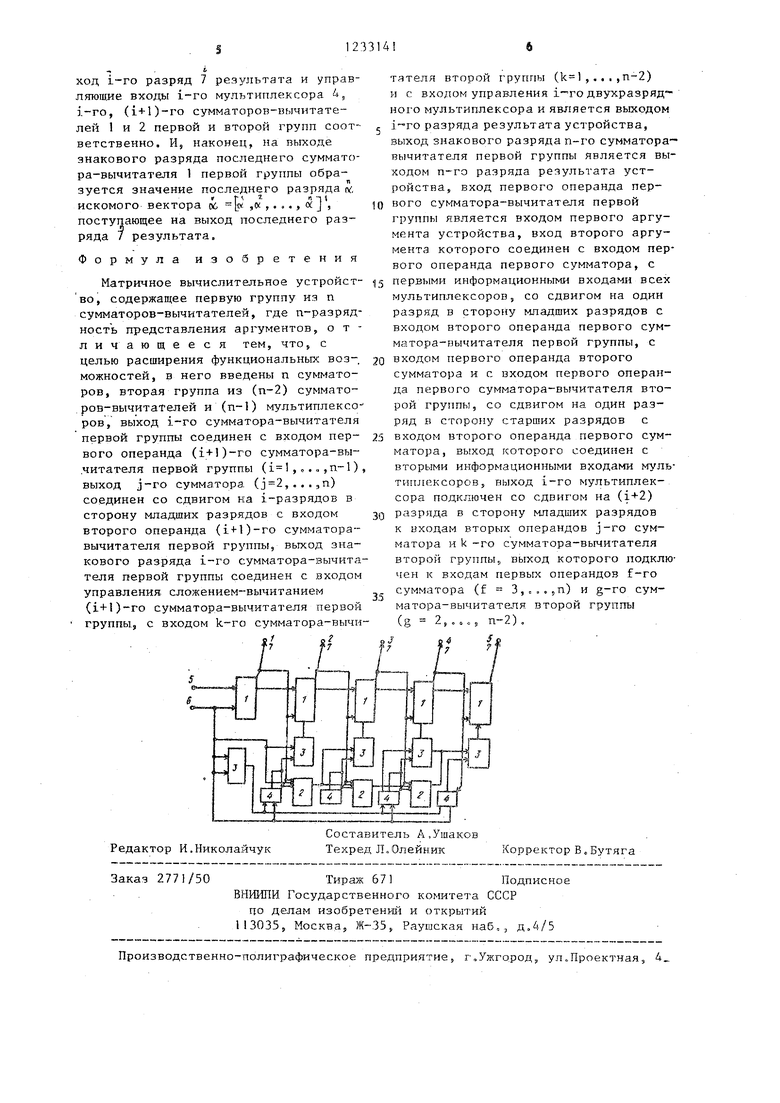

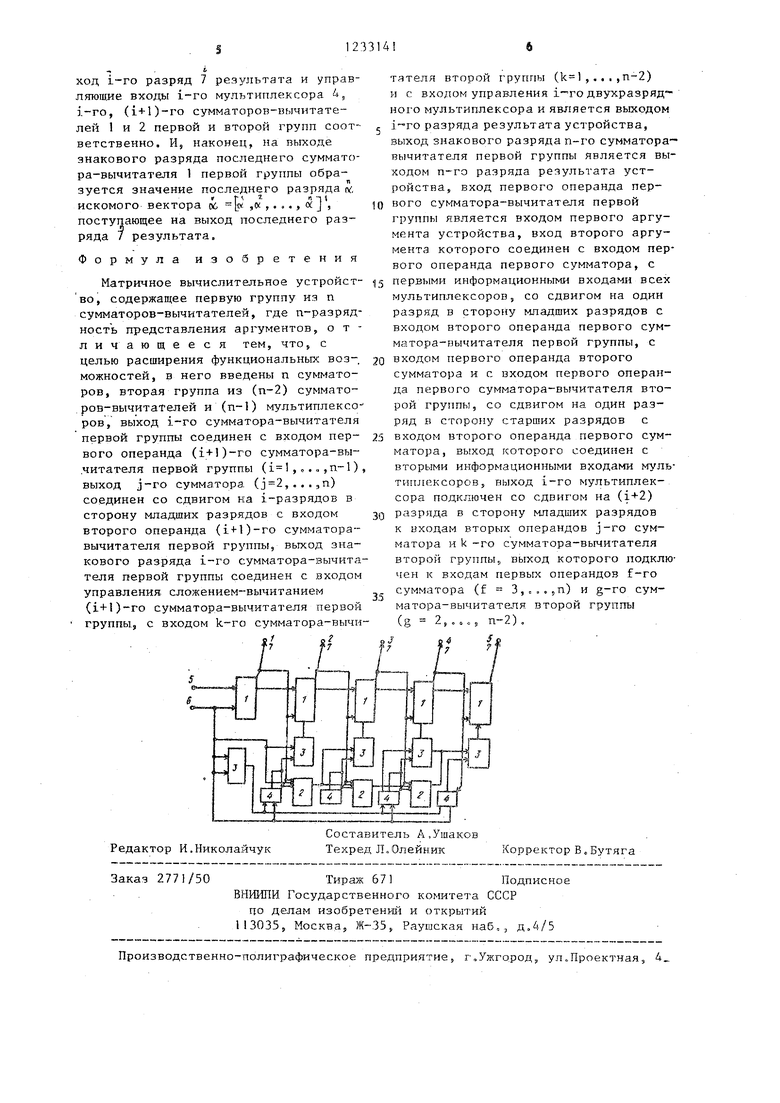

пы, n сумматоров 2, (n-1) мультиплек соров 4, вход 5 первого аргумента, вход 6 второго аргумента и выход разрядов 7 (,2,3,.,,,п) результата устройства.

Работа устройства для реализации зависимости вида

йб

10

Изобретение относится к вычислительной технике и может быть примерно автономно или в качестве спецпроцессора в комплексе с цифровой вычислительной машиной или в многопроцессорных вычислительных системах для оперативного вычисления функциональных зависимостей и увеличения производительности вычислений всей системы в целом.

Целью изобретения является расширение функциональных возможностей устройства.

На чертеже представлена функциональная схема устройства для случая, когда n 5 (n - разрядность представления информации).

Устройство содержит n сумматоров- вычитателей 1 первой группы, (п-2) . зо ое изображение чисел Ь, О, с6 соот- сумматоров-вычитателей 2 второй груп- ветственно;

происходит следующим образом. Запи- DieM в разрядной форме выражение (1) как

V V J

(2)

V V V V

b - а (ч .о

V

0.

5 V t- 1 2 гл-1 in и где,Ь I b,,b,..., Ь, J ;

О 16, 0,.../б: ОГ;

-7 г n-i « -it - (X.,od,.,.,a,oiJ - разрядные

векторы, представляющие собой разряд

- разрядные матрицы, представляющие собой разрядное изображение чисел а и об соответственно при n 4.

Тогда значение первого компонен- та. о: искомого вектора It определяется как

1, (fe Г

/ И.

а а

-l,et О

/ 1,- Vt24 ( 1

Ь - 2 а с

(г)

г rf,

общем случае значение каждого 3--го

1-1

,

f

ei

1-1 -1,(й О

СП v,i,

2

-(;- (И

Ь

м

пы, n сумматоров 2, (n-1) мультиплексоров 4, вход 5 первого аргумента, вход 6 второго аргумента и выход разрядов 7 (,2,3,.,,,п) результата устройства.

Работа устройства для реализации зависимости вида

йб

происходит следующим образом. Запи- DieM в разрядной форме выражение (1) как

V V J

(2)

V V V V

b - а (ч .о

V

0.

зо ое изображение чисел Ь, О, с6 соот- ветственно;

5 V t- 1 2 гл-1 in и где,Ь I b,,b,..., Ь, J ;

О 16, 0,.../б: ОГ;

-7 г n-i « -it - (X.,od,.,.,a,oiJ - разрядные

векторы, представляющие собой разряд

Z

«. fti

г I о сх . (У (v;

t г А а oi

1 3

oi ОС

4- 0(.

(3)

b-2

(О Тс) а Ь

к

v(0

Ь г О со

(4)

о, ь О,

40

а в.Торого компонента (v искомого вектора ы - по выражению

2- -a f 2.3а, 1

-1- V /5

2 -а -2 а, у( О

V

Ь Чо

(5)

О, , компонента ъ/. определяется как

2

, й 1

{i-il „-( Hl

а + 2 -а,

1-1

л О

f (() 1, Ь 0

LU,

V ( 1

Ь о .

(6)

в исходном состоянии на входы 5 и 6 устройства подаются соответственно значения b и а. После этого в схеме устройства протекает переходньш процесс, после окончания которого на выходе первого сумь5атора 3 образуется значение За, которое поступает на вторые информационные входы всех мультиплексоров 4 и хр анится до момента подачи на входы 5 и 6 ловьпс аргументов. Кроме того, значение а поступает, на первые информационные входы всех мультиплексоров 4 и со сдвигом на один разряд в сторону млад- ших разрядов на входы первых операндов второго сумматора 3 и первого сумматора-вычитате- ля 2 второй группы. В первом сумма- торе-вычитателе i первой группы реализуется выражение (4), т.е. Ь-2 х X а

поступает на вход второго операнда второго сумматора-вычитателя 1 первой группы. Во втором сумматоре-вы- читателе 1 первой группы реализуется в соответствии с формулой (5) вы ражение - 2. , благо благодаря чему полученное

значение о поступает на вход первого операнда второго сумматора-вычитателя этой же группы, а на знаковом выходе первого сумматора-вычитателя 1 первой группы по выражению (4) образуется значение первого разряда

01результата, которое поступает на управляющие входы первого мультиплексора 4, первого сумматора-вычитателя 2 второй группы и второго сумматора-вычитателя I первой группы. Если значение ей 1, то значение За с второго информационного входа первого мультиплексора 4 поступает на входы вторых операндов второго сумматора 3 и первого сумматора-вычитателя

2второй группы, второй сумматор-вы- читатель 1 и первый сумматор-вычита- тель 2 соответственно первой и второй групп настраиваются на сложение, Когда об О, второй сумматор-вычита- тель I и первый сумматор-вычитатель

2 первой и второй групп настраиваются на вычитание, а значение а с первого информационного выхода первого мультиплексора 4 поступает на входы первых операндов второго сумматора 3 и первого сумматора-вычитателя 2 первой группы.

Далее в первом сумматоре-вычИта- теле 2 второй группы реализуется выражение (5), благодаря чему на его

V /2)

выходе образуется значение а , пос- , тупающее на входы первых операндов

10

даря чему вычисленное значение b с его выхода поступает на вход перв го операнда третьего сумматора-вычи тателя 1 первой группы, а на входе знакового разряда второго сумматора вычитателя I по выражению (5) обра2

зуется значение второго разряда oi

« результата искомого неизвестного

15 Значение поступает на управляющие входы второго мультиплексора 4,трет го сумматора-вычитателя 1 первой и второго сумматора-вычитателя 2 второй групп. В зависимости от значения , равного 1, О, на выхо де второго мультиплексора 4 образуе ся соответственно значение За и а, поступающее на входы вторых операндов третьего сумматора 3 и второго

25 сумматора-вычитателя 2 второй группы, кроме того, третий 1 и второй 2 сумматоры-вычитатели первой и второй групп настраиваются на сложение или вычитание соответственно.

Во втором сумматоре-вычитателе 2 второй группы по выражению (6) вы20

30

числяется значение а

:.( 1

поступающее

35

40

45

50

на входы первых операндов четвертого сумматора 3 и третьего сумматора-вычитателя 2 этой же группы.В третьем сумматоре 3 вычисляется значение а, поступающее на вход второго операнда третьего сумматора-вычитателя 1 первой группь, а в третьем суммато- ре-вычитателе 1 первой группы по выражению (6) вычисляются значение ь , поступающее на вход первого операнда четвертого сумматора-вычитателя i этой же группы, и значение д , пающее на выход третьего разряда 7 результата и на управляющие входы третьего мультиплексора 4 и четвертого I и третьего 2 сумматоров-вычи- тателей первой и второй групп. Аналогичным образом в каждом i-M сумматоре 3, (i-l)-M сумматоре-вычитате- ле 2 второй группы по выражен™ (6) определяются значения а и а , а на выходе i-ro сумматора-вычитателя первой группы образуются по выражетретьего сумматора 3 и второго сумма- 55 (6) значение Ь поступающее на тора-вычитателя 2 этой же .группы.Во

вход первого операнда последующего сумматора-вычитателя 1 - этой же группы, и значение оС; , поступающее на вы

втором сумматоре 3 по выражению (5) вычисляется значение а , которое

поступает на вход второго операнда второго сумматора-вычитателя 1 первой группы. Во втором сумматоре-вы- читателе 1 первой группы реализуется в соответствии с формулой (5) вы ражение - 2. , благо0

даря чему вычисленное значение b с его выхода поступает на вход первого операнда третьего сумматора-вычитателя 1 первой группы, а на входе знакового разряда второго сумматора- вычитателя I по выражению (5) обра2

зуется значение второго разряда oi

« результата искомого неизвестного ,

5 Значение поступает на управляющие входы второго мультиплексора 4,третьего сумматора-вычитателя 1 первой и второго сумматора-вычитателя 2 второй групп. В зависимости от значения , равного 1, О, на выходе второго мультиплексора 4 образуется соответственно значение За и а, поступающее на входы вторых операндов третьего сумматора 3 и второго

5 сумматора-вычитателя 2 второй группы, кроме того, третий 1 и второй 2 сумматоры-вычитатели первой и второй групп настраиваются на сложение или вычитание соответственно.

Во втором сумматоре-вычитателе 2 второй группы по выражению (6) вы0

0

числяется значение а

:.( 1

поступающее

на входы первых операндов четвертого сумматора 3 и третьего сумматора-вычитателя 2 этой же группы.В третьем сумматоре 3 вычисляется значение а, поступающее на вход второго операнда третьего сумматора-вычитателя 1 первой группь, а в третьем суммато- ре-вычитателе 1 первой группы по выражению (6) вычисляются значение ь , поступающее на вход первого операнда четвертого сумматора-вычитателя i этой же группы, и значение д , пающее на выход третьего разряда 7 результата и на управляющие входы третьего мультиплексора 4 и четвертого I и третьего 2 сумматоров-вычи- тателей первой и второй групп. Аналогичным образом в каждом i-M сумматоре 3, (i-l)-M сумматоре-вычитате- е 2 второй группы по выражен™ (6) определяются значения а и а , а на выходе i-ro сумматора-вычитателя 1 первой группы образуются по выраже„р „ (6) значение Ь поступающее на

(6) значение Ь поступающее на

вход первого операнда последующего сумматора-вычитателя 1 - этой же группы, и значение оС; , поступающее на вы

ход i-ro разряд 7 результата и управляющие входы i-ro мультиплексора , i.-ro, (i+l)-ro сумматоров-вычитате- лей 1 и 2 первой и второй групп соответственно, И, наконец, на выходе знакового разряда последнего суммато- ра-вычитателя 1 первой группы образуется значение последнего разряда ГУ, искомого вектора об «,«,,.,, dJj , поступающее на выход последнего разряда 7 результата.

Формула изобретения

Матричное вычислительное устройст- во, содержащее первую группу из п сумматоров-вычитателей, где п-разряд- ность представления аргументов, о т - ли чающееся тем, что, с целью расширения функциональных возможностей, в него введены п сумматоров, вторая группа из (п-2) суммато- ров-вычитателей и (п-1) мультиплексоров, выход i-ro сумматора-вычиогателя первой группы соединен с входом первого операнда (i+l)-ro сумматора-вы- .читателя первой группы ( ,,...,п-1) выход j-ro сумматора (,,,..,n) соединен со сдвигом на i-разрядов в сторону младших разрядов с входом второго операнда (i+l)-ro сумматора- вычитателя первой группы, выход знакового разряда i-ro сумматора-вычита теля первой группы соединен с входом управления сложением-вычитанием (i+l)-ro сумматора-вычитателя первой группы., с входом сумматора-вычи

)

j

0

тателя второй группы (,..,,п-2) и с входом управления двухразряд- ного мультиплексора и является выходом i-ro разряда результата устройства, выход знакового разряда п-го сумматора- вычитателя первой группы является выходом п-го разряда результата устройства, вход первого операнда первого cyNrMaTopa-вычитателя первой группы является входом первого аргумента устройства, вход второго аргумента которого соединен с входом первого операнда первого сумматора, с первыми информационными входами всех мультиплексоров, со сдвигом на один разряд в сторону младших разрядов с входом второго операнда первого сум- матора-Е ычитателя первой группы, с входом первого операнда второго сумматора и с входом первого операнда первого сумматора-вь читателя второй группы, со сдвигом на один разряд в сторону старших разрядов с входом второго операнда первого сумматора, которого соединен с вторыми информационными входами мультиплексоров, выход i-ro мультиплексора подключен со сдвигом на (i+2) разряда в сторону младших разрядов к входам вторых операндов j-ro сумматора и 1 -го сумматора-вычитателя второй группы, выход которого подключен к входам первых операндов f-ro сумматора (f 3,.,п) и g-ro сумматора-вычитателя второй группы (g 2,. о о, п-2),

Редактор И.Николайчук

Составитель А.Ушаков Техред Л.Олейник

2771/50

Тираж 671Подписное

ВНИЖИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, д.4/5

Производственно-полиграфическое предприятие, г о Ужгород, уло Проектная, 4

Корректор ВсБутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Цифровой функциональный преобразователь | 1989 |

|

SU1686438A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для дифференцирования функций | 1986 |

|

SU1335995A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Матричный преобразователь координат | 1988 |

|

SU1559343A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1397904A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

Изобретение относится к вычислительной технике и позволяет вычцс- лять зависимость вида ci ЧЬ/а.Уст- ройство содержит п сумматоров-вычи- тателей первой группы, (п-2) сумматоров вычитателей второй группы, п сумматоров, (п-1) мультиплексоров, где п - разрядность представления информации. Результат вычисления формируется поразрядно на выходах знаковых разрядов соответствующих cy№ia- торов-вычитателей первой группы. ил. (Л

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разрядно-аналоговые вычислительные системы | |||

| - М.: Советское радио, 1978, с.13-35 | |||

| Стасюк А.И | |||

| Однородные многофункциональные матричные процессоры | |||

| Препринт АН УССР | |||

| Ин-т электродинамики, № 351 | |||

| - Киев, 1983, с.38, рис.12. | |||

Авторы

Даты

1986-05-23—Публикация

1984-07-05—Подача