Изобретение относится к вычислительной технике и может быть использовано в качестве спецпроцессора аппроксимации нелинейных зависимостей при решении систем нелинейных алгебраических и дифференциальных уравнений в реальном масштабе времени.

Цель - повьппение быстродействия,

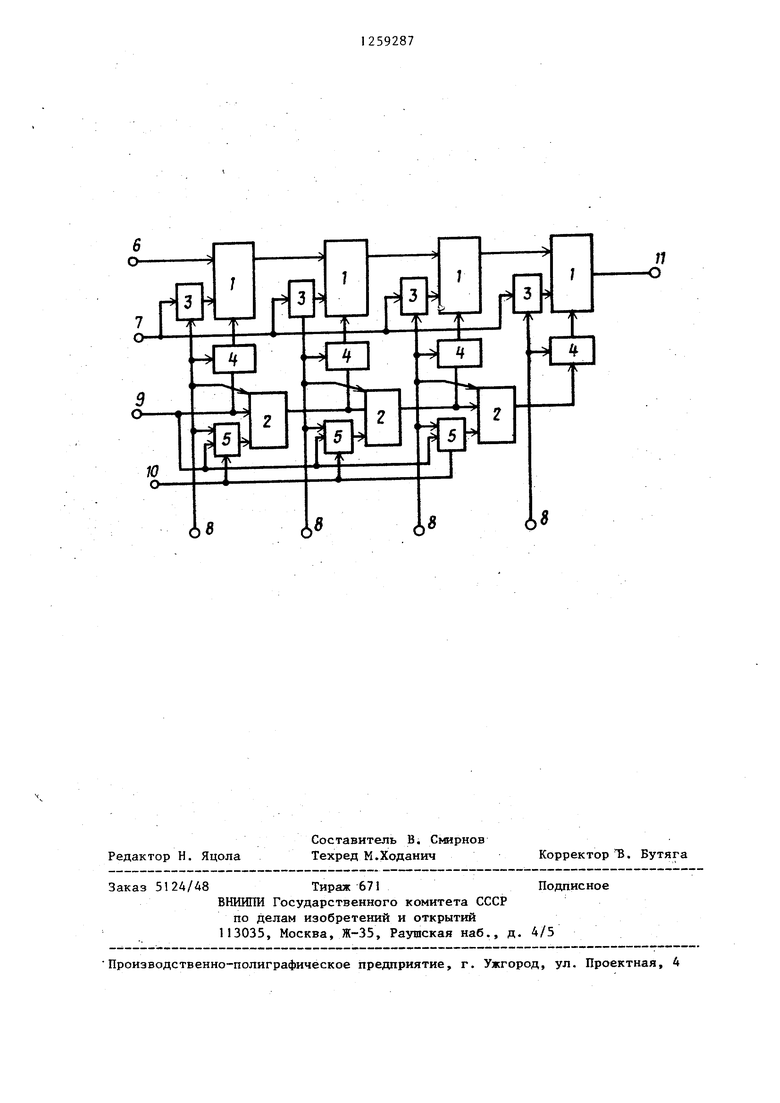

На чертеже показана блок-схема устройства для случая h А.

Устройство содержит сумматоры 1, сумматоры-вычитатели 2, блоки 3 элементов И первой группы, блоки 4 элементов И второй группы, коммутаторы 5, входы 6 свободного члена полинома, входы 7 коэффициентов линейного члена полинома, входы 8 переменных полинома, входы 9 коэффи- циентов нелинейного члена полинома.

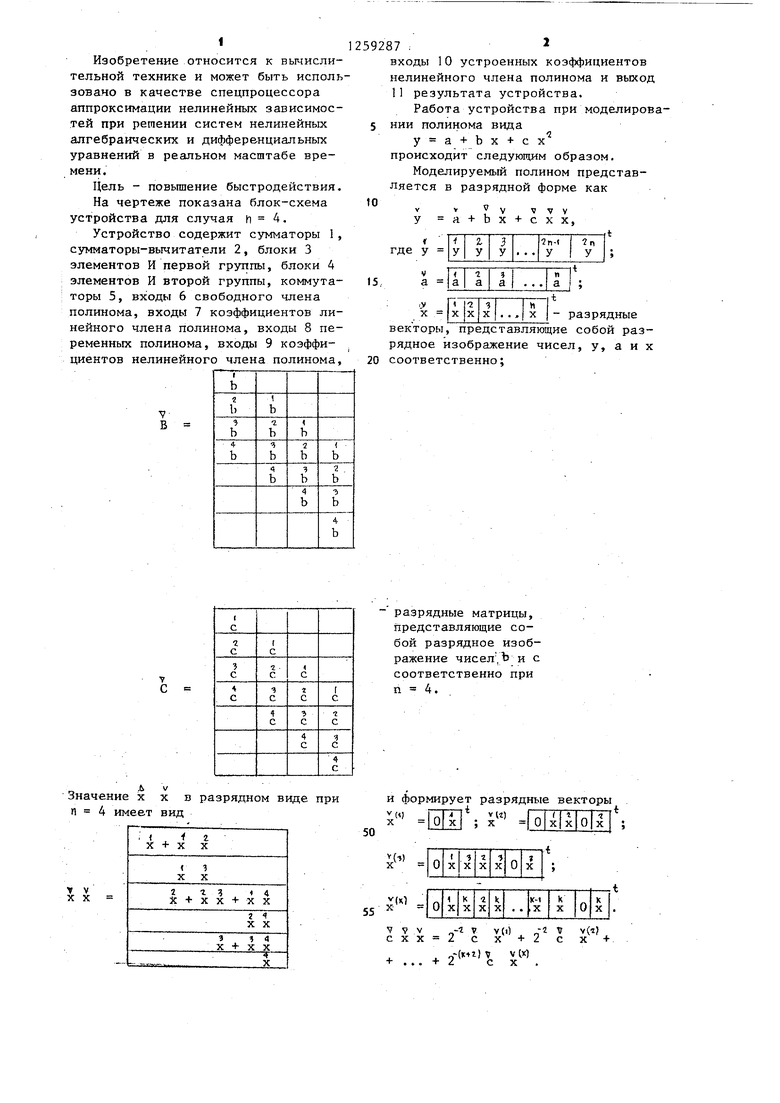

V

С

V

X

Значение х х в разрядном виде при п 4 имеет вид

V V XX

59287 :

входы 10 устроенных коэффициентов нелинейного члена полинома и выход 11 результата устройства.

Работа устройства при моделирова- 5 НИИ полинома вида

у а + Ьх + сх происходит следующим образом.

Моделируемый полином представляется в разрядной форме как

10

а + b X

V V V + с X X,

где

У

V

а

у

X

векторы, представляющие собой разрядное изображение чисел, у, а и х 20 соответственно;

разрядные матрицы, представляющие собой разрядное изображение чисел , Ь и с соответственно при п 4.

и формирует разрядные векторы

50

V.,

о X

55

X

М

V V -г V X X 2 с

... f I

v(0 „-г V X + 2 с

VM

X

v(i X +

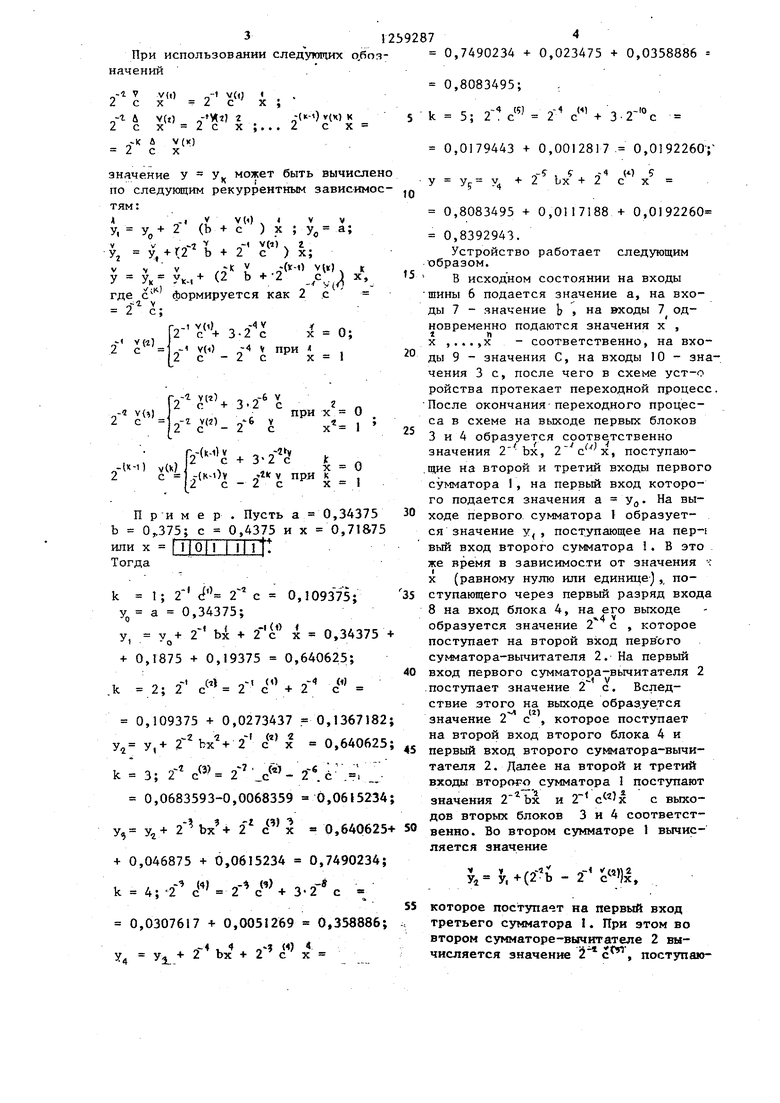

начений

2- I 2- i ; 5 ...

f ;

-(к- ) у(ч) к 2 с X

значение у У может быть вычисле по следукяцим рекуррентным зависимо

тям:

у v() , V V + 2 (b + c )x:v

о

Д-« ,У ( ч

у, 2 (Ь + с ) X ; у а; у, .;;,Г2- Ь 2 ) ;

у-у.-,(,г;.

где формируется как 2 с т

Г2- П 3. х 0; 1

Г2-.Ч3.

-7 у() Iпри

2 с ,.) V Р

Г2 - с+ 3-2 с

,-U-O v(x Г N /

2 с ,-(к-Оу „-гк Vпри

2 с-2с

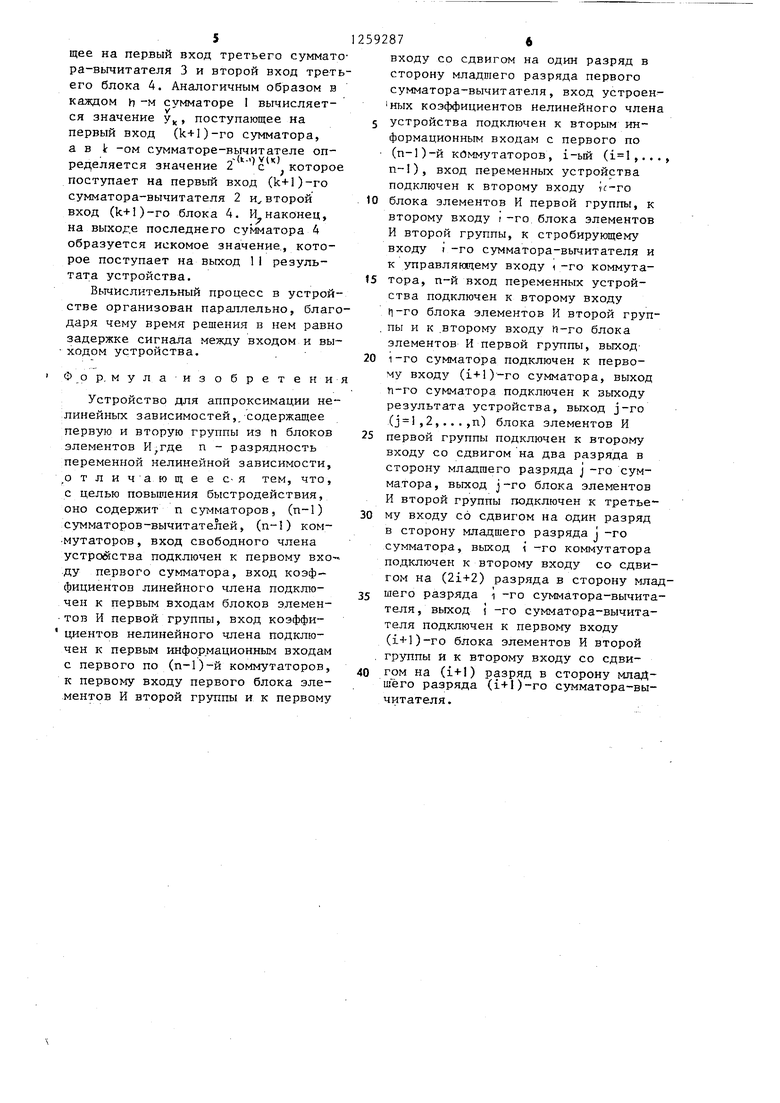

Пример. Пусть а 0,34375

, 0,71875 или X h I 011 I 11 rft

Тогда

k 1 ; 2- с 2 с у а 0,34375;

0,109375; у, у + 2 Ьх + 2 с X 0,34375 +

+ 0,1875 + 0,19375 0,640625; Л 2; 2 с 2- + 2 0,109375 + 0,0273А37 0,1367182;

(1) с

30 ходе первого сумматора I образуется значение у , поступающее на пер- вый вход второго сумматора 1. В это же время в зависимости от значения -: X (равному нулю или единице- , по- 35 ступающего через первый разряд входа 8 на вход блока 4, на его выходе образуется значение 2 с , которое поступает на второй вход первого су{Ф атора-вычитателя 2. На первый

40 вход первого сумматора-вычитателя 2 .поступает значение 2 с. Вследу, у,-. f

kl 3; с« 2 c -VVc

ствие этого на выходе образуется

м «1

значение 2 с , которое поступает

«,,,,„,- на второй вход второго блока 4 и

0.6406251 ff

45 первый вход второго сумматора-вычитателя 2. Далее на второй и третий входы второго сумматора 1 поступают

0,0683593-0,0068359 0,0615234;

значения и 2 с выходов вторых блоков 3 и 4 соответст- у. у + 2 Ък+ 2 с X 0,640625+ 50 венно. Во втором сумматоре 1 вычис- -

i О) 3

, .( ),

+ 0,046875 + 0,0615234 0,7490234;

k 4;-2 c 2- cr43. -, - .

55которое поступает на первый вход

0,0307617 + 0,0051269 0,358886; .третьего сумматора 1. При этом во

-I (« 4втором сумматоре-вычитателе 2 выу УЗ + 2 Ьх + 2 с X числяется значение 2 с, поступаю 0,8083495;

k 5; 2- 3.2-%

0,0179443 0,0012817- 0,0192260-;УГ 4

Х- , f „-ч W 5 +2 Ьх+2 с X

0,8083495 + 0,0117188 + 0,0192260

0,8392943.

Устройство работает следующим образом.

В исходном состоянии на входы шины 6 подается значение а, на входы 7 - значение Ь на В Ходы 7 одновременно подаются значения х , X ,...,х - соответственно, на входы 9 - значения С, на входы 10 - значения 3 с, после чего в схеме уст-о ройства протекает переходной процесс. После окончания переходного процесса в схеме на выходе первых блоков 3 и 4 образуется соответственно значения 2 Ьх, 2 х, поступаю- .щие на второй и третий входы первого сумматора I, на первый вход которого подается значения а у. На выходе первого сумматора I образуется значение у , поступающее на пер- вый вход второго сумматора 1. В это же время в зависимости от значения -: X (равному нулю или единице- , по- ступающего через первый разряд входа 8 на вход блока 4, на его выходе образуется значение 2 с , которое поступает на второй вход первого су{Ф атора-вычитателя 2. На первый

вход первого сумматора-вычитателя 2 .поступает значение 2 с. Вследляется значение

, .( ),

, -

51

щее на первый вход третьего суммато- ра-вьгчитателя 3 и второй вход третьего блока 4. Аналогичным образом в каждом h м сумматоре I вычисляется значение у, поступающее на первый вход (k+I)-ro сумматора, а в Jf -ом сумматоре-вычитателе (k-)V(K)

ределяется значение 2 с которое поступает на первый вход (k+)-ro сумматора-вычитателя 2 и второй вход (k+l)-ro блока 4, И наконец, на выходе последнего сумматора 4 образуется искомое значение., которое поступает на выход 11 результата устройства.

Вычислительный процесс в устройстве организован параллельно, благодаря чему время решения в нем равно

задержке сигнала между входом и вы- ходом устройства.

Фор, мула-изобретения

Устройство для аппроксимации нелинейных зависимостей,, Содержащее первую и вторую группы из п блоков элементов п - разрядность переменной нелинейной зависимости, отлич ающеес-я тем, что, с целью повышения быстродействия, оно содержит п сумматоров, (п-1) сумматоров-вычитателей, (п) ком- мутаторов, вход свободного члена устройства подключен к первому вхо- ду первого сумматора, вход коэффициентов линейного члена подключен к первым входам блоков элемен- тов И первой группы, вход коэффи- циентов нелинейного члена подключен к первым информационным входам с первого по (п-1)-и коммутаторов, к первому входу первого блока элементов И второй группы и к первому

592876

входу со сдвигом на один разряд в сторону младшего разряда первого сумматора-вычитателя, вход устроен- ных коэффициентов нелинейного члена 5 устройства подключен к вторым информационным входам с первого по (п-1)-й коммутаторов, i-ый (,..., п-1), вход переменных устройства подключен к второму входу с-го

10 блока элементов И первой группы, к второму входу i-го блока элементов И второй группы, к стробирующему входу I -го сумматора-вычитателя и к управляющему входу -го коммута15 тора, п-й вход переменных устройства подключен к второму входу fl-ro блока элементов И второй группы и к .второму входу и-го блока элементов И первой группы, выход20 1-го сумматора подключен к первому входу (i+l)--ro сумматора, выход п-го сумматора подключен к выходу результата устройства, выход j-ro .(j ,2,.. . ,п) блока элементов И

25 первой группы подключен к второму входу со сдвигом на два разряда в сторону младшего разряда j -го сумматора, выход j-ro блока элементов И второй группы подключен к третье30 му входу со сдвигом на один разряд в сторону младшего разряда j -го сумматора, выход i -го коммутатора подключен к второму входу со сдвигом на (2i.+2) разряда в сторону млад5 шего разряда i -го сумматора-вычитателя , выход i -го сумматора-вычитателя подключен к первому входу (i-i-l)-ro блока элементов И второй , группы и к второму входу со сдви0 грм на (i+l) разряд в сторону млаД- шего разряда (i+l)-ro сумматора-вычитателя.

Редактор Н. Яцола

Составитель В. Смирнов Техред М.Ходанич

Заказ 5124/А8Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор В. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298764A1 |

| Параллельное устройство для решения квадратного уравнения | 1984 |

|

SU1249532A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Устройство для дифференцирования функций | 1986 |

|

SU1335995A1 |

| Асинхронный матричный вычислитель обратных тригонометрических функций | 1982 |

|

SU1132286A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1983 |

|

SU1265793A1 |

| Цифровое параллельное устройство для возведения в куб | 1984 |

|

SU1196859A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве спецпроцессора аппроксимации нелинейных зависимостей при решении систем нелинейных алгебраических и дифференциальных уравнений в реальном масштабе времени. Цель изобретения - повышение быстродействия. Устройство содержит п сумматоров,(п-1) суммато- ров-вычитателей (где И .- разрядность переменной нелинейной зависимости |, две группы из ti блоков элементов И и п коммутаторов. Указанная совокупность признаков позволяет достигнуть цели изобретения. 1 ил. с (g (Л

| СПОСОБ ЭЛЕКТРОШЛАКОВОЙ СВАРКИ | 0 |

|

SU318442A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения квадратичных функций | 1977 |

|

SU710039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1984-12-26—Подача