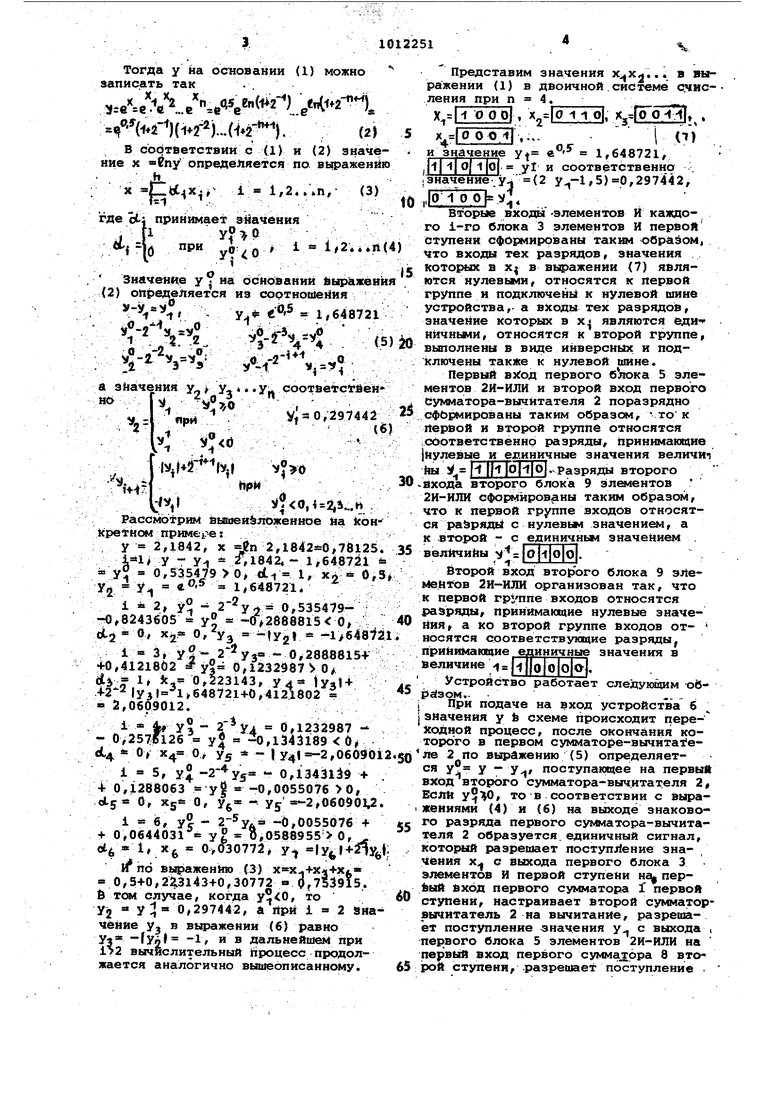

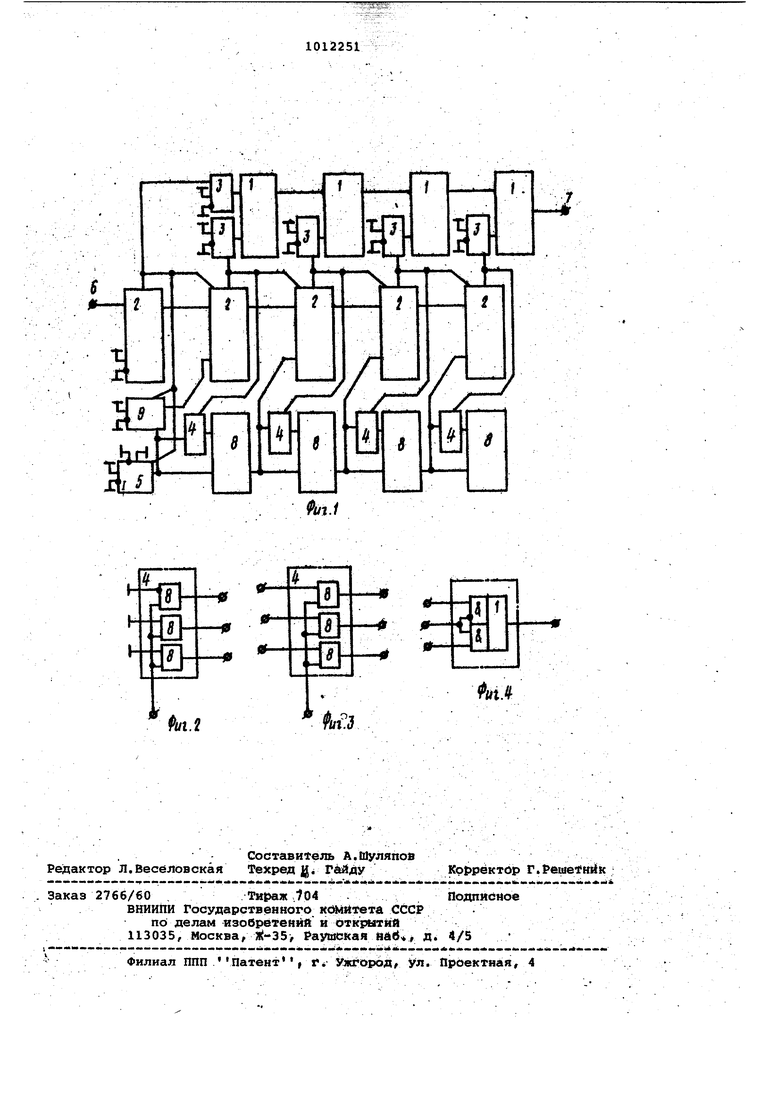

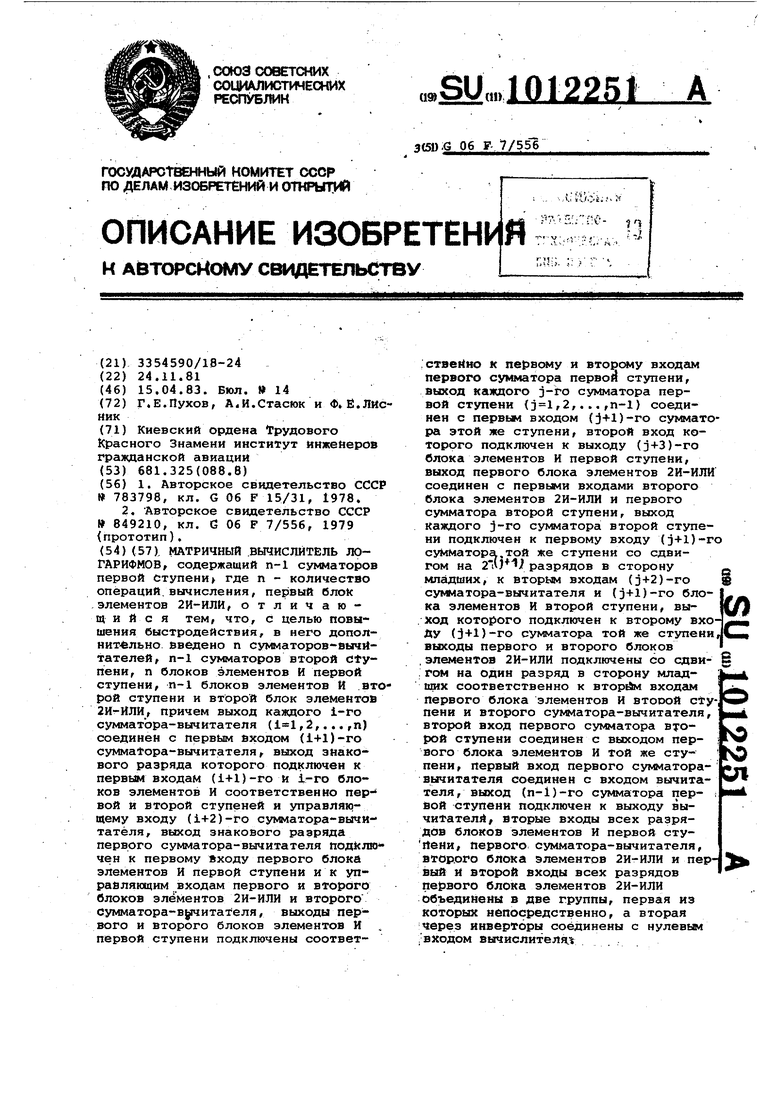

Изобретение относится к вычислительной технике и может быть применено в качестве спецпроцессора в ком лексе с цифровой вычислительной машиной Для оперативного вычисления натуральных логарифмов чисел. Известно устройство, содержащее регистр аргумента, сумматор результата, блок сдвига, блоки постоянной памяти, регистры разрядных цифр, сум маторы разрядных цифр, счетчики поло жительныхи отрицательных единиц Недостатком известного устройства являются низкое быстродействие, определяемое тем, что вычислительный процесс организован в вчде после довательности шагов, а также относительная сложность управления вычислительным процессом, связанная с на личием блоков постоянной . . Наиболее близким к предложенному по технической сущности является ус ройство для вычисления логари а, содержащее четыре сумматора, блок управления, блок сдвига, шифратор., три регистра, дешифратор и два прео разователя кода Недостатком известного устройств является низкое быстродействие, определяемое последовательной организацией вычислительного процесса и сложностью управления. Цель изобретения - увеличение быстродействия. Цель достигается тем, что в матричный вычислитель логарифмов, со- держащий п-1 сумматоров первой ступени, где п - количество вычисления, первый блок зЛёментов 2И-ИЛИ, дополнительно введено п сум ма торов-вычитателей, п-1 сумматоров второй ступени, п блоков злементов И первой ступени, п-1 блоков элемен тон И второй ступени и второй блок элементов 2Й-ИЛИ, причем выход кажд го i-ro сумматора-вычитателя (1 1,2,...,п) соединен с первьм входом (1+1)-го сумматора-вычитателя выход знакового разряда которого по ключей .к nepSbtoi входам (1+1)-го и 1-го блоков элементов И соответственно первой и второй ступеней и упргшляйядему входу (1+2)-го сумиато ра-вычитателя, выход знакового разряда первого сумматора-вычитателя подключен к первому входу первого блока злементов И первой ступени и к управляющим входам первого и втот рого блоков элементов 2И-ИЛИ и вто рого сумматора-вычитателя, выходы первого и второго блоков элементовъ первой ступени подключены сгбОтВетст йенно к первому и второму входам первого сумматора первой ступени, выход каждого j-ro сумматора первой ступени (J 1,2,.,.,п-1) соединен с первым входом (j+l)-ro сумматора эт же ступени, второй вход которого по ключен к выходу (j+3)-ro блока элементов И первой ступени, выход первого блока элементов 2И-ИЛИ соединен с первыми входами второго блока элементов 2И-ИЛИ и первого сумматора второй ступени, выход каждого j-ro сумматора второй ступени подключен к первому входу (j+l)-ro сумматора той же ступени со сдвигом на 2() разрядов в сторону младшИх, к вторьм входам (j+2)-ro сумматоравычитателя и (j+l)-ro блока элементов И второй ступени, выход которого подключен к второму входу (j+l)-ro сумматора той же ступени, выходы первого и второго блоков злементов 2И-ИЛИ подключены со сдвигом на один разряд в сторону младших соответственно к вторьм входам первого блока элементов И второй ступени и второго сумматора-вычитателя, второй вход первого сумматора второй ступени соединен с выходом первого блока элементов И той же ступени, первый вход первого сумматора-вычитателя соеди- ; иен с входом вычислителя, выход (n-l)-ro сумматора первой ступени . подключен к выходу вычислителя, вТорые входы всех разрядов блоков элементов И первой ступени, первого сумматора-вычитаТеля, второго блока элементов 2И-ИЛИ и первый и второй входы всех разрядбв первого блока элементов объединены в две группа. Первая из.которых непойрбдственно, а вторая через инверторы соединены с нулевым вхОдом вычислителя. I, . На фиг. 1 приведена схема йат{)ич:- . нрго вычислителя логарифмов; на фиг.2 и 3 - конструкция блока элементов И первой И второй ступени соответственно (вариант исполнений); на фиг.4 разряд элементов 2И-ИЛЙ (вариант исполнения). Матричный .выч1ислитель логарифмов {фиг.1) Содержит сумматоры 1 первой ступени сумматоры-вычитатели 2, . блок 3 элементов И первой ст5тени блок 4 элементов И второй Первый блок 5 элементов 2 И-ИЛИ, вход 6 устройства/ выход 7 устройства, су14латорь1 8 второй ступени второй блок 9 элементов 2И-ИЛИ; Матричный вычислитель логарифмов X пу работает следующим образом. величина X может быть представлена в виДе суммы X x.+x-+., .+Х| где х 0,5; х-« гп{1+2) 0,405465; х en(lf2-2) „ 0,223143; х tn(l+2) 0,117783; (1) kT еп{1+2:) 0,06024; х €п(1+2 Ь. Тогда у йа основании (1) можно записать так (.. (()...(. (2 в соотаетствии с (1) и (2) энач ние X Рпу определяемся по. вь ражен - X L.tttjX.j i « l,2..n, (3 1. -, .-/ .; - : где oti принимает эйачения i i,. |б Р« Значение у на 6сно1ваний выраже (2) определяется из срртношейия -у,;, Ул 1,64872 -«О f . 1 г 2 U л п; 2 - .. у. соотве с1г1ё y|s 0,29744 ,U2,i..h Рассмотрим вьааенёяоженное На kO kpeTHOM примере: у 2,1842, X ,7812 1842,- 1,648721 У - У - 2; If у° 0,535479 О, 4 1, X 1,648721. i «2 . У -2-у, 0,535479-0,8243605 yj -0 2888815 О, О,УЗ 1У21 О, Xj-1 648О 52 - 0,2888815+ - 3, +0,4121862 .у2 0,1232987 У 0 di 1 1 3t - 0,223143, у 4 1Уз -««-2-2 |уз1 1 648721+0,4l2ia02 2,06019012. 0,1232987 Ш26 у -0,2571 -0,1343189 0 0,4 О Х4 О, Уд - -2,0609 i S, yj-2- У5« - 0,13431 9 + 4-0,1288063 yg « -0,0055076 О, cLy « О, xgfe О, y - уу -2 ,06090, i - б, у - -6,0055076 + + 0,0644031 « у D,0588955 О, т и,ооччиал У и, х и, 6 1 X 0,030772, У I ho выражению (3) V AVMl lbniVirAA - -mf fVb4П ЪК «JK 0,5+0,2i2.3l43+0,30772e 0,753915. 6 TOM случае, когда , то У2 У 0,297442, а При 1 2 у в выражении (6) равно чёние УЗ fyof -1, ив дальнейшем при 172 вычислительный процесс продолжается аналогично вышеописанному. Представим значения ..; в выражении (1) в двоичной .системе с.числения при п 4. oooj. х оТТо}, . x |000/tf..,.1 О) . и значение у 1,648721, iHrZEllo У соответственно . значение y-j (2 ,5) 0,297442, o ooiV . Вторые входа -элементов И казидого i-ro блока 3 элементов И nepsoft ступени сформированы таким -образом, что входы тех разрядов, значения которых в Х{ в вьфажении (7) являются нулевьми, относятся к первой группе и подключень к нулевой шине устройства,- а входы тех разрядов, значение которых в Xj являются единичными, относятся к второй группе, выполнены в виде инверсных и подkлючeны также к нулевой шине. Первый первого блока 5 элементов 2И-ИЛИ и второй вход первого Сумматора-вычйтателя 2 поразрядно сформированы таким образе, -то к пер&ой и второй группе относятся соответственно разряды, принимающие 1нулевые и единичные значения величи- Ьы 3 р|И |ОИГо|- Разряды второго входа второго блока 9 элементов 2И-ИЛИ сформированы таким образе), что к первой группе входов относятся разряды с нулевым значением, а к второй - с единичные значением вёлйчийы |о -||о|о|. 4 . f Второй ВХОД второго блока 9 эЛеМе.йтов 2И-ИЛИ организован так, что к первой группе входов относятся разряды, принимающие нулевые значения, а ко второй группе входов от- v носятся соответствующие разряды принимающие единичные значения в величине (jp|р |o|o.j. Устройство работает следующим образом.-.. При подаче на вход устройства 6 значения у Ь схеме происходит пере- Ходкой процесс, после окончания которого в первом сумматоре-вычитахеле 2 по выражению 5) определяется yjs у - У, поступающее на первый вход второго сумматора-вычитателя 2, Если , то в соответствии с выражеииями (4) и (6) на выходе знакового разряда первого сумматора-вычитателя 2 образуется, единичный сигнал, который разрешает поступд1ение значения х с выхода первого блока 3 элементов И первой ступени нг первый Вход первого сумматора Г первой ступени, настраивает второй сумматорвычитатель 2 на вычитание, разрешает поступление значения с выхода , первого блока 5 элементов 2И-ИЛИ на первый вход первого сумма,трра 8 вто рой ступени, -разрешает поступление . значения 2 y с выхода первого блока 5 элементов 2И-ИЛИ на второй вход первого блока 4 элементов И второй ступени и значения 2 у через второй блок 9 эле(ентов 2 И-ИЛИ на второй вход второго сумматора-вычитателя 2. Во втором сумматоре-вычитателе 2 по выражению (5) определяется значение у у - , которое поступает на первый вход третьего сумматора-вычитателя 2. В зависимости от значения У2( или ) по выражениям (4) и (6) на выходе знаково го разряда второго сумматора-вычитателя 2 образуется сигнал, поступающий на второй 3 и первый 4 блоки элементов И первой и второй ступени соответственно и на управляющий вход третьего сумматора-вычитателя 2, настраивая его на сложение или вычитание. При этом в первом сумматоре 1 первого блока реализуется сумма значений х и XT поступающих с выходов первого и второго блоков 3 элементов И первой ступени, В сумматоре 1 второй ступени реализуется сумма значений у и которая поступает на вход второго сумматора этой же ступени. В третьем сумматоре-вычитателе 2 по выражению (5) вычисляется значение у уS- , поступак«цее на вход Четвертого сумматора-вычитателя 2. На выходе знакового разряда третьего сумматора-вычитателя 2 образуется сигнал, который в соответствии с (4) и (6) разрешает поступление значения х с выхода третьего блока 3 элементов И первой ступени на второй вход второго сумматора 1 этой же ступени, разрешает поступление суммы у-, с выхода перво го сумматора 8 второй ступени через второй вход второго блока 4 элементов И этой же ступени на второй вход второго сумматора 8 второй ступени со сдвигом на два разряда в сторону младших разрядов, т.е.2(у + + 2 У-|) , и настраивает последукиций .сумматорг-вычитатель 2 на режим сложения или вычитания. Во втором сумм торе 1 первой ступени реализуется сумма () с Xj по выражению (3) а во втором сумматоре 8 второй ступени в соответствии с (6) суммирует ся значение со значением 2 (у ) . Аналогичным образом в i-M сумматоре-вычитателе 2 реализуется выражение (5) у9 У значение у поступает на вход (i+1)-гоiсумматора-вычитателя 2, а на выходе знакового разряда i-ro сумматора-вычитателя 2 образуется .сигнал, который настраивает (i+1)-и сумматор-вычитатель 2 на сложение или вычитание и в соответствии с ыражением (4) разрешает поступление значения х На вход (±-1)-го сумМатора 1 первой ступени, благодаря ему в нем реализуется выражение (3). Кроме того, сигнал с выхода знаKoBOl-o разряда i-гр сумматора-вычитателя 2 вьщаёт разрешение на (1-1)-и блок 4 элементов И второй ступени, благодаря чему в (i-l)-M С5 мМаторе 8 этой же ступени реализуется выражение (б). По аналогии с вышеописанньм в п-м сумматоре-вычитателе 2 реализуется выражение (5) , а на выходе знакового разряда его Образуется сигнал, который по выражениям (4) и (6) разрешает поступление значения х с выхода п-го блока 3 элементов И первой ступени на вход последнего сумматорй I этой же ступени, на выходе которого и соответственно на выходе устройства 7 по выражению (3) образуется искомое значение х Рг у. В том случае, когда на выходе знакового разряда первого сумматора-вычитателя 2 образуется нулевой сигнал, то он настраивает второй cyNWaTop-выЧитатель 2 на режим сложения, разрешает поступление на его второй вход значение с выхода второго блока 9 элементов 2И-ИЛИ и разрешает поступление значения единицы и 0,5 с выхода первого блока 5 элементов 2И-ИЛЙ на первый и второй входы первого сумматора 1 и первого блока 4 элементов И первой ступени соответственно . Далее вычислительный процесс продолжается аналогично вышеописанному. Таким образом, в предложенном устройстве в отличие от прототипа, в котором вычислительный процесс организован в виде последовательности шагов, результат вычислений осуществляется за йремя Переходного процесса в схеме, которое практически равно времени задержки сигнала между входом и выходом устройства. Кроме того, в отличие от прототипа, в котором усложнена организация вычислительного процесса и увеличено количество управленческой информации, в данном устройстве не используется управленческая информация, а вычислительный процесс начинается с момента подачи на йходную шину исходной информации у. Устройство может быть применено для реализации .вычислительного процесса в натуральном масштабе времени, например, управления технологическими процессами или динамическими обоэктами в режиме их нормального функционирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель гиперболических функций | 1982 |

|

SU1149251A1 |

| Матричный вычислитель | 1985 |

|

SU1283791A1 |

| Матричный вычислитель | 1985 |

|

SU1265765A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Асинхронный матричный вычислитель обратных тригонометрических функций | 1982 |

|

SU1132286A1 |

| Устройство для деления | 1986 |

|

SU1381492A1 |

| Матричное устройство для решения дифференциальных уравнений в частных производных | 1982 |

|

SU1120346A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

. МАТРИЧНЫЙ .ВЫЧИСЛИТЕЛЬ ЛОГАРИФМОВ, содержащий п-1 сумматоров первой ступени где п - количество операций, вычисления, первый блок .элементов 2И-ИЛИ, о тлич ающ и и с я тем, что, с целью повышения быстродействия, в него дополнительно введено п сумматоров-вычйтателей, п-1 сумматоров второй ступени, п блоков элементов И первой ступени, п-1 блоков элементов И второй ступени и второй блок элементов 2И-ИЛИ, причем выход каждого i-ro сумматЬра-вычитателя (,2,...,п) соединен с первым входом

.3

t.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления логарифма | 1979 |

|

SU783798A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1981-11-24—Подача