1249532

Изобретение относится к вычисли- и Ь при и (м - разрядность представления информации),

Запишем произведение разрядной

V„V

матрицы X на разрядный вектор х в

тельной технике и может применяться автономно и в системах автоматического управления динамическими объектами или техническими процессами. 5 развернутом виде при п 4 как

Цель изобретения - расширение функциональных возможностей за счет реализации решения полного неприведенного квадратного уравнения вида охЧ Ьх + с 0.10

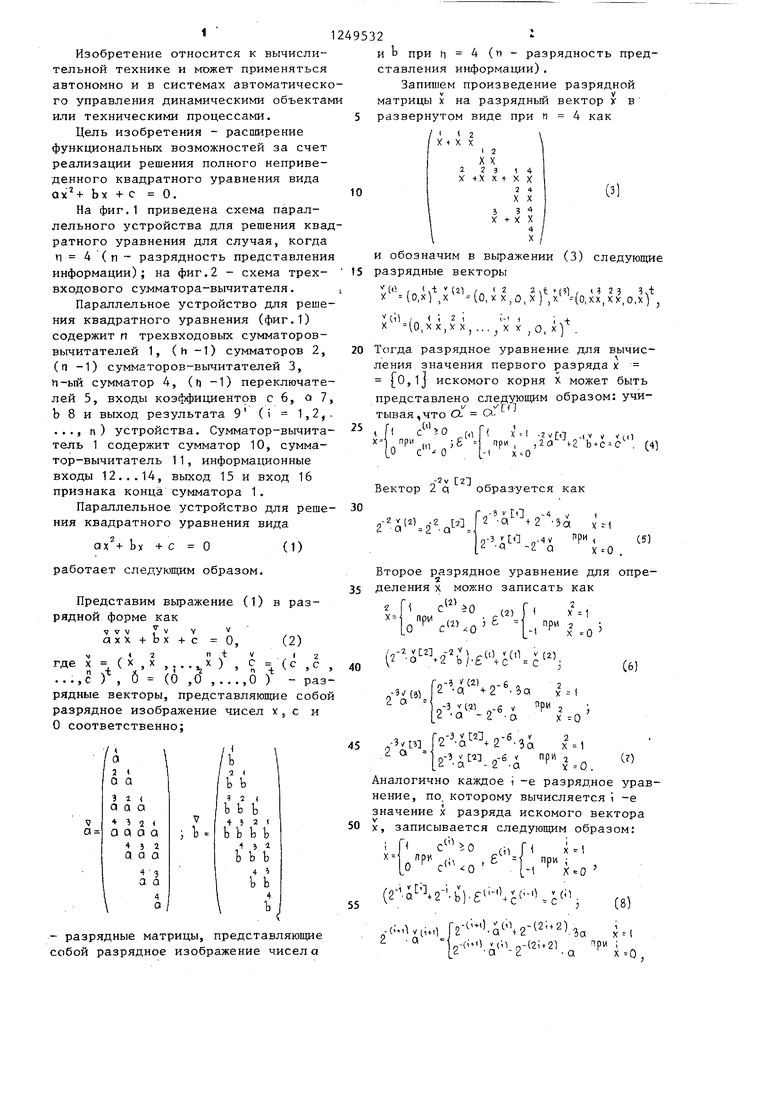

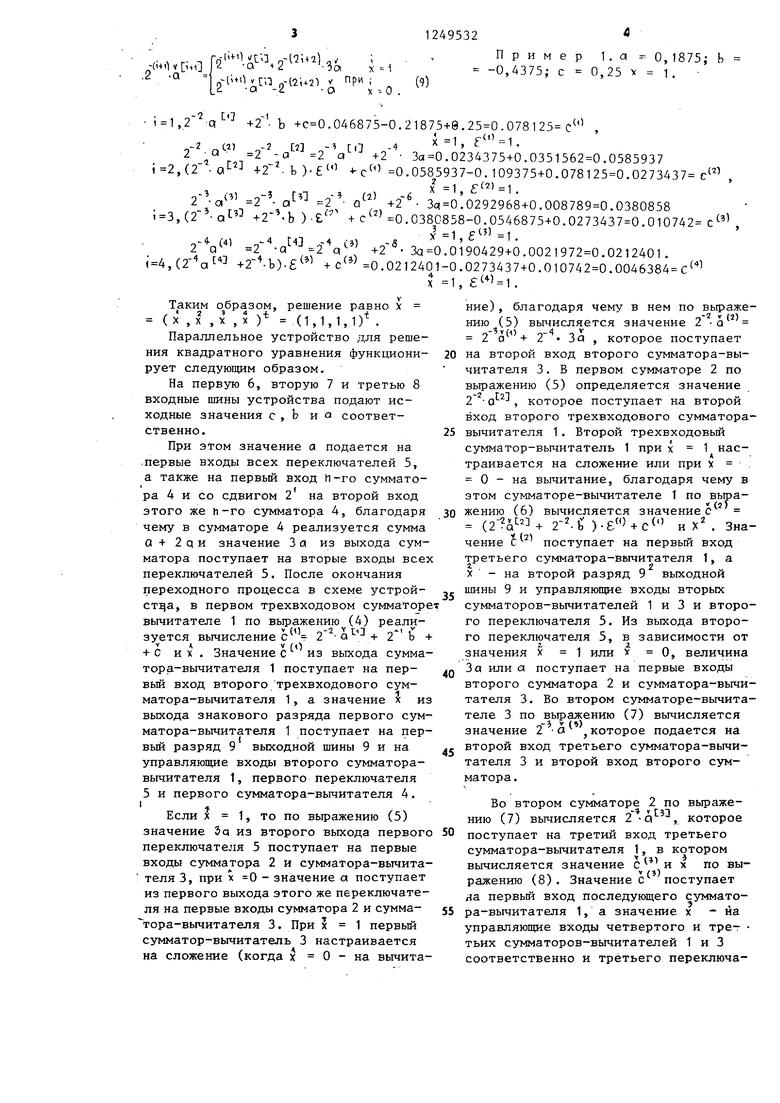

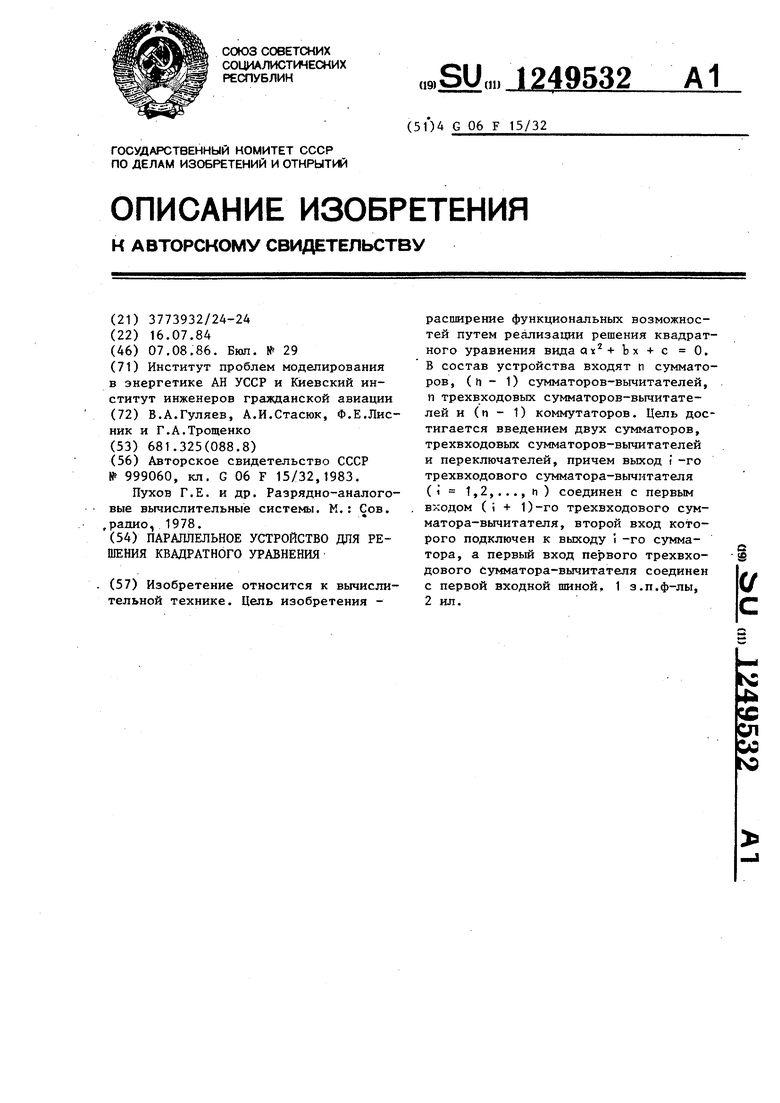

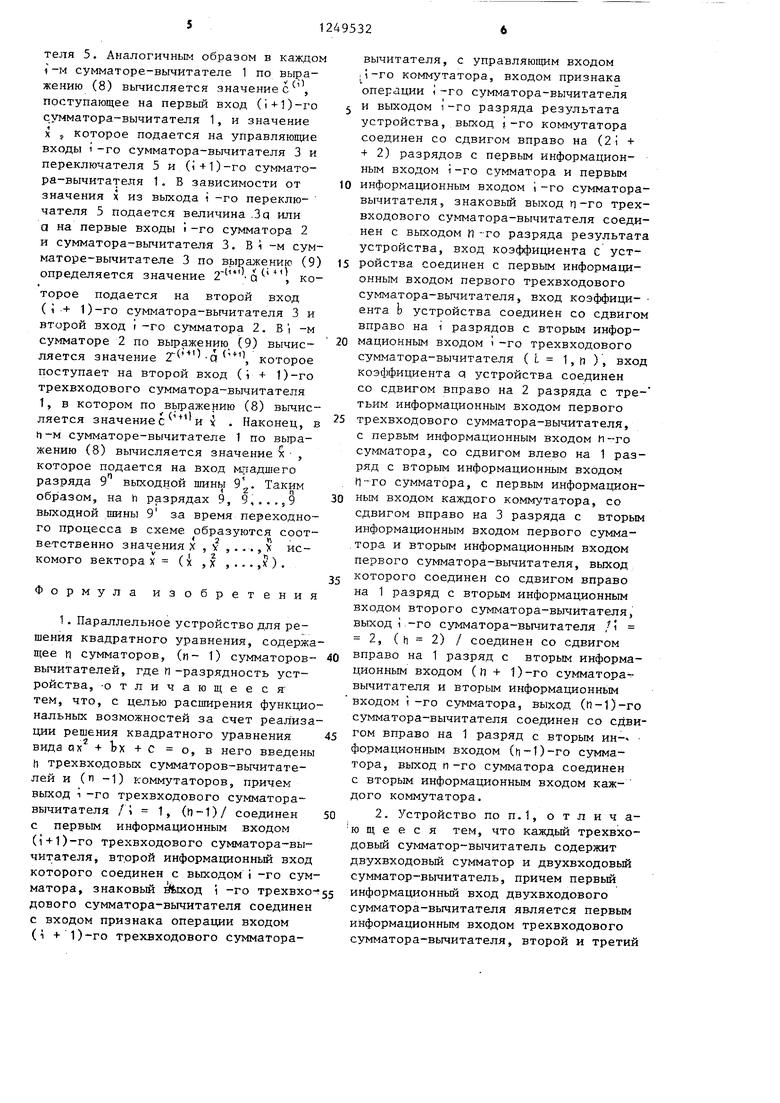

На фиг,1 приведена схема параллельного устройства для решения квадратного уравнения для случая, когда п 4 (п- разрядность представления и обозначим в выражении (3) следующие информации); на фиг.2 - схема трех- tS разрядные векторы входового сумматора-вычитателя. i I ,. г„ , (2i „ i2 a.tvf) , 23 .t

/I f 2

x + X X

I 2

X X

i 2 3 (4

X -tX X + X X

2 4

X X

} 3

X + X X

4 X

(3)

4o,x)(o,ix,o,xr.; 4o,xx,o,f,

4o,x)(o,ix,o,xr.; 4o,xx,o,f,

( ; 2 1 ;-i ( ;

X (0,Х «Л , -.. ; X X 0, X) .

Параллельное устройство для решения квадратного уравнения (фиг.1) содержит п трехвходовых сумматоров- вычитателей 1, (h -1) сумматоров 2, 20 Тогда разрядное уравнение для вычис- (П -1) сумматоров-вычитателей 3, ления значения первого разрядах П-ый сумматор 4, (п -1) переключате- 0,l искомого корня X может быть лей 5, входы коэффициентов с 6, о 7, представлено следутощим образом: учиb 8 и выход результата 9 (i 1,2,тывая,что Л О..

. СП

..., п) устройства. Сумматор-вычита- 5 Г( 01 г, тель 1 содержит сумматор 10, сумма- х | при ц, ;6 при, ,2а f2 . (4) тор-вычитатель 11, информационные

входы 12... 14, выход 15 и вход 16 признака конца сумматора 1.

Параллельное устройство для реше- НИН квадратного уравнения вида

Ьх + с О (1) работает следующим образом.

Представим вьфажение (1) в разрядной форме как

V V V , V V

ахх+Ьх+с 0,

(2)

35 деления х можно записать как г fl с JO „, fi %, .o 1/Р%чЬ

х

п t

- разрядные матрицы, представляющие собой разрядное изображение чисел а

Запишем произведение разрядной

V„V

матрицы X на разрядный вектор х в

развернутом виде при п 4 как

нии (3) след a.tvf) , 23

4

4

X

X

4 X

(3)

обозначим в выражении (3) следующие азрядные векторы I ,. г„ , (2i „ i2 a.tvf) , 23 .t

4o,x)(o,ix,o,xr.; 4o,xx,o,f,

огда разрядное уравнение для вычис- ения значения первого разрядах 0,l искомого корня X может быть редставлено следутощим образом: учи ( ; 2 1 ;-i ( ;

X (0,Х «Л , -.. ; X X 0, X) .

огда разрядное уравнение д ения значения первого разр 0,l искомого корня X мо редставлено следутощим обра

Тогда разрядное ура ления значения перв 0,l искомого ко представлено следуто

тывая,что Л О..

. СП

Г( 01 г, х | при ц, ;6 при,

-2v C2l

Вектор 2 q образуется как

2%М

-3 V Л ,4 V (

2 -а +2 За х-ч

,-3 LO .,-4 2 -о -2 Q -,Q

С5)

Второе разрядное уравнение для опре2

.-(-Ь,., ..2) ,, , при,

.и,

V. .o.

X i

,2-.

-2

2 Q

,(2-. a

+2 b .046875-0.21875+9..078125 c

i 1

-2 7 - (-4л I , с - I .

r, ; 2 2 .0234375+0.0351562 0.0585937

C2J j.9-Z L . с (О j, „()

W)

+ 2

2-.0, 2-. a

,-} . -3

. b). 1

.3,(2- -at +2

2

+-C

(2)

,1).

С -о-.

b). 4

a + с

0.0585937-0. 109375+0.078125 0.0273437 c

,.

+ 2 .0292968+0.008789 0.0380858 0.0380858-0.0546875+0.0273437 0.010742

4,(

+2

,-e

,

+2

2-% b). + 0.0212401-0.0273437+0.010742 0.0046384 c

3(.0190429+0.0021972 0.0212401. 01-0.0273437- X 1, .

Таким образом, решение равно X (X , X ,х ,х ) (1,1,1,1) .

Параллельное устройство для решения квадратного уравнения функционирует следующим образом.

На первую 6, вторую 7 и третью 8 входные шины устройства подают исходные значения с, b и а соответственно.

При этом значение а подается на .первые входы всех переключателей 5, а также на первьй вход и-го сумматора 4 и со сдвигом 2 на второй вход этого же h-го сумматора 4, благодаря чему в сумматоре 4 реализуется сумма Q + 2 q и значение 3 а из выхода сумматора поступает на вторые входы всех переключателей 5. После окончания переходного процесса в схеме устрой- CTiqa, в первом трехвходовом сумматоре вычитателе 1 по выражению (4) реализуется вычисление с 2 - а - + b +

ч ч.V fO

+ С их. Значение с из выхода сумматор а-вычитателя 1 поступает на первьй вход второго трехвходового сум- матора-вычитателя 1, а значение х из выхода

матора-вычитателя

вьй разряд 9 выходной шины 9

знакового разряда первого сум- 1 поступает на пери на

управляющие входы второго сумматора- вычитателя 1, первого переключателя 5 и первого сумматора-вычитателя 4.

Если X 1, то по выражению (5) значение За из второго выхода первого переключателя 5 поступает на первые входы сумматора 2 и сумматора-вычитателя 3, при X 0 - значение а поступает из первого выхода этого же переключателя на первые входы сумматора 2 и сумма- тора-вычитателя 3. При х 1 первьй сумматор-вычитатель 3 настраивается на сложение (когда х О - на вычита.

i

(9)

1249532

Приме -0,4375; с

P 1 . a 0,25 X

0,1875; Ь 1.

2 .0234375+0.0351562 0.0585937

()

2)

0.0585937-0. 109375+0.078125 0.0273437 c

,.

+ 2 .0292968+0.008789 0.0380858 0.0380858-0.0546875+0.0273437 0.010742 с

+2

,-e

,

0.0212401-0.0273437+0.010742 0.0046384 c

3(.0190429+0.0021972 0.0212401. 01-0.0273437- X 1, .

0

5

0

5

0

5

ние), благодаря чему в нем по выраже нию (5) вычисляется значение 2 -а 2 а + 2 За , которое поступает

0 на второй вход второго сумматора-вычитателя 3. В первом сумматоре 2 по вьфажению (5) определяется значение , которое поступает на второй вход второго трехвходового сумматора

5 вычитателя 1. Второй трехвходовьй сумматор-вычитатель 1 при х траивается на сложение или О - на вычитание, благодаря чему в этом сумматоре-вычитателе 1

1 насА

при у

по вьфажению (6) вычисляется значение с . 2-.- ).« +С ( +

чение С поступает

и X . Зна- на первьй вход 1, а

третьего сумматора-ввгчитателя X - на второй разряд 9 выходной шины 9 и управляющие входы вторых сумматоров-вычитателей 1 и 3 и второго переключателя 5. Из выхода второго переключателя 5, в зависимости от значения х 1 или х 0, величина За или а поступает на первые входы второго сумматора 2 и сумматора-вычитателя 3. Во втором сумматоре-вычитателе 3 по выражению (7) вычисляется значение 2 ,которое подается на второй вход третьего сзт матора-вычи- тателя 3 и второй вход второго сумматора.

Во втором сумматоре 2 по вьфажению (7) вычисляется 2 -о , которое поступает на третий вход третьего сумматора-вычитателя 1, в вычисляется значение

котором С и X по выражению (8) . Значение с поступает ла первьй вход последующего сумматора-вычитателя 1, а значение х - на управляющие входы четвертого и трег тьих сумматоров-вычитателей 1 и 3 соответственно и третьего переключателя 5. Аналогичным образом в каждом 1-м сумматоре-вычитателе 1 по выражению (8) вычисляется значение с поступающее на первый вход ()-го сумматора-вычитателя 1, и значение X J которое подается на управляющие входы 1 -го сумматора-вычитателя 3 и переключателя 5 и (i-t-l)-ro сумматора-вычитателя 1, В зависимости от значения х из выхода i -го переключателя 5 подается величина -3q или а на первые входы -го сумматора 2 и сумматора-вычитател-я 3. В i -м сумматоре-вычитателе 3 по выражению (9) определяется значение 2 Q , которое подается на второй вход (i + 1)-го сумматора-вычитателя 3 и второй вход i -го сумматора 2. Вi -м сумматоре 2 по выражению, (9) вычисляется значение которое поступает на второй вход (i 1)-го трехвходового сзгмматора-вычитателя 1, в котором по вьфажению (8) вычисляется значение с и х . Наконец, в h-м сумматоре-вычитателе 1 по выражению (8) вычисляется значение X , которое подается на вход м-падшего разряда 9 выходной шины 9,. Таким образом, на h разрядах 9, 9,.,. ,9 выходной шины 9 за время переходного процесса в схеме образуются соответственно значения х , v ,.,.,) искомого вектора х (х ,х ,...,).

Формула изобретения

1. Параллельное устройство для решения квадратного уравнения, содержащее ц сумматоров, (и- 1) сумматоров- вычитателей, где и-разрядность устройства, -отличающееся- тем, что, с целью расширения функциональных возможностей за счет реализации решения квадратного уравнения вида ах -f Ъх + С о, в него введены h трехвходовых сумматоров-вычитате- лей и (п -1) коммутаторов, причем выход i -го трехвходового сумматора- вБ1читателя / 1, (п-1)/ соединен с первым информационным входом (i+1)-ro трехвходового сумматора-вычитателя, второй информационный вход которого соединен с выходом i -го сумматора, знаковый (Уход i -го трехвходового сумматора-вычитателя соединен с входом признака операции входом (i -ь 1)-го трехвходового сумматоравычитателя, с управляющим входом и-го коммутатора, входом признака операции i-го сумматора-вычитателя 5 и выходом i-го разряда результата устройства, выход -го коммутатора соединен со сдвигом вправо на (2i + 2) разрядов с первым информационным входом i-го сумматора и первым 10 информационным входом i-го сумматора- вычитателя, знаковьй выход ti-го трехвходового сумматора-вычитателя соединен с выходом П -то разряда результата устройства, вход коэффициента с уст- 15 ройства соединен с первым информахщ- онным входом первого трехвходового сумматора-вычитателя, вход коэффищ- ента b устройства соединен со сдвигом вправо на i разрядов с вторым инфор- 20 мационным входом i-го трехвходового сумматора-вычитателя ( L 1,ц ), вход коэффициента q устройства соединен со сдвигом вправо на 2 разряда с тре- тьим информационным входом первого

25 трехвходового сумматора-вычитателя, с первым информационным входом и-го сумматора, со сдвигом влево на 1 разряд с вторым информационным входом сумматора, с первым информацион30 ным входом каждого коммутатора, со сдвигом вправо на 3 разряда с вторым информационным входом первого сумматора и вторым информационным входом первого сумматора-вычитателя, выход

25 которого соединен со сдвигом вправо на 1 разряд с вторым информационным входом второго сз мматора-вычитателя, выход i -го сумматора-вычитателя / 2, () / соединен со сдвигом

4Q вправо на 1 разряд с вторым информационным входом (П + 1)-го сумматора- вычитателя и вторым информационнь1м входом -го сумматора, выход (n-l)-ro сумматора-вычитателя соединен со сдви42 гом вправо на 1 разряд с вторым ин- формационным входом {ii-1)-ro сумматора, выход п-го сумматора соединен с вторым информационным входом каж- дого коммутатора.

50 2, Устройство по П.1, о т л и ч а- ю щ е е с я тем, что каждьй трехвхо- довьш сумматор-вычитатель содержит двухвходовый сумматор и двухвходовый сумматор-вычитатель, причем первьй 55 информационный вход двухвходового

сумматора-вычитателя является первым информационным входом трехвходового сумматора-вычитателя, второй и третий

информационные входы которого соединены соответственно с первым и вторым информационными входами двухвходово- го сумматора, выход которого соединен с вторым информационным входом

двухвходового сумматора-вычитателя, выход и вход признака операции которого являются соответственно выходом и входом признака операции трехвходо- вого сумматора-вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1986 |

|

SU1381492A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1983 |

|

SU1265793A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Матричное устройство для решения дифференциальных уравнений в частных производных | 1982 |

|

SU1120346A1 |

| Матричный вычислитель гиперболических функций | 1982 |

|

SU1149251A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для дифференцирования функций | 1986 |

|

SU1335995A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1119009A1 |

фиг. г

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пухов Г.Е | |||

| и др | |||

| Разрядно-аналого- вые вычислительные системы | |||

| М.: Сов | |||

| ,радио, 1978. | |||

Авторы

Даты

1986-08-07—Публикация

1984-07-16—Подача