со

00

г

ГчЭ

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Матричный вычислитель | 1985 |

|

SU1265765A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| Матричный вычислитель | 1985 |

|

SU1283791A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для деления | 1981 |

|

SU1051535A1 |

| Вычислительное устройство | 1985 |

|

SU1272330A1 |

| Матричный вычислитель логарифмов | 1981 |

|

SU1012251A1 |

| Матричный вычислитель гиперболических функций | 1982 |

|

SU1149251A1 |

Изобретение относится к вычислительной технике и может использоfi n ч ваться автономно или в комплексе с цифровой вычислительной машиной для увеличения производительности вычислений. Целью изобретения является расширение области применения.за счет выполнения деления комплексных чисел. Поставленная цел. достигается тем, что устройство, включающее первую и вторую группы сумматоров 1 и два элемента ИСКЛЮЧАОДЕЕ ИЛИ 7, содержит третью и четвертую группы сумматоров 1, две группы сумматоров 2 промежуточных вычислений, группы вычислителей 3, 6 значений разрядов, две груп- п. сумматоров 4 определения остатков и группу сумматоров 5 определяющих значений с соответствующими связями. 2 з.п. ф-лы, 3 ил. чэ сл с:

/Р /F I №

IDuii

113814922

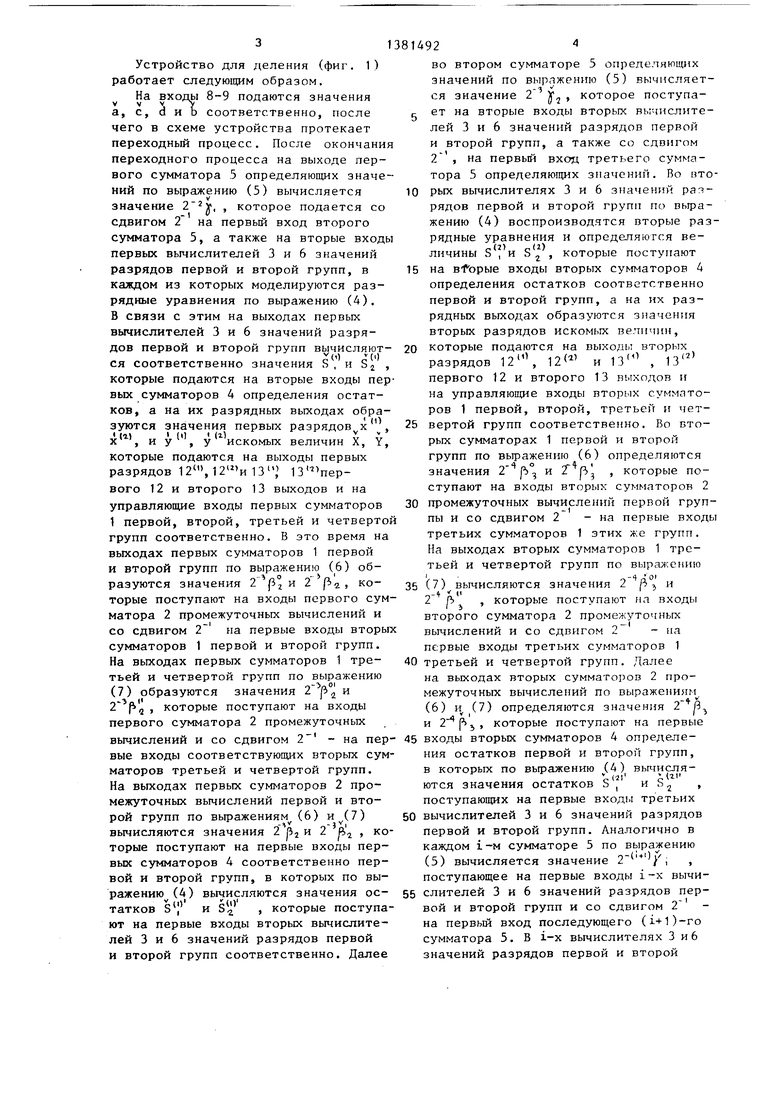

Изобретение относится к вычисли-ты ИСКЛЮ ШОЩЕЕ ИЛИ 7, информационные

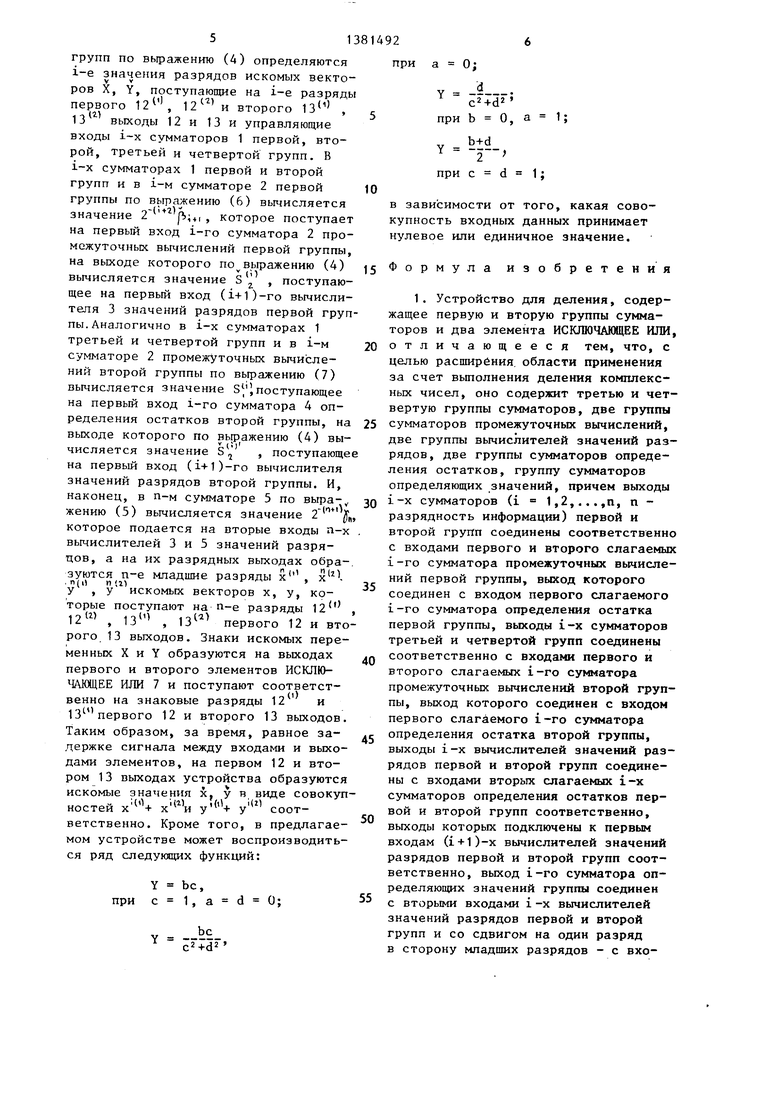

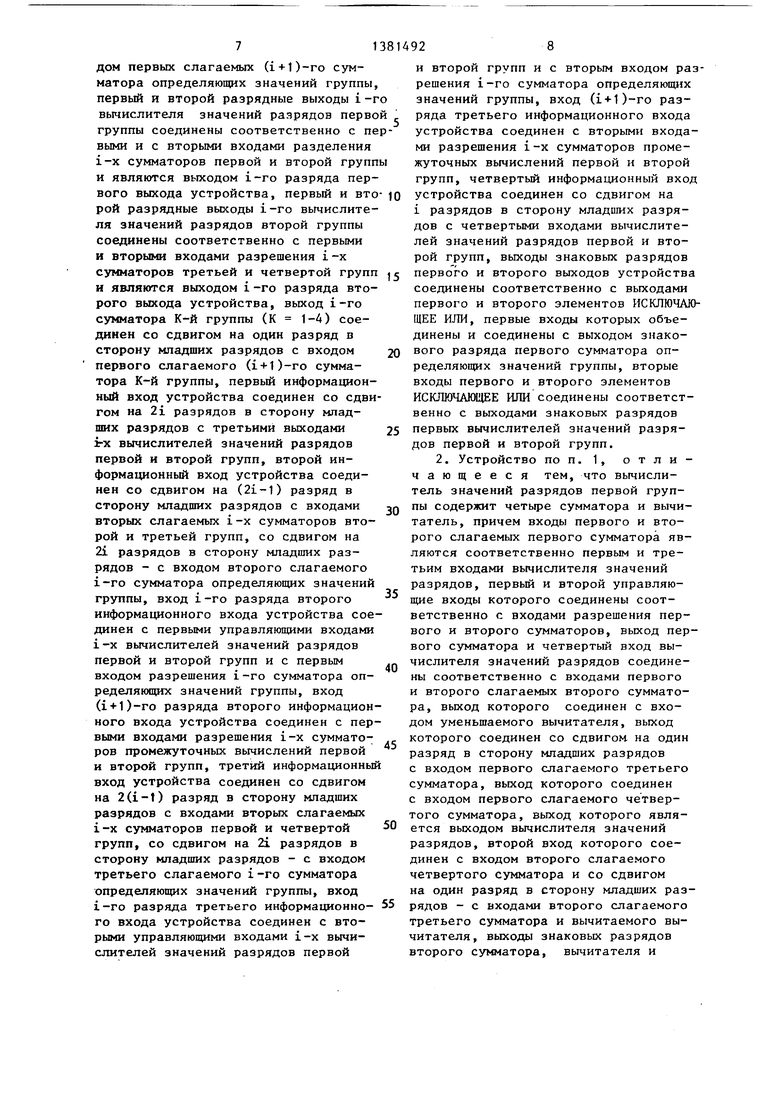

тельной технике и может быть исполь-входы 8-11 и выходы 12 и 13. зовано в составе многопроцессорной Вычислитель 3 значений разрядов

вычислительной машины как быстродей- г(фиг. 2) содержит четыре сумматора

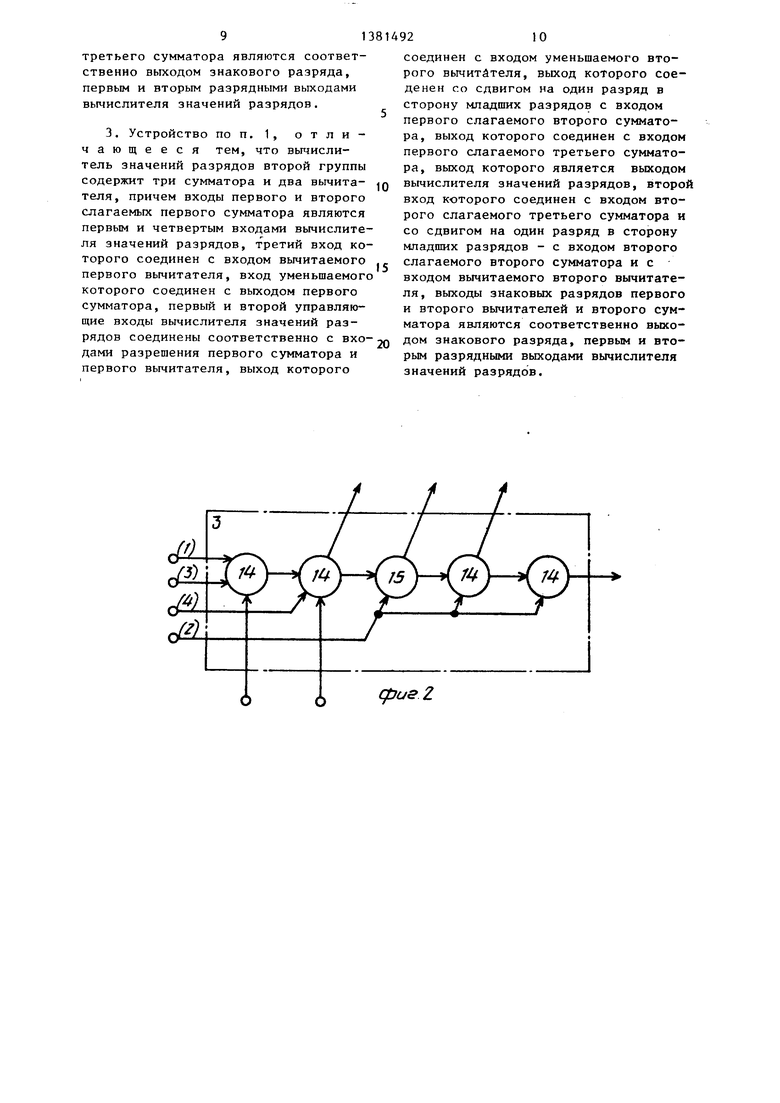

ствующее многофункциональное устрой-14 и вычитатель 15., ство.Вычислитель 6 значений разрядов

(фиг. 3) содержит три сумматора 14

Цель изобретения - расширение об-„ вычитателя 15.

ласти применения устройства для де- ,Q Работа симметричного устройства

ления за счет выполнения деления ком-д. деления чисел плексных чисел.

На фиг. 1 изображена схема устрой-211В x+iy (1)

ства для деления для случая, когдаc+jd

п 3 (п - разрядность представления 5основывается на следующих соотношеинформации); на фиг. 2 и 3 - схемыниях: вычислителей значений разрядов первой и второй групп соответственно х . у -SlE , (2) (цифрами в скобках обозначены номера c +d яходов). 20 Запишем выражения (2) в разрядной

форме как;

Устройство для деления (фиг. 1)

VV V „.. Vv V V 7у VV Vw УУ V V

содержит четыре группы сумматоров 1,ac+bd-(cc+dd) bc-ad-(cc-t-dd),(3) две группы сумматоров 2 промежуточных вычислений, первую группу вычи- 25 Для определения п-разрядных значеслителей 3 значений разрядов, двений и у в выражении (3) запишем

группы сумматоров 4 определения ос-п-разрядных уравнений, на основании

татков, группу сумматоров 5 определя-каждого из которых определяется соющих значений, вторую группу вычи-ответствующее i-e значение (,2,,

слителей 6 значений разрядов, элемен-30..-, п).

S; - . 2- а . bd) 2- - }; i . ; ; V - .., s)

. 2(U - d) }, . H ; - ,, Г ()

где if; ., . ( . dd)

2-(U.1 ;„ ,, . p,4, d; p.;. , .

. i; (5)

, dx (6)

2- - p;,, 2- - | ;.. . 2- - p ;, d ;

,, - dy

Алгоритм вычислений значений раз- ,рядном уравнении (4) может быть зарядов X, у аналогичен и в каждом раз- писан как:

г . r(i.iV-i ; „ ; v; п .li+o v i(0

, „pH|i::° - 2- (Si. Щ. (,) ; ,; -.;ПРИ ;;;:

, : - -ПоёГ -ё Г.ё -Ч (2- - f;l f. S ; .

2) г 1

t; 1 „ при .(lu, (8). и S

1 i (l) 1 (11 MI) (П

где x x -t-x , +y

Устройство для деления (фиг. 1) работает следующим образом, На входь 8-9 подаются значения а, с, d и Ь соответственно, после чего в схеме устройства протекает переходный процесс. После окончания переходного процесса на выходе первого сумматора 5 определяюгцих значений по выражению (5) вычисляется значение 2, , которое подается со сдвигом 2 на первый вход второго сумматора 5, а также на вторые входы первых вычислителей 3 и 6 значений разрядов первой и второй групп, в каждом из которых моделируются разрядные уравнения по выражению (4). В связи с этим на выходах первых вычислителей 3 и 6 значений разрядов первой и второй групп вычисляютV(,i v(,)

ся соответственно значения S , и Sj , которые подаются на вторые входы первых сумматоров 4 определения остатков, а на их разрядных выходах обра ю зуются значения первых разрядов х .

Ча (1) (г V V х , и y , у ИСКОМЫХ величин X, Y,

которые подаются на выходы первых разрядов 12, 13, вого 12 и второго 13 выходов и на управляющие входы первых сумматоров 1 первой, второй, третьей и четвертой групп соответственно. В это время на выходах первых сумматоров 1 первой и второй групп по выражению (6) образуются значения 2 р° и 2 , которые поступают на входы первого сумматора 2 промежуточных вычислений и со сдвигом 2 на первые входы вторых сумматоров 1 первой и второй групп. На выходах первых сумматоров 1 третьей и четвертой групп по выражению (7) образуются значения 2 j и 2( I которые поступают на входы первого сумматора 2 промежуточных

вычислений и со сдвигом 2 - на первые входы третьих сумматоров 1 40 третьей и четвертой групп. Далее на выходах вторых сумматоров 2 провычислений и со сдвигом 2 вые входы соответствующих вторых сумматоров третьей и четвертой групп. На выходах первых сумматоров 2 промежуточных вычислений первой и второй групп по выражениям (6) и (7) вычисляются значения 2 В и 2 В , которые поступают на первые входы первых сумматоров 4 соответственно первой и второй групп, в которых по вымежуточных вычислении по выражениям (6) и (7) определяются значения 2 и 2,,, которые поступают на первые - на пер- 45 входы вторых сумматоров 4 определения остатков первой и второи групп,

в которых по вьфажению (4) вьгчисля(2| Л(г1

ются значения остатков S

и s;

поступающих на первые входы третьих 50 вычислителей 3 и 6 значений разрядов первой и второй групп. Аналогично в каждом i-м сумматоре 5 по выражению (5) вычисляется значение , , поступающее на первые входы i-х вычи:( I

и S

(I)

которые поступаражению (4) вычисляются значения ос- 55 слителей 3 и 6 значений разрядов первой и второй групп и со сдвигом 2 на первый вход последующего (i+1)-ro сумматора 5. В i-x вычислителях 3 и6 значений разрядов первой и второй

ют на первые входы вторых вычислителей 3 и 6 значений разрядов первой и второй групп соответственно. Далее

381492Ч

во втором сумматоре 5 определяющих значений по выражению (5) вычисляет л v

СЯ значение 2 у, , которое поступа- g ет на вторые входы вторых вычислителей 3 и 6 значений разрядов первой и второй групп, а также со сдвигом 2 , на первый вход третьего сумматора 5 определяю1цих значений. Во нто- 10 рых вычислителях 3 и 6 значений ра:ч- рядов первой и второй групп по выражению (4) воспроизводятся вторые разрядные уравнения и определяются величины S , и S 2 , которые поступают 15 на в Горые входы вторых сумматоров 4 определения остатков соответственно первой и второй групп, а на их разрядных выходах образуются значения вторых разрядов искомых величин, 20 которые подаются на выходы вторых разрядов 12, 12( и , первого 12 и второго 13 выходов и на управляющие входы вторых сумматоров 1 первой, второй, третьей и чет- 25 вертой групп соответственно. Во вторых сумматорах 1 первой и второй групп по вьфажению (6) определяются значения 2 |Ъ° и 2 р

которые поступают на входы вторых сумматоров 2 30 промежуточных вычислений первой группы и со сдвигом 2 - на первые входы третьих сумматоров 1 этих же групп. На выходах вторых сумматоров 1 третьей и четвертой групп по вырал-;ению

2- -Y,

и

35 (7) вычисляются значения 2 (1

которые поступают ил входы

2 промежуточных Т

второго сумматора

вычислений и со сдвигом 2 - на первые входы третьих сумматоров 1 40 третьей и четвертой групп. Далее на выходах вторых сумматоров 2 прония остатков первой и второи групп,

в которых по вьфажению (4) вьгчисля(2| Л(г1

ются значения остатков S

и s;

поступающих на первые входы третьих 50 вычислителей 3 и 6 значений разрядов первой и второй групп. Аналогично в каждом i-м сумматоре 5 по выражению (5) вычисляется значение , , поступающее на первые входы i-х вычигрупп по выражению (А) определяются i-e значения разрядов искомых векторов X, Y, поступающие на i-e разряды первого , и второго , 13 выходы 12 и 13 и управляющие входы сумматоров 1 первой, второй, третьей и четвертой групп. В i-x сумматорах 1 первой и второй групп и в i-M сумматоре 2 первой группы по вьгражению (6) вычисляется значение , , которое поступает на первый вход i-ro сумматора 2 промежуточных вычислений первой группы, на выходе которого по вьфажению (Д) вычисляется значение S , поступающее на первый вход (i+1)-ro вычислителя 3 значений разрядов первой группы. Аналогично в i-x сумматорах 1 третьей и четвертой групп и в i-м сумматоре 2 промежуточных вычислений второй группы по вьгражению (7) вычисляется значение S iпоступающее на первый вход i-ro сумматора А определения остатков второй группы, на выходе которого по вьгражению (4) вычисляется значение , поступающе на первый вход (i+O-ro вычислителя значений разрядов второй группы. И, наконец, в п-м сумматоре 5 по выра- жению (5) вычисляется значение которое подается на вторые входы п-х вычислителей 3 и 5 значений разрядов, а на их разрядных выходах образуются п-е младшие разряды .n(il и (г) у , у искомьк векторов х, у,

торые поступают на п-е разряды

12

ti)

13

С)

13

u

ко- 12

первого 12 и второго 13 выходов. Знаки искомых переменных X и Y образуются на выходах первого и второго элементов ИСКЛЮ- ИЛИ 7 и поступают соответственно на знаковые разряды и 13 первого 12 и второго 13 выходов. Таким образом, за время, равное задержке сигнала между входами и выходами элементов, на первом 12 и втором 13 выходах устройства образуются искомые значения х. у в виде совокупностей COOTветственно. Кроме того, в предлагаемом устройстве может воспроизводиться ряд следукяцих функций:

при

Y be,

с 1, а d 0;

Y

be

при

0;

Y

d

при b 0, a 1;

у - bld Y - 2-

при с d 1;

0

5

0

в зависимости от того, какая совокупность входных данных принимает нулевое или единичное значение.

5 Формула изобретения

0 отличающееся тем, что, с целью расширения области применения за счет выполнения деления комплексных чисел, оно содержит третью и четвертую группы сумматоров, две группы

5 сумматоров промежуточных вычислений, две группы вычислителей значений разрядов , две группы сумматоров определения остатков, группу сумматоров определяющих значений, причем выходы i-x сумматоров (i 1,2,...,п, п - разрядность информации) первой и второй групп соединены соответственно с входами первого и второго слагаемых i-го сумматора промежуточных вычислений первой группы, выход которого соединен с входом первого слагаемого i-го сумматора определения остатка первой группы, выходы i-x сумматоров третьей и четвертой групп соединены соответственно с входами первого и второго слагаемых i-ro сумматора промежуточных вычислений второй группы, выход которого соединен с входом

первого слагаемого 1-го сумматора определения остатка второй группы, выходы i-x вычислителей значений разрядов первой и второй групп соединены с входами вторых слагаемых 1-х сумматоров определения остатков первой и второй групп соответственно, выходы которых подключены к первым входам (i+l)-x вычислителей значений разрядов первой и второй групп соответственно, выход i-ro сумматора определяющих значений группы соединен с вторыми входами i-х вычислителей значений разрядов первой и второй групп и со сдвигом на один разряд в сторону младших разрядов - с вхо7

дом первых слагаемых (i+1)-ro сумматора определяющих значений группы первый и второй разрядные выходы iвычислителя значений разрядов перв группы соединены соответственно с пвыми и с вторыми входами разделения i-x сумматоров первой и второй груп и являются выходом i-ro разряда первого выхода устройства, первый и вт рой разрядные выходы i-го вычислителя значений разрядов второй группы соединены соответственно с первыми и вторыми входами разрешения i-х сумматоров третьей и четвертой груп и являются выходом i-го разряда второго выхода устройства, выход i-ro сумматора К-й группы (К 1-4) соединен со сдвигом на один разряд в сторону младших разрядов с входом первого слагаемого ()-ro сумматора К-й группы, первый информационный вход устройства соединен со сдвгом на 21 разрядов в сторону младших разрядов с третьими выходами tx вычислителей значений разрядов первой и второй групп, второй информационный вход устройства соединен со сдвигом на (21-1) разряд в сторону младших разрядов с входами вторых слагаемых i-x сумматоров второй и третьей групп, со сдвигом на 21 разрядов в сторону младших разрядов - с входом второго слагаемого 1-го сумматора определяющих значени группы, вход 1-го разряда второго информационного входа устройства содинен с первыми управляющими входам 1-X вычислителей значений разрядов первой и второй групп и с первым входом разрешения i-го сумматора определяющих значений группы, вход (1+1)-го разряда второго информационого входа устройства соединен с певыми входами разрешения i-x сумматоров промежуточных вьмислений первой и второй групп, третий информационн вход устройства соединен со сдвигом на 2(1-t) разряд в сторону младших разрядов с входами вторых слагаемых 1-х сумматоров первой и четвертой групп, со сдвигом на 21 разрядов в сторону младших разрядов - с входом третьего слагаемого 1-го сумматора определяющих значений группы, вход 1-го разряда третьего информационно го входа устройства соединен с вторыми управляющими входами 1-х вычислителей значений разрядов первой

ю j 20 25 0 5

30

35

40

5

8

и второй групп и с вторым входом разрешения i-ro сумматора определяющих значений группы, вход (1+1)-го разряда третьего информационного входа устройства соединен с вторыми входами разрешения i-x сумматоров промежуточных вычислений первой и второй групп, четвертый информационный вход устройства соединен со сдвигом на i разрядов в сторону младших разрядов с четвертыми входами вычислителей значений разрядов первой и второй групп, выходы знаковых разрядов первого и второго выходов устройства соединены соответственно с выходами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых объединены и соединены с выходом знакового разряда первого сумматора определяющих значений группы, вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами знаковых разрядов первых вычислителей значений разрядов первой и второй групп.

третьего сумматора являются соответственно выходом знакового разряда, первым и вторым разрядными выходами вычислителя значений разрядов.

соединен с входом уменьшаемого второго вычитйтеля, выход которого сое- денен со сдвигом на один разряд в сторону младших разрядов с входом первого слагаемого второго сумматора, выход которого соединен с входом первого слагаемого третьего сумматора, выход которого является выходом вычислителя значений разрядов, второй вход которого соединен с входом второго слагаемого третьего сумматора и со сдвигом на один разряд в сторону младших разрядов - с входом второго слагаемого второго сумматора и с входом вычитаемого второго вычитателя, выходы знаковых разрядов первого и второго вычитателей и второго сумматора являются соответственно выходом знакового разряда, первым и вторым разрядными выходами вычислителя значений разрядов.

cpusZ

О

фиг 5

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1206774, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-04-25—Подача