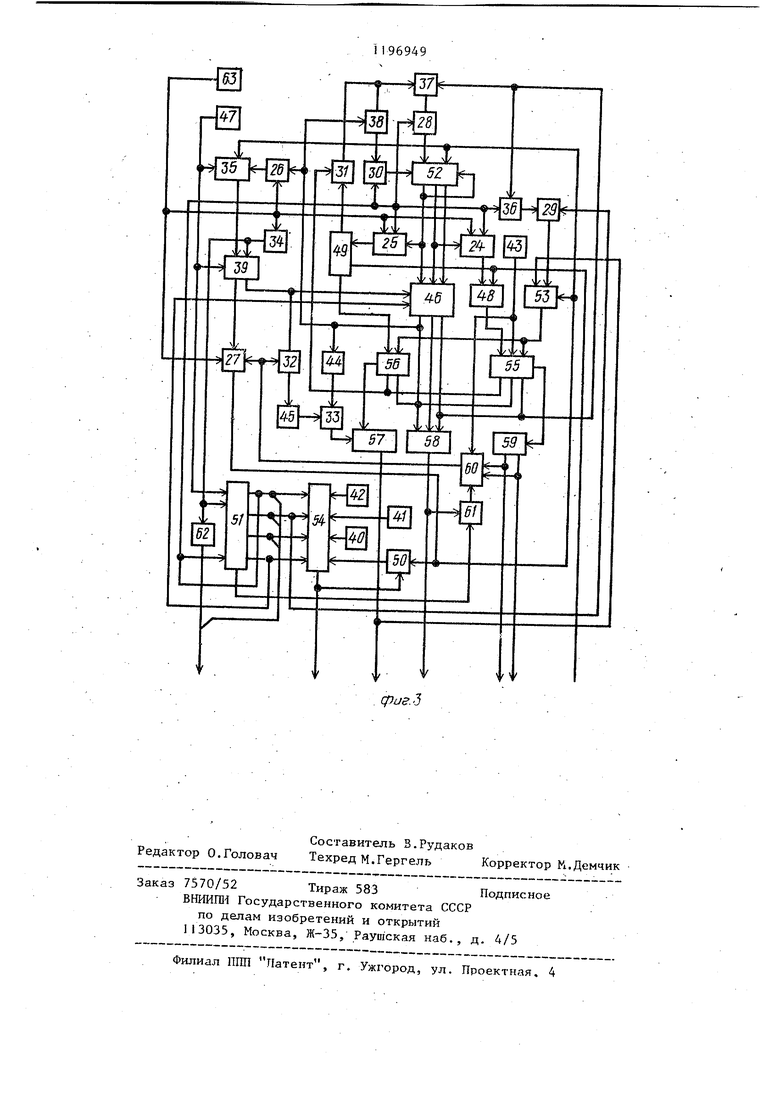

НЕ, RS-триггеры.с первого по четвертый, В-триггер, формирователи .сигналов с первого по восьмой, регистры с второго по четвертый, первый и второй регистры сдвига, счетчик, коммутаторы со второго по четвертый, группы усилителей, третш блок сравнения, второй дешифратор, элемент задержки и третий генератор импульсов, выход которого подключен к первым-входам элементов И с четвертого по седьмой и через второй элемент НЕ - к С-входам D-триггера, первого регистра сдвига и к входу элемента задержки, .С-выходы второго и третьего регистров соединены соотрзетственно с выходами .четвертого и пятого элементов И, выход шестого элемента И соединен с первьвд R-входом первого RS-триггера, выход которого соединен с D-входом D-триггера, выход седьмого элемента И соединен с С-входами четвертого регистра, счетчика и с S-входами первого RS-триггера и второго регистра сдвига, С-вход которого соединен с выходом восьмого элемента И, первый выход первого регистра сдвига соединен с первым входом второ.о дешифратора, выход которого соединен с первым входом третьего блока сравнения, второй выход первого регистра сдвига соединен . с первыми входами седьмого формирователя и второго коммутатора, выход которого соединен с D-входом четвертого регистра, третий вькод первого регистра сдвига соединен со вторым входом второго коммутатора, четверть1й выход первого регистра сдвига соединен с третьим входом второго коммутатора и с первым входом девятого элемента И, выход которого соединен со счетным входом счетчика, пятый выход первого регистра сдвига соединен с D-входом первого -регистра сдвига, с вторыми входами четвертого и пятого элементов И, с первьи и входами восьмого и десятого элементов И, с R-входом второго RS-триггера и с чевертым входом второго коммутатора, входы с пятого по восьмой которого соединены соответственно с выходами четвертого регистра и формирователей сигналов с первого по третий, первый выход второго регистра сдвига соединен с вторьш входом седьмого формироват(аля сигналов, первьц ВЫХОД которого соединен с иСувыми рходами усилителей второй группы, второго коммутатора, с S-входами второго и третьего RS-триггеров, второй выход второго регистра сдвига соединен с третьими входами четвертого элемента И и седьмого формирователя сигналов, второй выход которого соединен с вторыми входами усилителей второй группы, третьего коммутатора, с первыми входами четвертого коммутатора и одиннаддатого элемента И, третий выход второго регистра сдвига соединен с D-входом второго регистра сдвига, с третьим входом пятого элемента И и с четвертым входом седьмого формирователя сигналов, третий выход которого соединен с третьими входами усилителей второй группы, третьего коммутатора, с вторыми входами четвертого коммутатора, шестого элемента И, с R-входом четвертого RS-триггера и через пятый формирователь сигналов - с первым входом элемента ИЛИ, выход одиннадцатого элемента И соединен с R-входом третьего RS-триггера и S-входом четвертого RS-триггера, выход которого соединен с вторым входом десятого элемента И, выход которого соединен с R-входом

второго регистра сдвига, выходы второго и третьего RS-триггеров соединены соответственно с вторыми входами девятого и восьмого элементов И,выход второго регистра соединен с четвертым входом третьего

коммутатс(ра, выход которого соединен с входами усилителей третьей группы, первый и второй выходы третьего регистра соединены соответственно с вторым входом одиннадцатого элемента И и с третьим входом четвертого коммутатора, выход которого соединен с первыми : входами усилителей первой группы, первый выход -О-триггера соединен с вторым входом седьмого элемента И,третий вход которого соединен с

первым входом двенадцатого элемента И и с выходом третьего блока сравнения, BTOpoii выход D-TpHr.repa соединен с пятым входом седьмого формирователя сигналов и с вторым входом Двенадцатого элемента И, выход которого через шестой формирователь сигналов соединен с вторым вхо

дом элемента ИЛИ, выход которг го соединен с вторыми входами усилителей первой группы, выход четвертого формирователя сигналов соединен с вторым входом третьего блока сравнения и с пятым входом третьего коммутатора, Аестой вход которого.со единен с четвертым входом четвертого коммутатора и с выходом счетчика, первые выходы усилителей третьей группы соединены с третьим входом третьего блока сравнения, вьп4оды усилителей третьей группы соединены с четвертым входом третьего блока сравнения, выход восьмого фор96949

мирователя сигналов соединен с вторым R-входом первого RS-триггера, с R-входом D-триггера и с S-входом первого регистра сдвига, причем D-входы второго и третьего регистров являются входом.блока, выходами которого являются выход элемента задержки,, выход второго ком утатора, третий вьгход первого регистра сдвига, выходы усилителей первой группы, пятый выход первого регистра сдвига, первые и вторые выходы усилителей третьей группы, выходы,усилителей второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Устройство для отображения и редактирования информации на экране электронно-лучевой трубки | 1989 |

|

SU1695288A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

I.ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, первые и вторые входы и выходы которых являются соответственно первым и вторым входами и первым выходом устройства, адресные блоки, выходы которых соединены с третьими входами соответствующих блоков памяти, о тличающее. с,я тем, что, с целью повышения емкости устройства, в ,него введен формирователь адресных сигналов, вход которого подключен к выходам блоков памяти, первый и второй выходы соединены с первыми и вторыми входами блоков памяти и адресных блоков, третий и четвертый выходы формирователя ад ресных .сигналов и третий и четверть1й входы адресных блоков являются соответственно третьим и четвертым входами устройства, Четвертые входы блоков памяти, пятые входы адресных блоков и пятый выход формирователя адресных сигналов являются вторым выходом устройства, шестой выход формирователя адресных сигналов соединен с шестыми входами адресных блоков. . 2. Устройство по п.1, о т л ичающееся тем, что каждый адресный блок содержит элементы И с первого по третий, первый элемент . НЕ, блоки сравнения, первый регистр, генераторы импульсов, первьгй коммутатор и дешифратор, выход которого подключен к первому входу второго элемента И, второй вход которого соединен с выходом первого блока сравнения, а выход подключен к входу первого элемента НЕ и первому входу первого элемента И, выход первого генератора импульсов соединен с первыми входами первых блока сравнения и регистра, второй и третий входы которого подключены g соответственно к выходам второго генератора импульсов и Первого элеСП мента И, а выход соединен с первым входом второго блока сравнения, вьгход которого подключен к первому входу третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, а выход - с первым входом первого коммутатора, со выход которого является выходом фор05 мирователя, входами которого являют-, OD ся соответственно второй в.хОд пер вого коммутатора и вход nepjjoro со дешифратора, второй вход первого блока сравнения, четвертыйвход первого регистра, второй вход вто рого блока сравнения и третий вход первого блока сравнения, третий вход второго блока сравнения, второй вход второго элемента И, 3. Устройство по П.1, о т л ичающее с я тем, что формирователь адресных сигналов содержит элементы И с четвертого по двенадцатый, элемент НЛП, второй элемент

Изобретение относится к вычислительной технике и может быть использовано при построении мультипроцессорных вычисл11тельных систем

Цель изобретения - повышение емкости устройства.

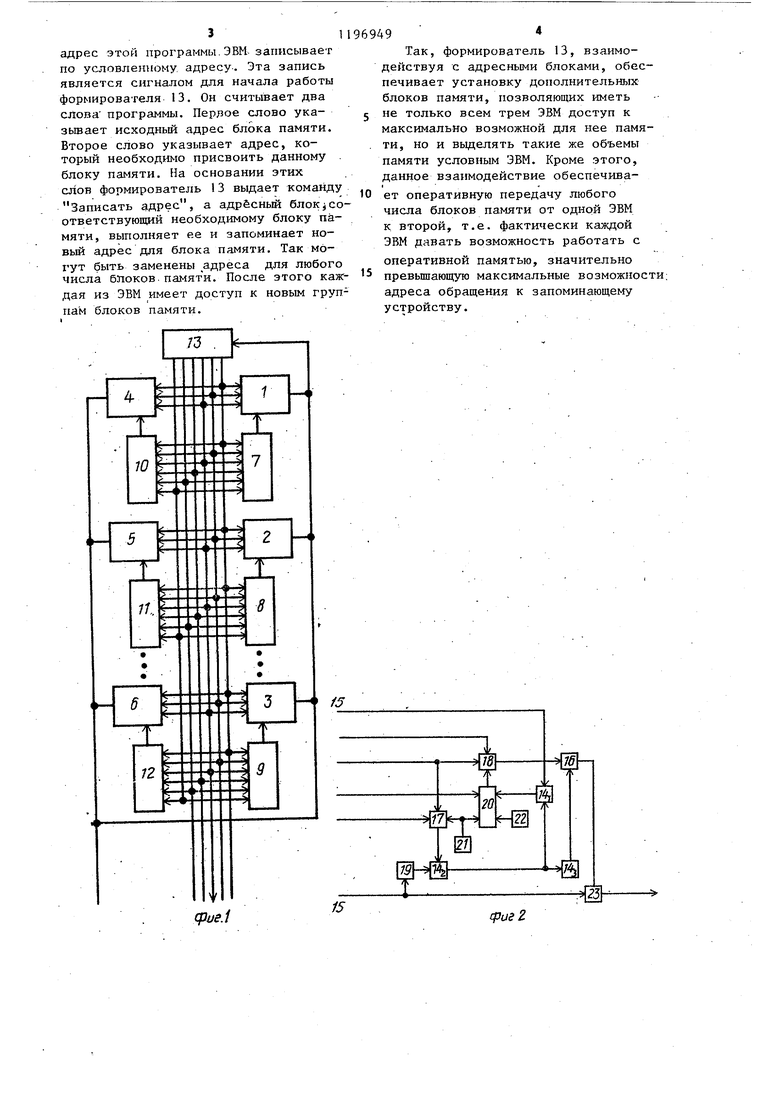

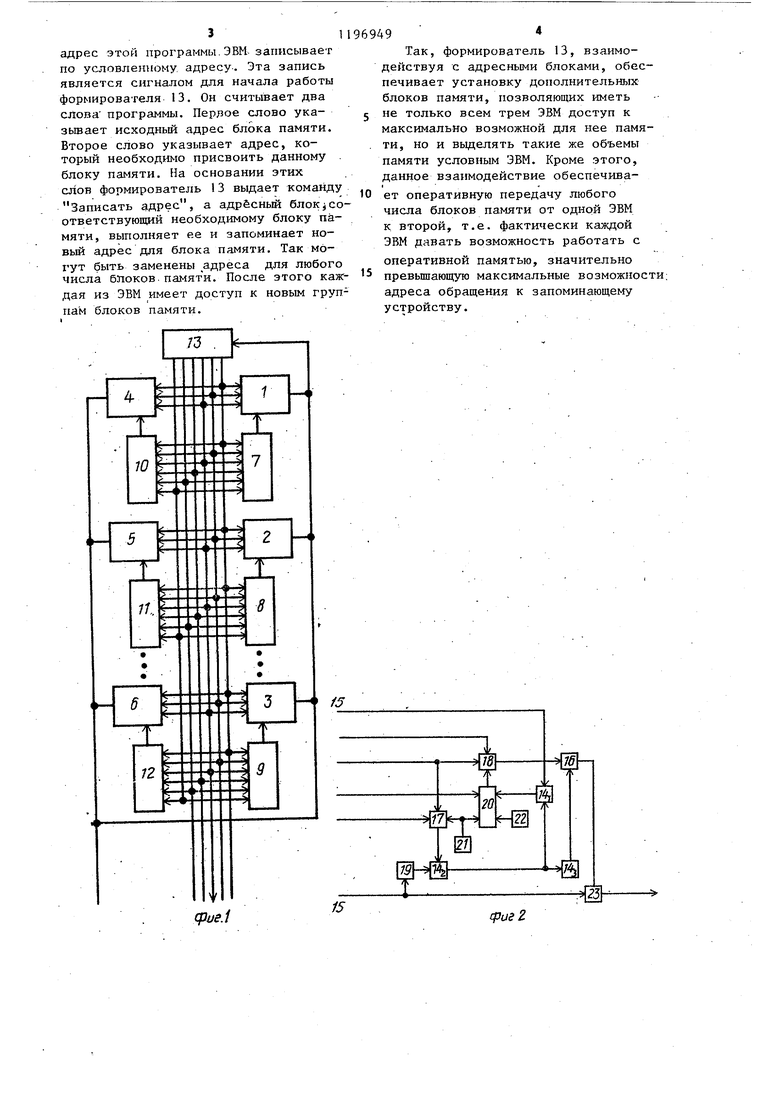

На фиг.1 изобра.жена структурная схема запоминающего устройства; на фиг.2 - структурная схема адресного блока; на фиг.3 - ртруктурная схема формирователя адресных сигналов.

Запоминающее устройство (фиг.1) содержит блоки 1-6 памяти, адресные, блоки 7-12 и формирователь. 13 адресных сигналов.

Каждый из адресных блоков 1-6 содержит (фиг.2) элементы И. 14|-14з с первого по третий, входные шины 15 первый элемент НЕ 16, первый 17 и второй 18 блоки сравнения, первый дешифратор 19, первый регистр 20, первый генератор 21 импульсов, второ генератор 22 импульсов и первый коммутатор 23.

Формирователь 13 адресных сигналов (фиг. 3J содержит элементы И 24-32- с третьего по двенадцатый, элемент ИЛИ 33, второй элемент НЕ 34 RS-триггеры 35-38 с первого по четвертый, D-триггер 39, формирователи 40-47 с первого по восьмой, второй 48, третий 49 и четвертьШ 50 регистры, первый 51 и второй 52 регистры сдвига, счетчик 53, второй 54, третий 55 и четвертьй 56 коммутаторы, первую 57, вторую 58 и третью 59

группы усилителей, третий блок 60 сравнения, второй деи ифратор 61, элемент 62 задержки и третий генератор 63 импульсов. .

Устройство-работаем следующим образом.

С устройством связано несколько ЭВМ (не показаны). Каждая ЭВМ обращается к запоминающему устройству в строго отведенное для нее

время. Выданный ЭВМ адрес дополняется формирователем 13 адресом ЭВМ, который вместе со старшей частью адреса от ЭВМ поступает во все адресные блоки 7-12. Здесь они сравниваются с хранимым адресом блоков 1-6 памяти. Адресный блок, определивший paiseHCTBo-полученного составного адреса с хранимым, передает полученную команду в соответствующий ему блок памяти, который выполняет ее. Так как формирователь 13

для каждой ЭВМ выдает разные адреса ЭВМ, то каждой,из ЭВМ доступны свои группы блоков памяти и не

доступны памяти других ЭВМ, о существовании которых они могут не знать. Такой режим работы ЭВМ, , подключенных к данному запоминающему устройству, соответствует режиму работы трех независимьтх одна от другой ЭВМ. Обмен информацией между ЭВМ осуществляет . формирователь 13 по программе, написанной для него одной из ЭВМ и помещенной в один из блоков памяти. Начальный

31

адрес этой программы.ЭВМ записывает по условленному адресу. Эта запись является сигналом для начала работы формирователя 13, Он считывает два слова программы. Перэое слово указьшает исходный адрес блока памяти. Второе слово указывает адрес, который необходимо присвоить данному блоку памяти. На основании этих слов формирователь 13 выдает команду Записать адрес, а адресный блок соответствующий необходимому блоку памяти, выполняет ее и запоминает новый адрес для блока памяти. Так могут быть заменены адреса для любого числа блоков, памяти. После этого каждая из ЭВМ имеет доступ к новым группам блоков памяти.

6949

Так, формирователь 13, взаимодействуя с адресными блоками, обеспечивает установку дополнительных блоков памяти, позволяющих иметь 5 не только всем трем ЭВМ доступ к

максимально возможной для нее памя. ти, но и выделять такие же объемы памяти условным ЭВМ. Кроме этого, данное взаимодействие обеспечивает оперативную передачу любого числа блоков памяти от одной ЭВМ к второй, т.е. фактически каждой ЭВМ давать возможность работать с

оперативной памятью, значительно превьшающую максимальные возможности; адреса обращения к запоминающему устройству.

15

срие.1

||ИО

apoeZ

сриг.д

| Запоминающее устройство | 1982 |

|

SU1016832A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Каган Б.М | |||

| Электронные вычис- лительные машины и системы.- М., Энергия, 1979, с | |||

| Автоматический прибор для регистрирования числа замыканий | 1922 |

|

SU454A1 |

Авторы

Даты

1985-12-07—Публикация

1984-03-01—Подача