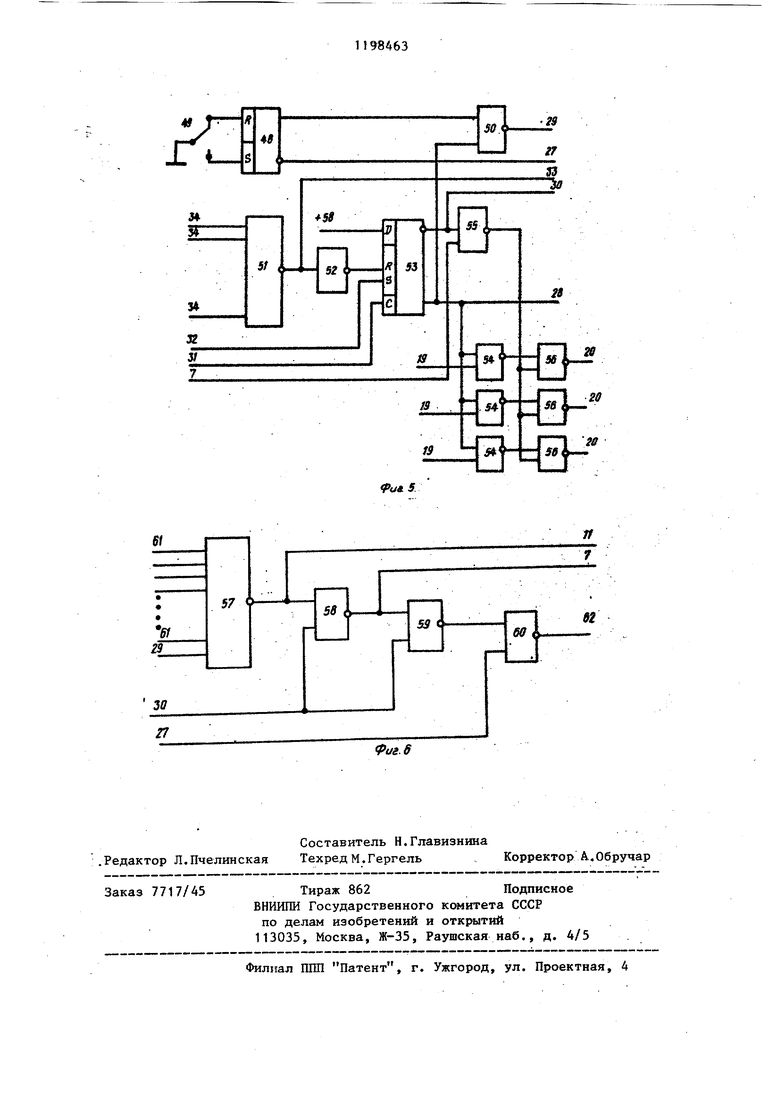

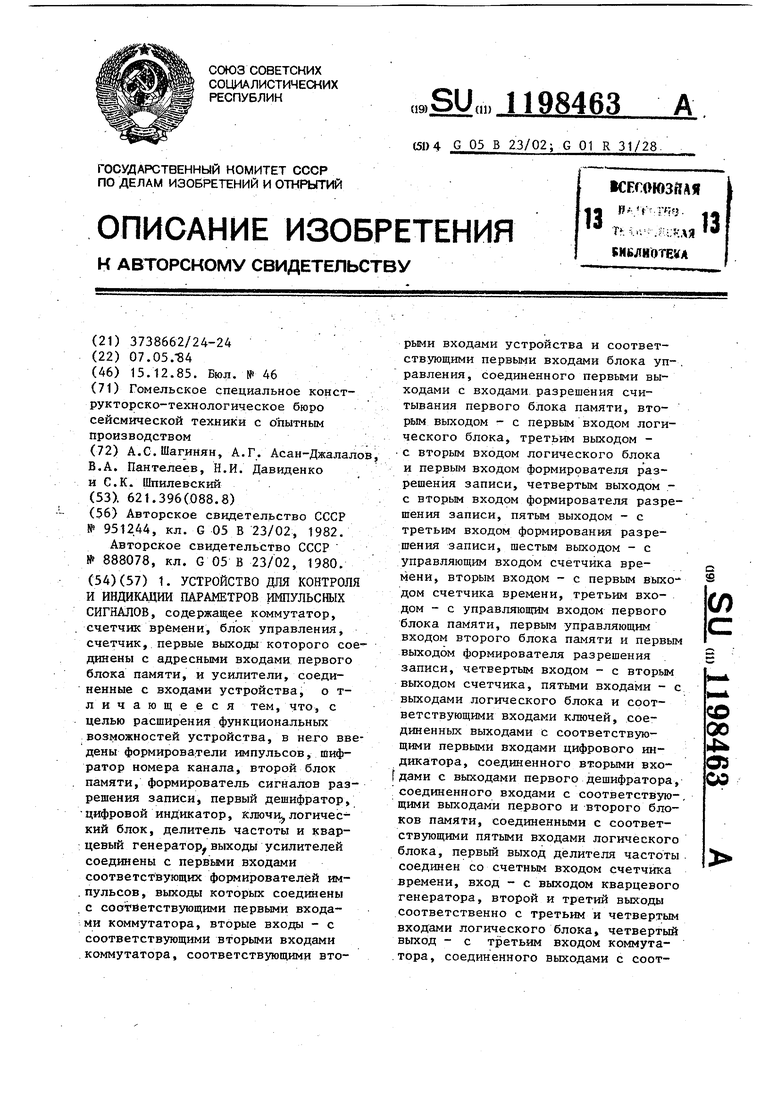

ветствующими входами шифратора номе ра канала и четвертыми входами формирователя разрешения записи, соединенного вторым выходом со счетным в.ходом счетчика, третьрм выходом с вторым управляющим входом второго блока памяти, соединенного информационными входами с выходами шифрато ,ра номера канала,; адресные входы вт ррго блока памят;,И1 соединены с первы ми выходами , информационны входы первого памяти соединены с вторымивыходами счетчика времени. 2.Устройство по п. 1, отличающееся тем, что блок управления содержит кнопку, соединенную первым выводом с общей шиной устройства, вторым и третьим выводами соответственно с R -и S -входами R5 -триггера, соединенного .прямым выходом с первым входом перв го элемента И-НЕ, соединенного выходом с четвертьм выходом блока управления, вторым входом - с вторым выходом блока управления и прямым выходом первого Г -триггера, соединённого D -входом с шиной питани устройства, 5 - и С -входами соответственно со вторым и четверты входами блока управления, R -входом - с выходом первого элемента НЕ инверсным выходом - с пятым выходом блока управления и первым входом первого элемента ИЛИ-НЕ, соединенного выходом с первыми входами вторых элементов И-НЕ, соединенных выходами с соответствующими первыми выходами блока управления, вторыми входами - с выходами соответствующих третьих элементов И-НЕ, соединенных первыми входами.с прямым выходом первого D -триггера, вторыми входами с соответствующими пятьвчи входами блока управления, третий вход которого соединен с вторым входом первого элемента ИЛИ-НЕ, пер вые входы - с соответствующими входами первого элемента И, соединенного выходом с шестым выходом, блока управления и с входом первого элемента НЕ. 3.Устройство по п. 1, отличающееся тем, что коммутато содержит второй счетчик, соединенный счетным входом с третьим входом коммутатора, R -входами с обще шиной устройства, выходами с соот3ветствующими входами второго дешифратора, соединенного выходами со входами соответствующих вторых элементов НЕ, соединенных выходами с первыми входами соответствующих четвертых элементов И-НЕ, соединенных вторыми входами с соответствующими первыми входами коммутатора, третьими входами с инверсными выходами соответствующих вторьпс D -триггеров, выходами - с С -входами соответствующих вторых D -триггеров, соединенных D -входами с шинами питания устройства, R -входами - с соответствующими вторыми входами коммутатора, выходы четвертых элементов И-НЕ соединены с соответствующими выходами коммутатора. 4.Устройство по п. 1, отличающееся тем, что формирователь разрешения записи содержит второй элемент ИЛИ-НЕ, соединенньй первыми входами с соответствующими четвертыми входами формирователя разрешения записи, вторыми входами с вторыми входами формирователя разрешения записи, выходом - со вторым выходом формирователя разрешения записи и с первым входом пятого элемента И-НЕ, соединенного вторым входом с третьим входом формирователя разрешения записи и с первым входом третьего элемента ИЛИ-НЕ, соединенного вторым входом с первым выходом формирователя разрешения записи и с выходом пятого элемента И-НЕ, выходом - с первым входом шестого элемента И-НЕ, соединенного вторым входом с первым входом формирователя разрешения записи, выходом - с .третьим выходом формирователя разрешения записи. 5.Устройство по п. 1, отличающееся тем, что логический блок содержит мультиплексор, соединенньй первыми информационными входами с шиной питания устройства, вторыми информациоиньми входами с общей шиной устройства, адресными входами - с соответствующими пятыми входами логического блока, соединенного первым входом с первьм входе седьмого элемента И-НЕ, вторым входом - с первым входом восьмого элемента И-НЕ и первым входом третьего дешифратора, четвертым и третьим входами - соответственно со вторым и третьим входами третьегб дешифратора, соединенного выходами с выходами логического блока, четвертым входом - с выходом седьмого элемента И-НЕ, соединенного вторым входом с выходом восьмого элемента И-НЕ, соединенного вторым входом с выходом мультиплексора.

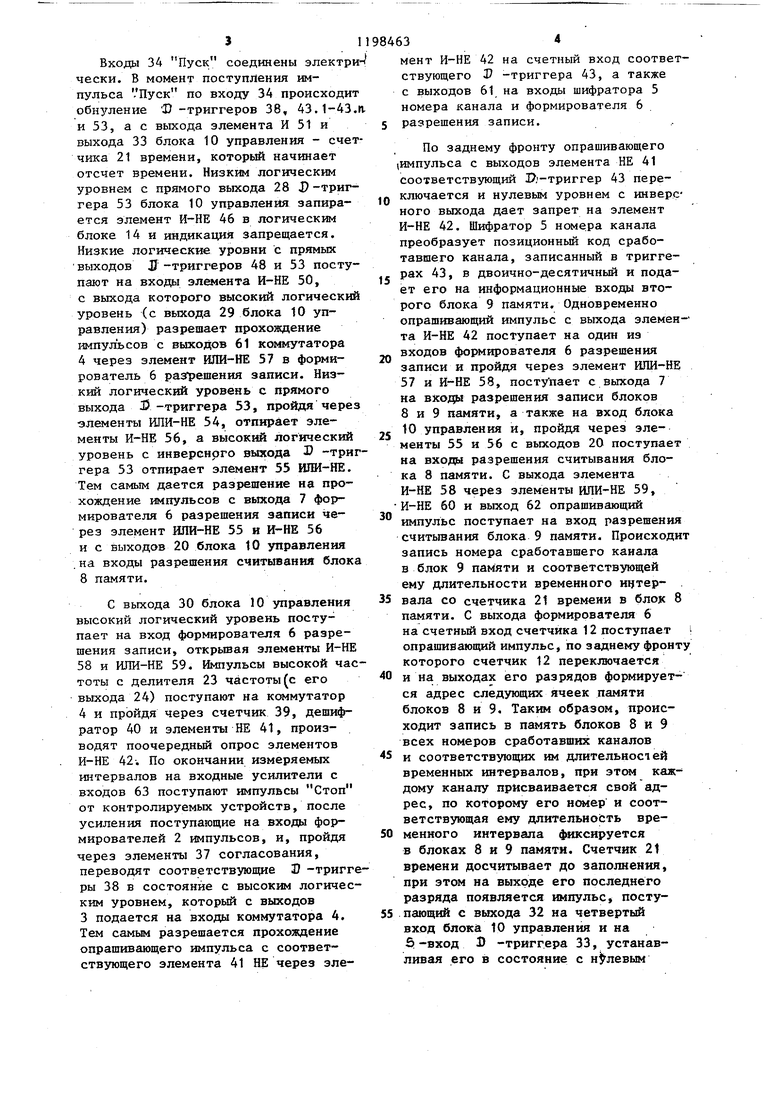

6. Устройство по п. 1, отличающееся тем, что формирователь содержит элемент согласования, соединенный входом с первым входом формирователя, выходом - с С -входом третьего Р -триггера, соединенного Э -входом с шиной питания устройства и выводом питания элемента согласования, R -входом со вторым входом формирователя, выходом - с выходом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для дистанционного управления топливораздаточными колонками | 1982 |

|

SU1067472A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для выдачи команд об изменении движения транспорта | 1986 |

|

SU1446640A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство для сопряжения процессоров | 1982 |

|

SU1053097A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИНДИКАДИИ ПАРАМЕТРОВ ИМПУЛЬСНЫХ СИГНАЛОВ, содержащее коммутатор, счетчик времени, блок управления, счетчик, первые выходы которого соединены с адресными входами первого блока памяти, и усилители, соединенные с входами устройства, о тличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены формирователи импульсов, шифратор номера канала, второй блок памяти, формирователь сигналов разрешения записи, первый дешифратор, цифровой индикатор, ключи,,логический блок, делитель частоты и квар: цевый генератор выходы усилителей соединены с первьми входами соответствующих формирователей им. пульсов, выходы которых соединены с соответствующими первыми входами коммутатора, вторые входы - с соответствующими вторыми входами ,коммутатора, соответствующими вторыми входами устройства и соответствующими первыми входами блока уп-, равления, соединенного первыми выходами с входами разрешения считывания первого блока памяти, вторым выходом - с первым входом логического блока, третьим выходом с вторым входом логического блока и первым входом формирователя разрешения записи, четвертым выходом с вторым входом формирователя разрешения записи, пятым выходом - с третьим входом формирования разрешения записи, шестым выходом - с управляющим входом счетчика врес мени, вторым входом - с первым выхо сл дом счетчика времени, третьим входом - с управляющим входом первого блока памяти, первым управляющим входом второго блока памяти и первым выходом формирователя разрешения записи, четвертым входом - с вторым выходом счетчика, пятыми входами - с вькодами логического блока и соот ветствующими входами ключей, сое00 4 диненных выходами с соответствующими первыми входами цифрового инas дикатора, соединенного вторыми вхосо дами с выходами первого дешифратора, соединенного входами с соответствую-, щими выходами первого и второго блоков памяти, соединенными с соответствующими пятыми входами логи1еского блока, первый выход делителя частоты . соединен со счетным входом счетчика времени, вход - с выходом кварцевого генератора, второй и третий выходы соответственно с третьим и четвертым входами логического блока, четвертый выход - с третьим входом коммута,тора, соединенного выходами с соот

,

Изобретение относится к автоматике и вычиелительной технике и может быть использовано для контроля временных параметров.

Цель изобретения - расширение функциональных возможностей устройства.

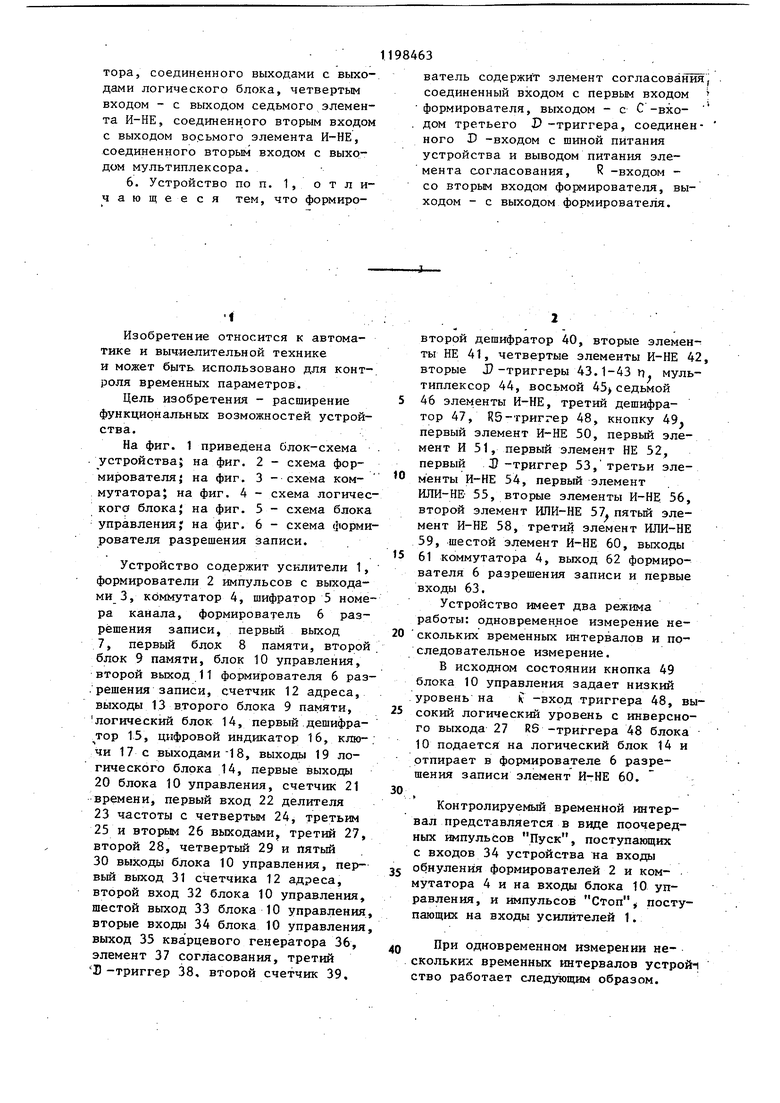

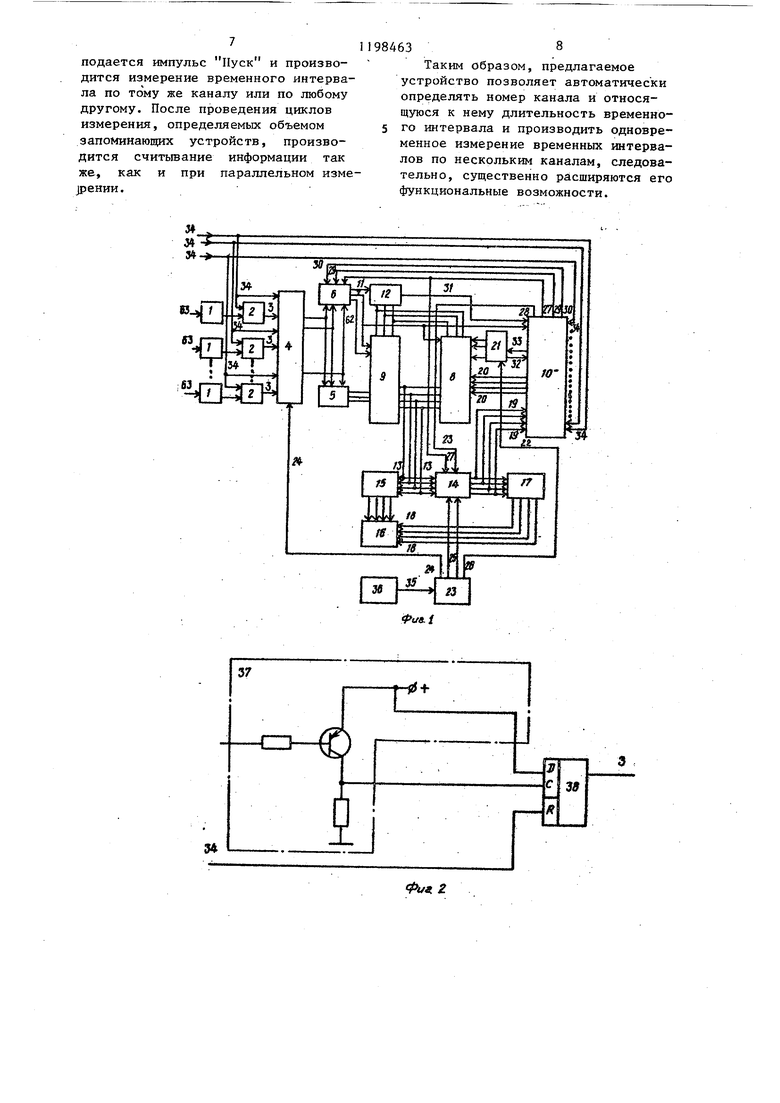

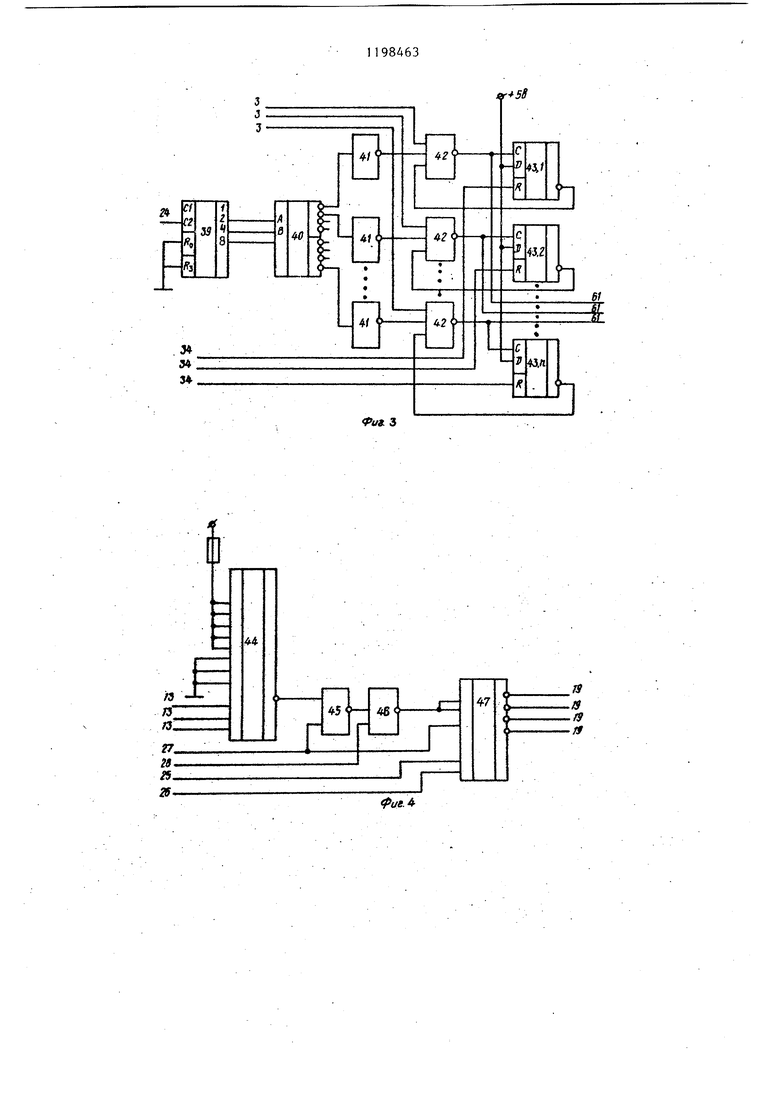

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - схема формирователя} на фиг. 3 - схема коммутатора; на фиг. 4 - схема логического блока; на фиг. 5 - схема блока управления на фиг. 6 - схема формирователя разрешения записи.

Устройство содержит усилители 1, формирователи 2 импульсов с выходами 3, ксзммутатор 4, шифратор 5 номера канала, формирователь 6 разрешения записи, первый выход 7, первый блок 8 памяти, второй блок 9 памяти, блок 10 управления, второй выход 11 формирователя 6 раз. решения записи, счетчик 12 адреса, выходы 13 второго блока 9 памяти, логический блок 14, первый.дешифра тор 15, цифровой индикатор 16, ключи 17 с выходами 18, выходы 19 логического блока 14, первые выходы 20 блока 10 управления, счетчик 21 времени, первый вход 22 делителя 23 частоты с четвертым 24, третьим 25 и вторым 26 выходами, третий 27, второй 28, четвертый 29 и пятый 30 выходы блока 10 управления, первьй выход 31 счетчика 12 адреса, второй вход 32 блока 10 управления, шестой выход 33 блока 10 управления вторые входы 34 блока 10 управления выход 35 кварцевого генератора 36, элемент 37 согласования, третий В -триггер 38. второй счетчик 39,

второй дешифратор 40, вторые элементы НЕ 41, четвертые элементы И-НЕ 42, вторые J -триггеры 43.1-43 л. мультиплексор 44, восьмой 45 седьмой

46 элементы И-НЕ, третий дешифратор 47, 1 5-триггер 48, кнопку 49 первый элемент И-НЕ 50, первый элемент И 51, первый элемент НЕ 52, первый 1 -триггер 53,третьи элементы И-НЕ 54, первый элемент

ИЛИ-НЕ- 55, вторые элементы И-НЕ. 56, второй элемент ИПИ-НЕ 57. пятьш элемент И-НЕ 58, третий элемент ИЛИ-НЕ 59, шестой элемент И-НЕ 60, выходы

61 коммутатора 4, выход 62 формирователя 6 разрешения записи и первые входы 63.

Устройство имеет два режима работы: одновременное измерение нескольких временных штepвaлoв и последовательное измерение.

В исходном состоянии кнопка 49 блока 10 управления задает низкий уровень на С -вход триггера 48, высокий логический уровень с инверсного выхода 27 R6 -триггера 48 блока 10 подается на логический блок 14 и отпирает в формирователе 6 разрешения записи элемент И-НЕ 60.

.

Контролируемый временной интервал представляется в виде поочередных импульсов Пуск, поступающих с входов 34 устройства на входы обнуления формирователей 2 и коммутатора 4 и на входы блока 10 управления, и импульсов Стоп% поступающих на входы усилителей 1.

При одновременном измерении нескольких временных интервалов устрой-i ство работает следующим образом.

3

Входы 34 Пуск соединены электри чески. В момент поступления импульса .Пуск по входу 34 происходит обнзление Ф -триггеров 38, 43.1-43. и 53, ас выхода элемента И 51 и выхода 33 блока 10 управления - счетчика 21 времени, который начинает отсчет времени. Низким логическим уровнем с прямого выхода 28 Л -триггера 53 блока 10 управления запирается элемент И-НЕ 46 в логическим блоке 14 и индикация запрещается. Низкие логические уровни с прямых выходов Л -триггеров 48 и 53 поступают на входа элемента И-НЕ 50, с выхода которого высокий логический уровень (с выхода 29 блока 10 управления) разрешает прохождение импульсов с выходов 61 коммутатора 4 через элемент ИЛИ-НЕ 57 в формирователь 6 разрешения записи. Низкий логический уровень с прямого выхода Л5 -триггера 53, пройдя через элементы ИЛИ-НЕ 54, отпирает элементы И-НЕ 56, а высокий логический уровень с инверсного выхода D -триггера 53 отпирает элемент 55 ИЛИ-НЕ. Тем самым дается разрешение на прохождение импульсов с выхода 7 формирователя 6 разрешения записи через элемент ИПИ-НЕ 55 и И-НЕ 56 и с выходов 20 блока 10 управления на входы разрешения считывания блока В памяти.

С выхода 30 блока 10 управления высокий логический уровень поступает на вход формирователя 6 разрешения записи, открьшая элементы И-НЕ 58 и ИЛИ-НЕ 59. Импульсы высокой частоты с делителя 23 частоты (с его выхода 24) поступают на коммутатор 4 и пройдя через счетчик 39, дешифратор 40 и элементы НЕ 41, производят поочередный опрос элементов И-НЕ 42. По окончании измеряемых интервалов на входные усилители с входов 63 поступают импулвсы Стоп от контролируемых устройств, после усиления поступающие на входы формирователей 2 импульсов, и, пройдя через элементы 37 согласования, переводят соответствующие 3J -триггеры 38 в состояние с высоким логическим уровнем, который с выходов 3 подается на входы коммутатора 4. Тем самым разрешается прохождение опрашивающего импульса с соответствующего элемента 41 НЕ через эле84634

мент И-НЕ 42 на счетный вход соответствующего 3 -триггера 43, а также с выходов 61 на входы шифратора 5 номера канала и формирователя 6 5 разрешения записи.

По заднему фронту опрашивающего (Импульса с выходов элемента НЕ 41 соответствующий 1 ;-триггер 43 переQ ключается и нулевым уровнем с инверс ного выхода дает запрет на элемент И-НЕ 42. Шифратор 5 номе.ра канала преобразует позиционньш код сработавшего канала, записанный в триггерах 43, в двоично-десятичный и подает его на информационные входы второго блока 9 памяти. Одновременно опрашивающий импульс с выхода элемента И-НЕ 42 поступает на один из

входов формирователя 6 разрешения записи и пройдя через элемент ИЛИ-НЕ 57 и И-НЕ 58, поступает с выхода 7 на входы разрешения записи блоков 8 и 9 памяти, а также на вход блока

. 10 управления и, пройдя через элементы 55 и 56 с выходов 20 поступает на входы разрешения считывания блока В памяти. С выхода элемента И-НЕ 58 через элементы ИЛИ-НЕ 59, И-НЕ 60 и выход 62 опрашивающий импульс поступает на вход разрешения считьгоания блока 9 памяти. Происходит запись номера сработавшего канала в блок 9 памяти и соответствующей ему длительности временного ицтер5 вала со счетчика 21 времени в блок 8 памяти. С выхода формирователя 6 на счетный вход счетчика 12 поступает опрашивающий импульс, по заднему фронту которого счетчик 12 nepeKjao4aeTCH

0 и на выходах его разрядов формируется адрес следующих ячеек памяти блоков 8 и 9. Таким образом, происходит запись в память блоков 8 и 9 всех номеров сработавших каналов

5 и соответствующих им длительностей временных интервалов, при этом каждому каналу присваивается свой адрес, по которому его номер и соответствующая ему длительность временного интервала иссируется в блоках 8 и 9 памяти. Счетчик 21 времени досчитывает до заполнения, при этом на выходе его последнего разряда появляется импульс, поступающий с выхода 32 на четвертый вход блока 10 управления и на 5 -вход 3) -триггера 33, устанавливая его в состояние с нулевым

51

логическим уровнем на инверсном выходе, который с выхода 30 поступает на вход формирователя 6 разрешения записи и запирает элемент И-НЕ 58. Дальнейшая запись в блоки 9 и 8 памяти запрещается. Высокий логический уровень с прямого выхода 15-триггера 53 отпирает элементы 50 и 54, а также с выхода 28 поступает на стробирующий вход логического блока 14, отпирая элемент И-НЕ 46. Низкий логический уровень с инверсного выхода S -триггера 53 пройдя через элемент ИЛИ-НЕ 55, отпирает элементы 56, при этом разрешается прохождение сигналов с выхода логического блока 14 (выходы 19) через элементы 54 блока 10 управления и с выходов 20 на входы разрешения считывания блока 8 памяти.

Считывание записанной информации происходит следующим образом.

Когда кнопка 49 в блоке 10 управления задает О на R -вход триггера 48, с выхода 27 дается разрешение на стробирующий вход логического блока 14, где отпирается элемент И-НЕ 45, и на второй стробирующий вход дешифратора 47. При этом разрешается индикация номера канала. разрешения с выхода 27 открывает также элемент И-НЕ 60 в формирователе 6 разрешения записи, с выхода которого низкий логический уровень поступает на вход разрешения считывания из.блока памяти 9, с выходов 13 которого двоично-десятичный код номера канала поступает на . входы дешифратора 15 и на вход логического блока :14, поступая на . управляющие, входы мультиплексора 44 на выходе которого при наличии информации в адресованной ячейке блока 9 памяти появляется низкий логический уровень, который, пройдя через элементы И-НЕ 45 и 46 отпирает дешифратор 47, на входы которого с выходов 25 и 26 делителя 23 частотыпоступают импульсы. Позиционный код с выходов дешифратора 47 управляет ключами 17, которые поочередно с выходов 18 включают разряды цифрового индикатора 16, на информационные входы которого подан код с выхода дешифратора 15. На цифровом индикаторе 16 высвечивается номер первого сработавшего канала.

984636

При переводе кнопки 47 в поло- . жение задания нуля 9-вход R б-триггера 48 устанавливается в 1

и

низкий логический уровень с его инверсного выхода 27 поступает на второй вход формирователя 6 разрешения записи, запирая элемент И-НЕ 60, тем самым запрещая считывание информации из блока 9, а также поступает

0 на вход логического блока 14, запирая элемент И-НЕ 45, тем самым отключая мультиплексор 44. Уровень с выхода 27 блока 10 управления подается на вход дешифратора 47, разрешая.

5 его работу. С выхода дешифратора 47 и выходов 19 логического блока 14 позиционный код управляет через ключи 17 разрядами цифрового индикатора 16, а также подается на входы

0 блока 10 управления и, пройдя через элементы И-НЕ 54 и 56, с выходов 20 подается на входы блока 8 памяти и осуществляет подекадный опрос блока 8 памяти. С выходов 13 блока 8

5 памяти информация поступает на дешифратор 15 и, пройдя через него, в виде кода поступает йа цифровой индикатор 16, а так как подекадный опрос первого блока 8 памяти

0 производится согласованно с включением разрядов цифрового индикатора 16, то происходит динамическая индикация длительности измеренного интервала времени, соответствующего контролируемому каналу. Для контроля следзгющих каналов кнопка 49 в блоке 10 управления переводится в исходное положение, RS-триггер 48 переключается в положение с низким логи-. ческим уровнем на прямом выходе. Перепад через элемент И-НЕ 50 с выхода 29 поступает на вход формирователя 6 разрешения, записи и пройдя через элемент ИЛИ-НЕ 57, с выхода 11 попадает на счетный вход счетчика 12 и переключает его в . следующее состояние, при этом проис.ходит индикация номера следующего канала. Кнопку 49 переключают до тех пор, пока не будут считаны все

номера каналов и соответствзтощие им длительности интервалов. При поочередном измерении временных интервалов команда Пуск на входы 34 задается так же, как и при па- 5 раллельном.измерении, а импульс Стоп поступает на входа усилителей 1 только по одному каналу в каждом цикле измерения. Затем снова

подается импульс Пуск и производится измерение временного интервала по же каналу или по любому другому. После проведения циклов измерения, определяемых объемом запоминающих устройств, производится считьгаание информации так же, как и при параллельном изме Jpeнии.

198463

Таким образом, предлагаемое устройство позволяет автоматически определять номер канала и относящуюся к нему длительность временного интервала и производить одновременное измерение временных интервалов по нескольким каналам, следовательно, существенно расширяются его функциональные возможности.

3

j

3

3 S. 3

| Электромагнитный ограничитель тока | 1926 |

|

SU9512A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля параметров | 1980 |

|

SU888078A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-12-15—Публикация

1984-05-07—Подача