венно с разрядными выходами регистра сдвига, установочный вход которого соединен с выходом четвертого элемента И, третий вход первого элемента И и второй вход третьего элемента И соединены с выходом третьего элемента ИЛИ, входы которого соеднены соответственно с разрядными выходами последовательно-параллельного регистра, выход старшего разряда которого соединен с входом установки в 1 -триггера, причем выходы остатка первого шифратора цифр частного соединены с соответствующими входами остатка второго шифратора цифр частного, выходы которого соединены с первыми входами соответствующих разрядов первого и зторого регистров остатка, входы остатка первого шифратора цифр частного соединены с соответствующими выходами первого и второго регистров остатка входы кратных делителя первого и второго шифраторов цифр частного соединены с выходами соответствующих разрядов первого вспомогательного регистра, разрядные входы первого и второго шифраторов цифр частного соединены с соответствующими выходами второго вспо огательного регистра входы знака делителя первого и второго шифраторов цифр частного соединены с выходом знакового разряда первого вспомогательного регистра, вход знака остатка второго иифратора цифр частного соединен с выходом младшей цифры частного первого пгафратора цифр частного, а вход -знака остатка первого шифратора цифр частного соединен с выходом триггера знака остатка, выходы цифр частного шифраторов цифр частного являются соответствующими выходами цифр частного устройства, выход младшей цифры частного второго шифратора циф частного соединен с первым входом триггера знака остатка-, информационные входы первого вспомогательного регистра соединены с соответствующими выходами блока смещения делителя, информационные входы которого соединены с соответствующими выходами блока регистров делителя, а вход управления смещением подключен к выходу делителя блока определения знака частного, информационные входь первого вспомогательного регистра

соединены с соответствующими информационными выходами блока регистров разрядности, информационные входы второго вспомогательного регистра соединены с соответствующими информационными выходами блока регистров разрядности, вход знака и вход переполнения делителя блока определения знака частного соединены соответственно с выходами разрядов знака и переполнения делителя блока- регистров делителя, а вход знака и вход переполнения делимого блока определения знака частного соединены соответственно с выходами разрядов знака и переполнения делимого блока регистров делимого, информационные входы смещения делимого блока смещения делимого соединень с соответствующими выходами делимого блока регистров делимого, а информационные входы инверсии блока смещения делимого соединены с соответствующими информационными выходами блока регистров разрядности,, выход знака делимого блока определения знака частного соединен с вторым информационным входом триггера знака остатка, выходы управления инверсией и смещением делимого блока определения знака частного соединены соответственно с управляющими входами инверсии и смещения делимого блока смещения делимого, выход знака частного блока- определения знака частного является.выходом знака частного устройства прямые и инверсные информационнью выходы делимого блока смещения делимого соединены соответственно; с вторыми информационными входами.первого и второго регистров остатков, входы блокировки которых соединены с соответствующими управляющими выходами блока регистров разрядности, входы управления первого вспомогательного регистраj первого и второго регистров остатка, второго вспомогательного регистра,блока определения знака частного и триггера знака остатка соединены с выходом второго элемента ИЛИ блока управления, установочные входы последовательно-параллельного регистра блока управления соединены с соответствующими выходами разрядности блока регистров разрядности, разрядные выходы сдвигового регистра блока управления соединены

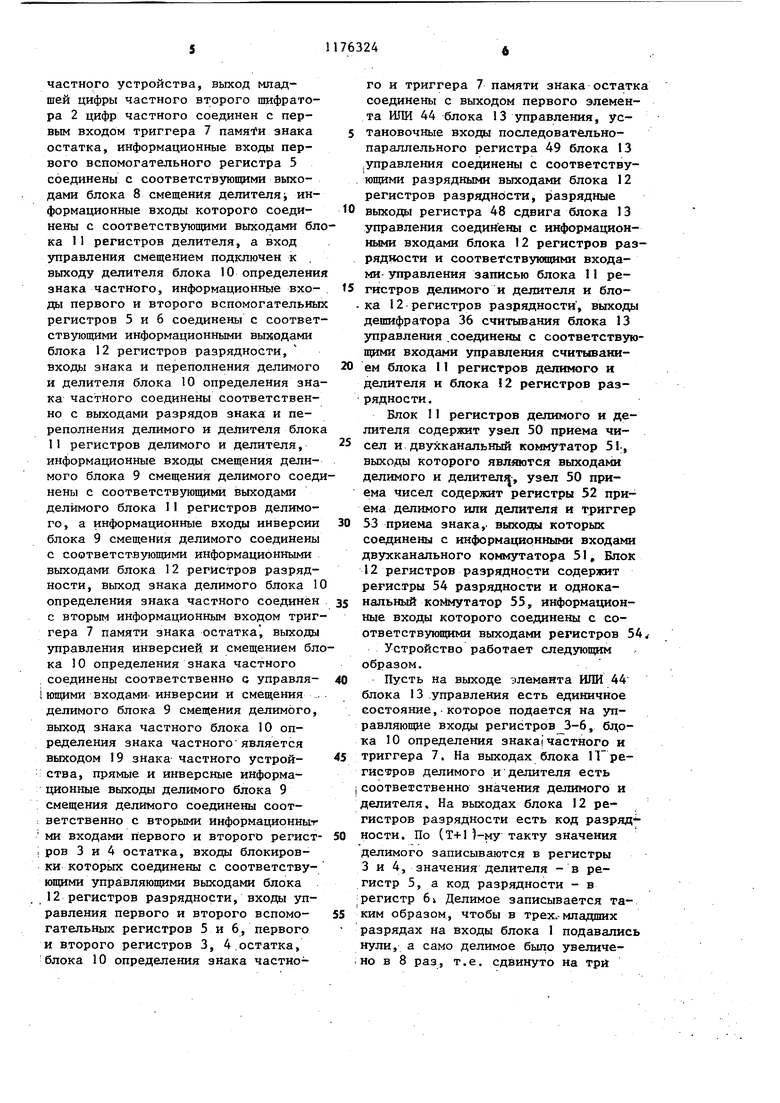

с информационными входами блока регистров разрядности и с соответствующими входами выбора записи блока регистров делимого и делителя, выходы дешифратора записи блока управления соединены с соответствующими входами управления записью блока регистров делимого и делителя и блока регистров разрядности, выходь дешифратора считывания блока управления соединены -с соответствующими входами управления считыванием блока регистров делимого и делителя и блока регистров разрядности, блок регистров делимого и делителя содержит узел приема чисел и двухканальный коммутатор, выходы которого являются выходами делимого и делителя, узел приема чисел содержит регистры приема делимого, триггер приема знака делимого, регистры : приема делителя, триггер приема знака делителя, выходы которых соединены с информационными входами двухканального коммутатора, управдяющие входы которого являются входами управления считьгоанием блока регистров делимого и делители,- входы выбора соответствующих разряг дов всех регистров приема делимого и делителя и триггеров приема знаков делимого и делителя объединены

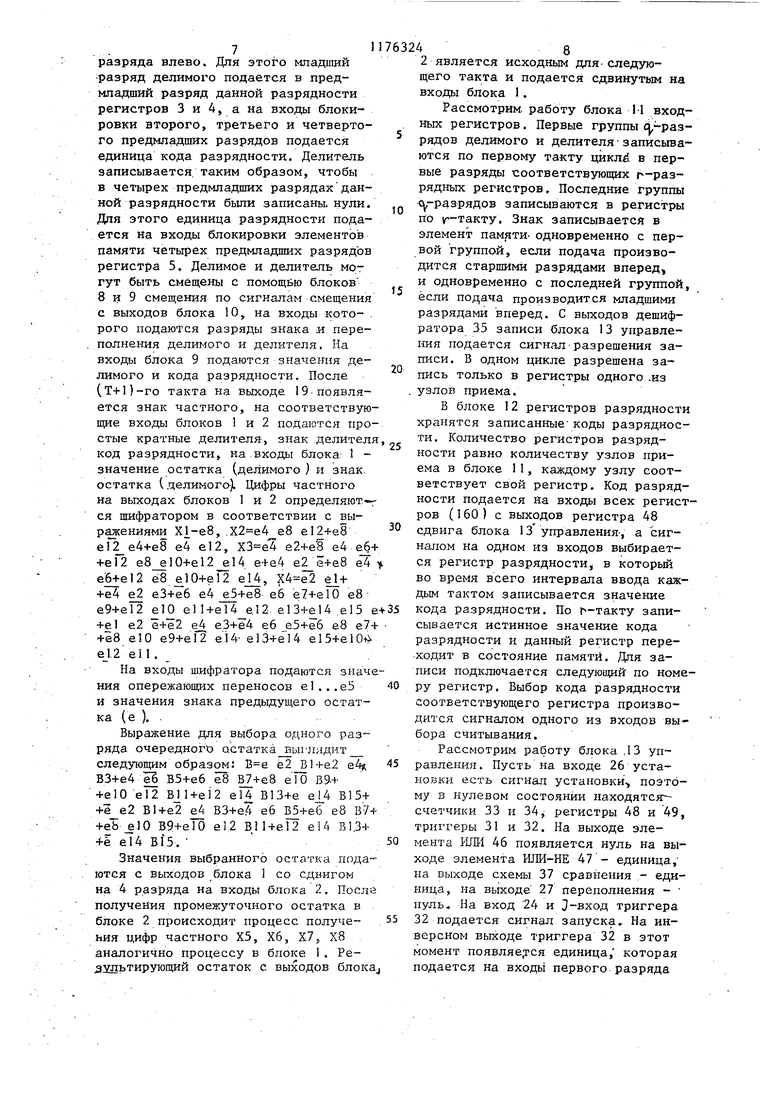

и являются входами выбора записи блока регистров делимого и делителя, входы разрешения регистров приема делимого иделителя и триггеров приема знаков делимого и делителя о(5ъединены и являются входами управления записью блока регистров делимого и делителя, входы направления ввода регистров приема делимого и триггера приема знака делимого объединены и являются входом направления ввода делимого блока регистров делимого и делителя вход направления ввода регистров приема делителя к триггера приема знака делителя объединены и являются входом направления ввода делителя блока регистров делимого и делителя, блок регистров разрядности содержит регистры разрядности и одноканальный коммутатор, выходы которого являются выходами блока регистров разрядности, а управляющие входы являются входами управления считывания блока регистров разрядности, информационт 1е входы одноканального переключателя соединены с соответствующими выходами регистров разрядности, информационные входы соответствующих разрядов регистров разрядности объединены и йвляются информационными входами блока регистров разрядности, а входы разрешения регистров разрядности являются входами управления записью блока регистров разрядности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок регистров делимого и делителя и первый шифратор цифр частного, отличающееся тем, что, с целью повьшения быстроде лствия, в него введены второй шифратор цифр частного, первый и второй регистры остатка, первый и второй вспомогательные регистрыi триггер памяти знака остатка, блок смещения делителя, блок смещения делимого, блок, определения знака частного, блок регистров разрядности и блок управления, содержащий генератор тактовых импульсов,и-триггер, JK-триггер, счетчик записи-, счетчик считывания, дешифратор записи, дешифратор . считывания, схему сравнения, первый, второй, третий, четвертый, пятый и шестой элементы И, первый, второй и ; третий элементы ИЛИ, элемент ИЛИ-НЕ, регистр сдвига, последовательно-паргллельный регистр, тактовый вход которого соединение тактовым входом сдвигового регистра и с выходом генератора тактовых импульсов , выход 1-триггера соединен с первыми входами первого и второго элементов И, первого элемента ИЛИ и счетным входом счетчика считывания, выход которого соединен с входом дешифратора считывания и входами первой группы схемы сравнения, входы установки в О D-триггера, Лк-триггера, последовательно-параллельного регистра и счетчиков записи и считывания соединены с установочным входом блока управления, прямой выход 3liJ-Tp«rrepa соединен с первыми входами четвертого и шестого элементов И и входом установки в О сдвигового регистра, управляющий вход блока управления сое динен с вторьпч входом шестого элемента И, выход которого соединен с K- входом JK-триггера, вторым входомпервого элемента И и счетным входом (Л счетчика записи, выход которого соес динен с входом дешифратора записи и входами второй группы схемы сравнения, выход которой соединен с вторыми входами второго и третьего элементов И и четвертым входом первого элемента И, второй вход первого эле мента ИЛИ соединен с первым входом Од второго элемента ИЛИ и с выходом 00 первого элемента И, выход второго го элемента И соединен с вторым вхо1 дом второго элемента ИЛИ, выход которого соединен с входом последовательной записи последовательно-параллельного регистра, выход третьего элемента И соединен с управляющим входом дешифратора записи и с первым входом пятого элемента И, второй вход которого соединен с установочным входом блока управления, а выход - с J-входом ЗК-триггера, второй вход четвертого элемента И соединен с выходом элемента ШЭД-НЕ, входы которого соединены соответст-

I

Изобретение относится к вычис.лительной технике и мОжет быть использовано при построении быстродействующих вычислительных.систем.

Цель изобретения - повьшение быстродействия устройства;

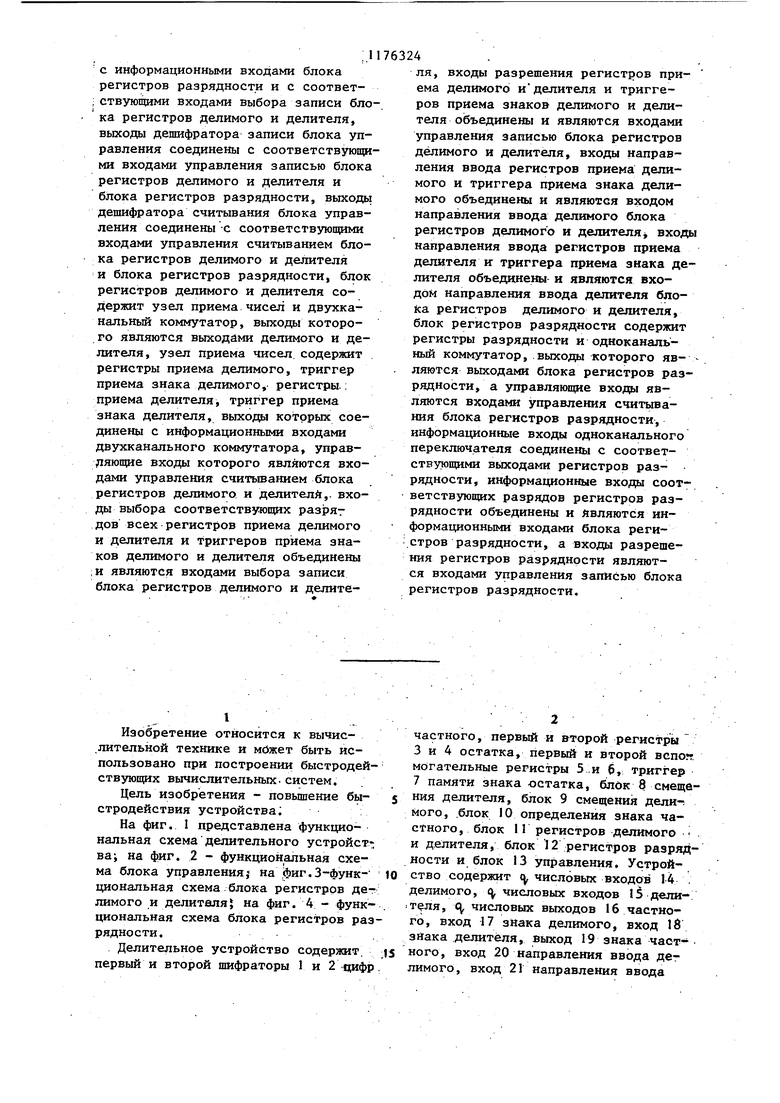

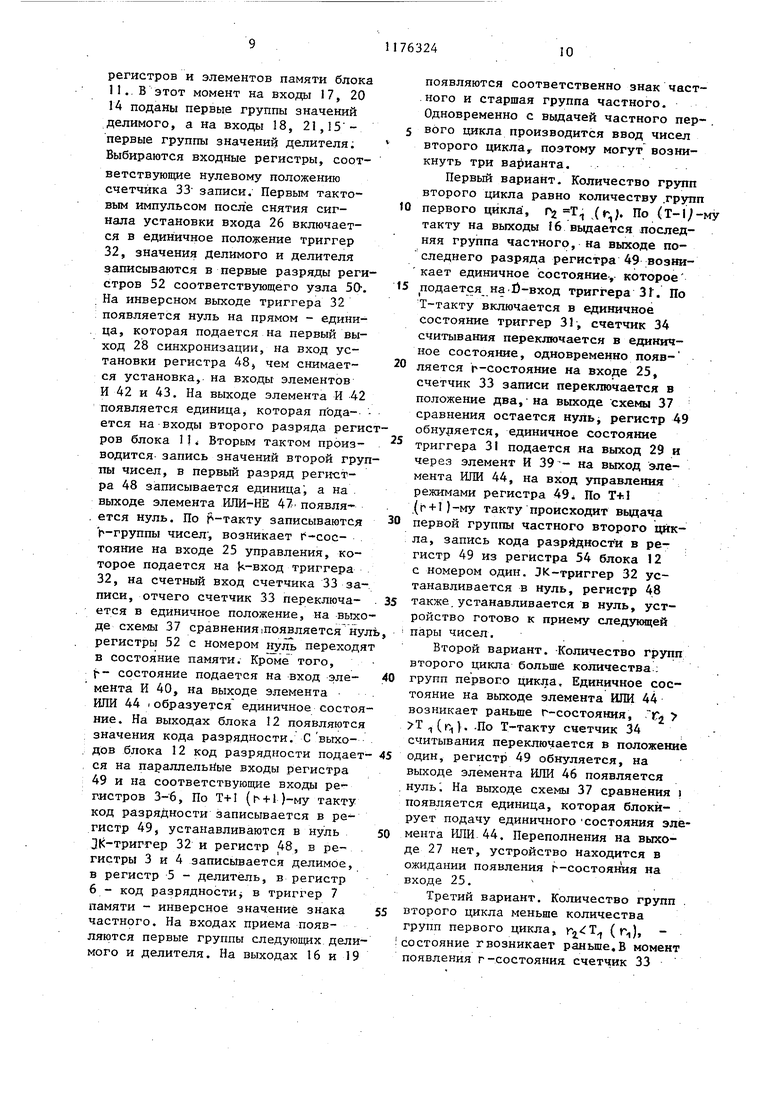

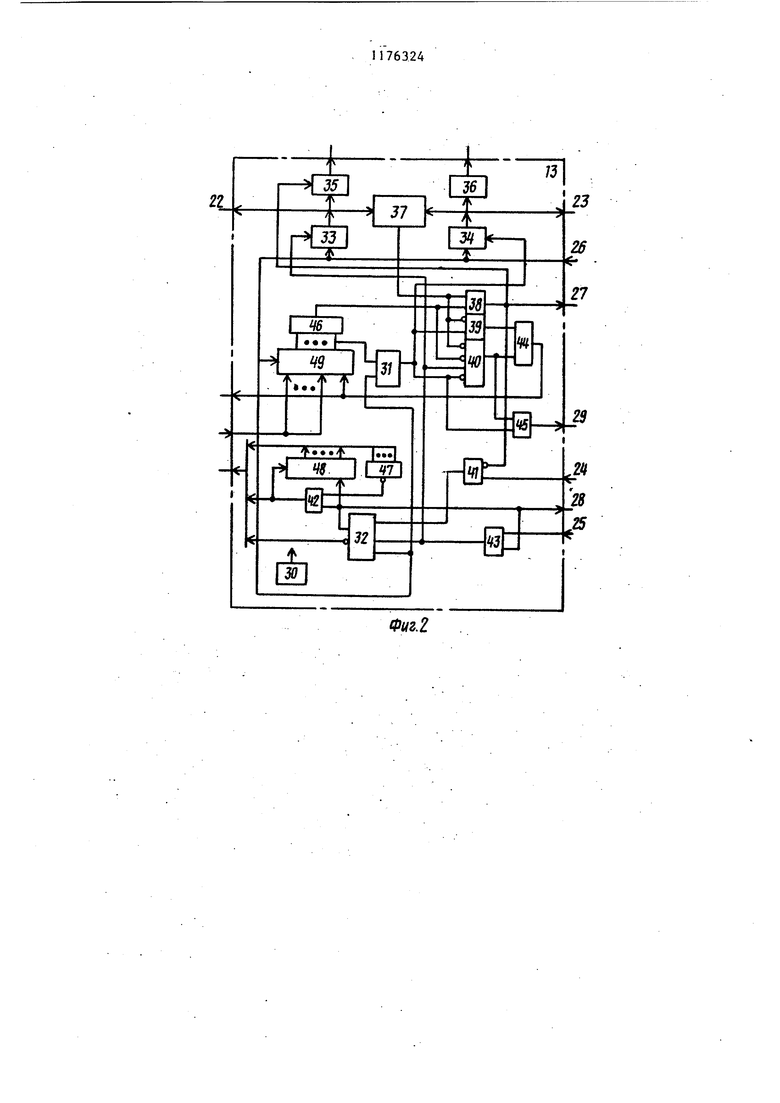

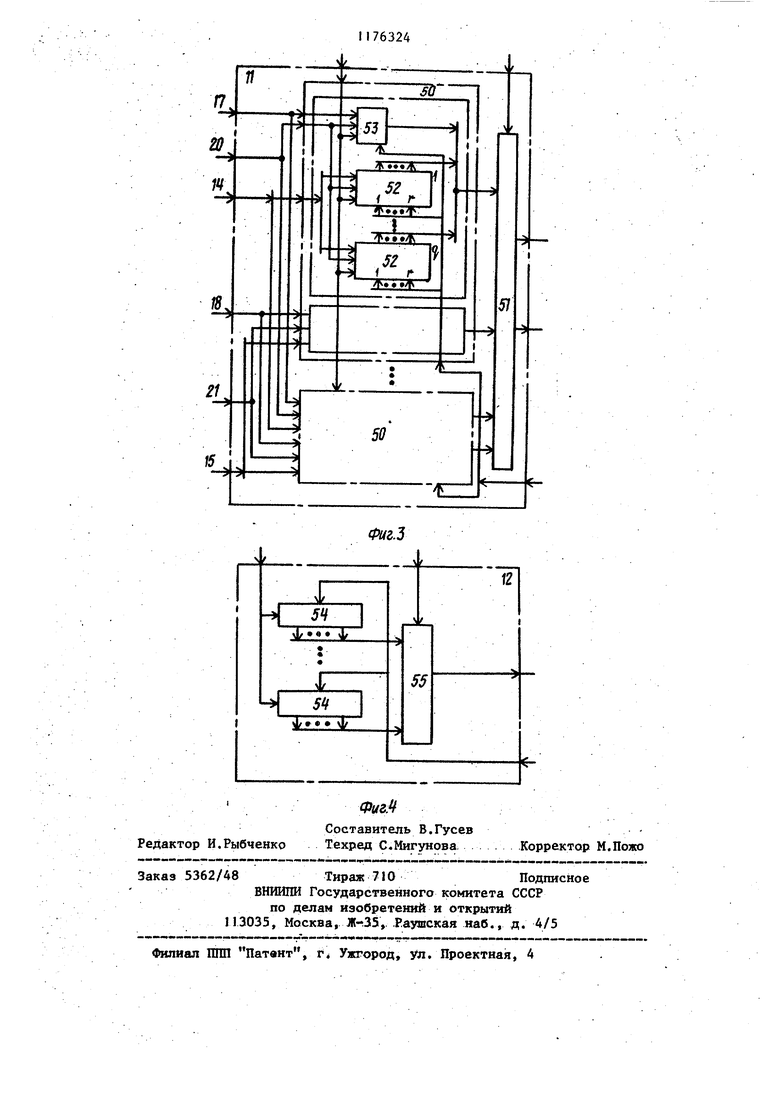

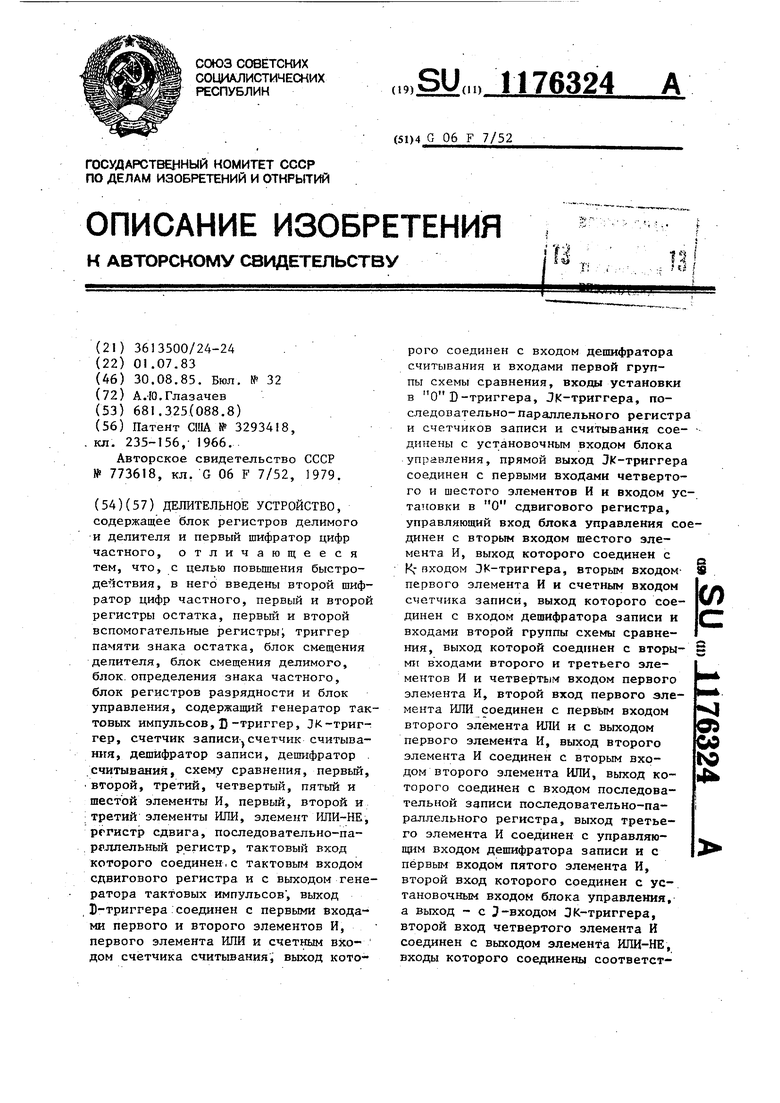

На фиг. 1 представлена функциональная схема делительного устройства j на фиг. 2 - функциональная схема блока управления, на ,фиг.3-функциональная схема блока регистров делимого и делителяJ на фиг. 4 - функциональная схема блока регистров разрядности.

Делительное устройство содержит первый и второй шифраторы 1 и 2 цифр

частного, первый и второй регистры 3 и 4 остатка, первый и второй вспогт. могательные регистры 5 и 6, триггер 7 памяти знака остатка, блок 8 смещения делителя, блок 9 смещения делимого, .блок 10 определения знака частного, блок 1 Г регистров делимого и делителя, блок J2 регистров разрядности и блок 13 управления. Устройство содержит ( числовых входов 14 делимого, числовых входов 1 дели-Г : , с числовых выходов 16 частного, вход 17 знака делимого, вход 18 знака делителя, выход 19 знака частного, вход 20 направления ввода делимого, вход 2 Г направления ввода

3

делителя, вькоды 22 счетчика записи/ выходы 23 счетчика считывания, вход 24 запуска, вход 25 управления, вход 26 установки, выход 27 переполнения, первый и второй выходы 28 и 29 синхронизации.

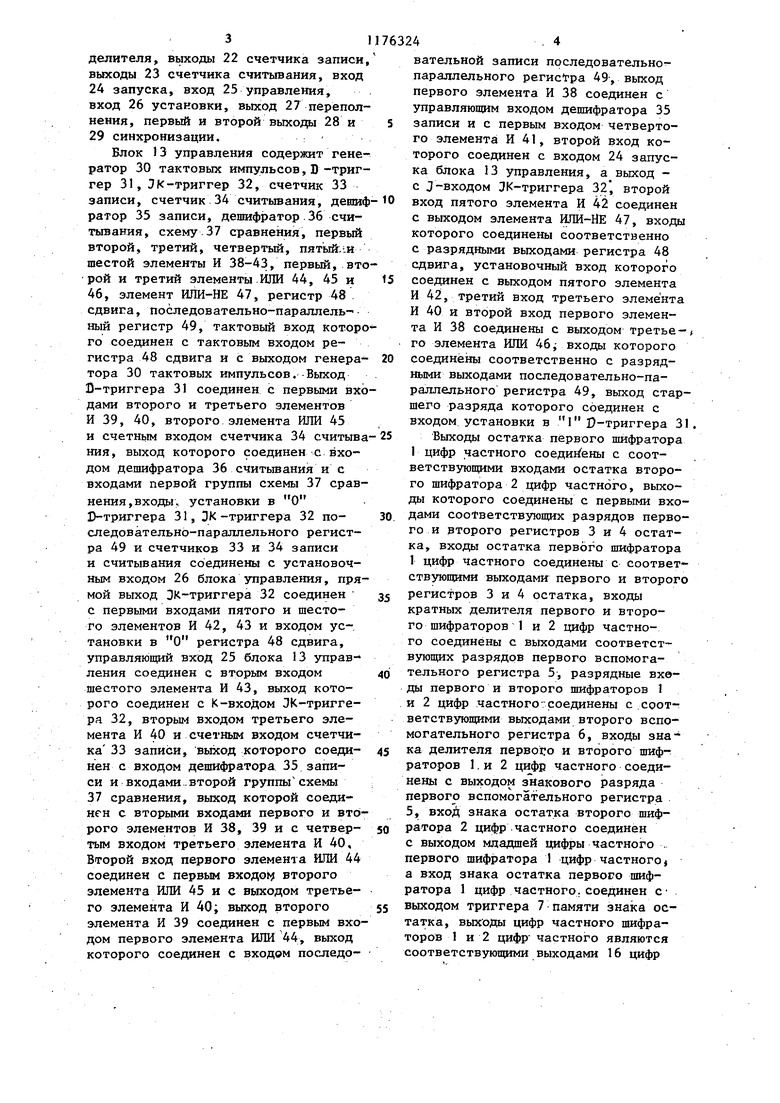

Блок 3 управления содержит генератор 30 тактовых импульсов,D -триггер 31, JK-триггер 32, счетчик 33 записи, счетчик 34 считывания, дешифратор 35 записи, дешифратор.36 считывания, схему.37 сравнения, первый второй, третий, четвертый, пять1й.-:и шестой элементы И 38-43, первый, второй и третий элементы ИЛИ 44, 45 и 46, элемент Ш1И-НЕ 47, регистр 48 сдвига, последовательно-параллельный регистр 49, тактовый вход которого соединен с тактовым входом регистра 48 сдвига и с выходом генератора 30 тактовых импульсов. Выход D-триггера 31 соединен с первыми входами второго и третьего элементов И 39, 40, второго элемента ИЛИ 45 и счетньм входом счетчика 34 считывания, выход которого соединен с входом дешифратора 36 считьгоания и с входами первой группы схемы 37 сравнения, входы, установки в О D-триггера 31, ЗК-триггера 32 последовательно-параллельного регистра 49 и счетчиков 33 и 34 записи и считывания соединены с установочным входом 26 блока управления, прямой выход ЗК-триггера 32 соединен с первыми входами пятого и шестого элементов И 42, 43 и входом установки в О регистра 48 сдвига, управляющий вход 25 блока 13 управления соединен с вторым входом шестого элемента И 43, выход которого соединен с К-входом ЭК-триггера 32, вторым входом третьего элемента И 40 и счетным входом счетчика 33 записи, выход которого соединен с входом дешифратора 35 записи и входами.второй группьГ схемы 37 сравнения, выход которой соединен с вторыми входами первого и втЬрого элементов И 38, 39 и с четвертым входом третьего элемента И 40, Второй вход первого элемента ИЛИ 44 соединен с первым входоЬ второго элемента ИЛИ 45 и с вьпсодом третьего элемента И 40; выход второго элемента И 39 соединен с первым входом первого элемента ИЛИ 44, выход которого соединен с входом последо244

вательной записи последовательнопараллельного регисгра 49, выход первого элемента И 38 соединен с управляющим входом дешифратора 35 записи и с первым входом четвертого элемента И 41, второй вход которого соединен с входом 24 запуска блока 13 управления, а выход с J-входом JK-триггера 32, второй

вход пятого элемента И 42 соединен с выходом элемента ИЛИ-НЕ 47, входы которого соединены соответственно с разрядными выходами регистра 48 сдвига, установочный вход которого

соединен с выходом пятого элемента И 42, третий вход третьего элемента И 40 и второй вход первого элемента И 38 соединены с выходом третье- го элемента ИЛИ 46 j входы которого

соединены соответственно с разрядными выходами последовательно-параллельного регистра 49, выход старшего разряда которого соединен с входом установки в 1 D-триггера 31.

Выходы остатка первого шифратора 1 цифр частного соеди1 ены с соответствзтопщми входами остатка второго шифратора 2 цифр частного, выходы которого соединены с первьми входами соответствзпощих разрядов первого и эторого регистров 3 и 4 остатка, входы остатка первого шифратора 1 цифр частного соединены с соответствующими выходами первого и второго

регистров 3 и 4 остатка, входы кратных делителя первого и второго шифраторов 1 и 2 цифр частного соединены с выходами соответствующих разрядов первого вспомогательного регистра 5, разрядные вхеды первого и второго шифраторов 1 и 2 цифр частного соединены с соответствующими выходами второго вспомогательного регистра 6, вхоДы знака делителя первого и второго шифраторов 1, и 2 цифр частного соединены с выходом знакового разряда первого вспомогательного регистра 5, вход знака остатка второго шифратора 2 цифр частного соединен с выходом младшей цифры частного первого шифратора 1 цифр частногоj а вход знака остатка первого шифратора 1 цифр частного.соединен С

выходом триггера 7 памяти знака остатка, выходы цифр частного шифраторов 1 и 2 ЦИФР частного являются соответствующими выходами 16 цифр частного устройства, выход младшей цифры частного второго шифратора 2 цифр частного соединен с первым входом триггера 7 памяти знака остатка, информационные входы первого вспомогательного регистра 5 соединены с соответствующими выходами блока 8 смещения делителяj информационные входы которого соединены с соответствующими выходами бл ка 11 регистров делителя, а вход зшравления смещением подключен к , выходу делителя блока 10 определени знака частного, информационные входы первого и второго вспомогательны регистров 5 и 6 соединены с соответ ствующими информационными вьп5одами блока 12 регистров разрядности, входы знака и переполнения делимого и делителя блока 10 определения зна ка частного соединены соответственно с выходами разрядов знака и переполнения делимого и делителя блок 11регистров делимого и делителя, информационные входы смещения делимого блока 9 смещения делимого соед нены с соответствующими выходами делимого блока 11 регистров делимого, а информационные входы инверсии блока 9 смещения делимого соединены с соответствующими информационными выходами блока 12 регистров разрядности, выход знака делимого блока 1 определения знака частного соединен с вторым информационным входом триг гера 7 памяти знака остатка , выходы управления инверсией и смещением бл ка 10 определения знака частного соединены соответственно о управляющими входами- инверсии и смещения . делимого блока 9 смещения делимого, выход знака частного блока 10 определения знака частного является выходом 19 знака частного устрой: ства, прямые и инверсные информационные выходы делимого блока 9 смещения делимого соединены соот: ветственно с вторыми информационны.г ми входами первого и второго регист 1 ров 3 и 4 остатка, входы блокировки которых соединены с соответствующими управляющими выходами блока 12регистров разрядности, входы управления первого и второго вспомогательных регистров 5 и 6, первого и второго регистров 3, 4 остатка, Яблока 10 определения знака частного и триггера 7 памяти знака остатка соединены с выходом первого элемента ИЛИ 44 блока 13 управления, установочные входы последовательнопараллельного регистра 49 блока 13 управления соединены с соответствующими разрядными выходами блока 12 регистров разрядности, разрядные выходы регистра 48 сдвига блока 13 управления соединены с информационными входами блока 12 регистров разрядности и соответствующими входами- управления записью блока 11 регистров делимого и делителя и блока 12 регистров разрядности , выходы дешифратора 36 считывания блока 13 управления .соединены с соответствующими входами управления считыванием блока 11 регистров делимого и делителя и блока 2 регистров разрядности. Блок 11 регистров делимого и делителя содержит узел 50 приема чисел и двухканальный коммутатор 51-, выходы которого являются выходами делимого и делителя, узел 50 приема чисел содержит регистры 52 приема делимого или делителя и триггер 53 приема знака,, выходы которых соединены с информационными входами двухканального коммутатора 51, Блок 12 регистров разрядности содержит регистры 54 разрядности и одноканальный коммутатор 55, информационные входы которого соединены с соответствукйцими выходами регистров 54 Устройство работает следующим образом. Пусть на выходе элемента ШШ 44 блока 13 управления есть единичное состояние, которое подается на управляющие входы регистров 3-6, бдока 10 определения знака частного и триггера 7. На выходах блока П регистров делимого и делителя есть соответственно значения делимого и делителя. На выходах блока 12 регистров разрядности есть код разряд- ности. По (Т+1)-му такту значения делимого записываются в регистры 3 и 4, значения делителя - в регистр 5, а код разрядности - в регистр 6i Делимое записывается таКИМ образом, чтобы в трех -мпадщих разрядах на входы блока 1 подавались нули, а само делимое было увеличено в 8 раз, т.е. сдвинуто на три разряда влево. Для этого младший разряд делимого подается в предмладший разряд данной разрядности регистров 3 и 4, а на входы блокировки второго, третьего и четвертого предмладших разрядов подается единица кода разрядности. Делитель записывается/таким образом, чтобы в четырех предмладших разрядахданной разрядности бьши записаны, нули, Для этого единица разрядности подается на входы блокировки элементов памяти четьфех предмладших разрядов регистра 5, Делимое и делитапь могут быть смещены с помощью блоков 8 и 9 смещения по сигналам смещения с выходов блока 10, на входы котороге подаются разряды знака и переполнения делимого и делителя. На входы блока 9 подаются значения делимого и кода разрядности. После (Т+1)-го такта на выходе 19-появляется знак частного, на соответствую щие входы блоков 1 и 2 подаются про стые кратные делителя, знак делител код разрядности, на.входы блока 1 значение остатка (делимого } и знак. остатка (делимого). Цифры частного на выходах блоков 1 и 2 определяются шифратором в соответствии с выражениями Xi-e8,. el2+e8 el e4+e8 е4 el2, е2+е8 е4 еб +el2 e8 elO+el2 14 е+е4 е4 ei6+el2 ё8 lO+el2 ej, +е4 е2 еЗ+еб е4 е5+е8 е6 e7+elO еВ e9+el2 elO el l+el4 el2 el el5 +el e2 ё+ё2 e3+i4 е6 еЗ+ёб еВ еУ +е8 el О e9+el2 el3+el4 el5+elOti ell . На входы шифратора подаются знач ния опережающих переносов el...e5 и значения знака предьщущего остатка (е ). . Выражение для выбора однох о разряда очередного остатка выглядит следующим образом: е2 В1-не2 е4 В3+е4 е| В5+е6 ё8 В7+е8 еТО B9.-t +е 10 е 1 2 BJ 1 +е 1 2 е 14 В1 3+е е 4 В15+ В1+е2 е4 В3+е4 е6 В5+е(Г еВ В7 В9+е10 el2 В,П+е12 el4 В1.3+ +ё el4 В15. Значения выбранного остатка пода ются с выходов блока 1 со сдвигом на 4 разряда на входы блока 2, Посл получения промежуточного остатка в блоке 2 происходит процесс получения цифр частного Х5, Хб, X7j, ХВ аналогично процессу в блоке 1. Результирующий остаток с выходов блoк 1 2 является исходным для- следующего такта и подается сдвинутым на входы блока 1. Рассмотрим работу блока 1-1 входных регистров. Первые группы cj,pa3рядов делимого и делителязаписьгааются по первому такту цикли в первые разряды соответствующих г-разрядных регистров. Последние группы су-разрядов записываются в регистры по г-такту. Знак записывается в элемент памяти- одновременно с первой группой, если подача производится старшими разрядами вперед, и одновременно с последней группой, если подача производится младшими разрядами вперед. С выходов дешифратора 35 записи блока 13 управлеIiия подается сигнал разрешения записи. В одном цикле разрешена запись только в регистры одного из узлов приема. В блоке 12 регистров разрядности хранятся записанные коды разрядности. Количество регистров разрядности равно количеству узлов приема в блоке 11, каждому узлу соответствует свой регистр. Код разрядности подается на входы всех регистров (160) с выходов регистра 48 сдвига блока 13 управления-, а сигналом на одном из входов выбирается регистр разрядности в который во время всего интервала ввода каждым тактом записывается значение кода разрядности. По г-такту записывается истинное значение кода разрядности и данный регистр пере.ходит в состояние памяти. Для записи подключается следующий по номеру регистр. Выбор кода разрядности соответствующего регистра производится сигналом одного из входов выбора считывания. Рассмотрим работу блока .13 управления. Пусть на входе 26 установки есть сигнал установки поэтому в нулевом состоянии находятся-счетчики 33 и 34, регистры 48 и 49, триггеры 31 и 32. На выходе элемента ИЛИ 46 появляется нуль на выходе элемента ИЛИ-НЕ 47 - единица, на выходе схемы 37 сравнения .- единица, на выходе 27 переполнения пуль. На вход 24 и J-вход триггера 32 подается сигнал запуска.. На инверсном выходе триггера 32 в этот момент появляе,тся единица, которая подается на входы первого разряда регистров и элементов памяти блока П.. В этот момент на входы 17, 20 14 поданы первые группы значений делимого, а на входы 18, 21,15первые группы значений делителя; Выбираются входные регистры, соответствующие нулевому положению счетчика 33 записи. Первым тактовым импульсом после снятия сигнала установки входа 26 включается в единичное положение триггер 32, значения делимого и делителя записываются в первые разряды реги стров 52 соответствующего узла ЗО-. На инверсном выходе триггера 32 появляется нуль на прямом - единица, которая подается на первый выход 2:8 синхронизации, на вход установки регистра 48j чем снимается установка, на входы элементов И 42 и 43. На выходе элемента И 42 появляется единица, которая подается на входы второго разряда реги ров блока 11i Вторым тактом производится- запись значений второй гру пы чисел, в первый разряд реги-стра 48 зiaпиcывaeтcя единица, а на выходе элемента ИЛИ-НЕ 47-появляется нуль. По р-такту записываются Г-группы чисел , возникает г-состояние на входе 25 управления, которое подается на К-вход триггера 32, на счетный вход счетчика 33 за писи, отчего счетчик 33 переключается в единичное положение, на вых де схемы 37 сравнения Появляется ну регистры 52 с номером нуль переход в состояние памяти. Кроме того, J-- состояние подается на вход элемента И 40, на выходе элемента ИЛИ 44 I образуется единичное состо ние. На выходах блока 12 появляютс значения кода разрядности. Свыходов блока 12 код разрядности подае ся на параллельные входы регистра 49 и на соответствующие входы регистров 3-6, По Т+1 (h + l )-му такту код разрядности записывается в регистр 49, устанавливаются в нуль jK-триггер 32 и регистр 48, в регистры 3 и 4 записывается делимое, в регистр 5 - делитель, в регистр 6 - код разрядностиi в триггер 7 памяти - инверсное значение знака частного. На входах приема появляются первые группы следующих дел мого и делителя. На выходах 16 и 1 появляются соответственно знак частного и старшая группа частного. Одновременно с вьщачей частного пер- . вого цикла производится ввод чисел второго 1Д1кла,. поэтому могут возникнуть три варианта. Первый вариант. Количество групп второго цикла равно количеству .групп первого цикла , Г Т, (г-). По ( такту на выходы 16 выдается последняя группа частного, на выходе последнего разряда регистра 49 возникает единичное состояние, которое подается наЙ-вход триггера 3Г. По Т-такту включается в единичное состояние триггер 31, счетчик 34 считывания переключается в единичное состояние, одновременно появляется г-состояние на входе 25, счетчик 33 записи переключается в положение два, на выходе схемы 37 сравнения остается нуль регистр 49 обнуляется, единичное состояние триггера 31 подается на выход 29 и через элемент И 39 - на выход элемента ИЛИ 44, на вход управления режимами регистра 49 По (г +1)-му такту происходит вьщача первой группы частного второго цикла, запись кода разрйдности в регистр 49 из регистра 54 блока 12 с номерам один. ЛК-триггер 32 устанавливается в куль, регистр 48 также устанавливается в нуль, устройство готово к приему след5гннцей пары чисел. Второй вариант. Количество групп второго цикла больше количества ; групп первого цикла. Единичное состояние на выходе элемента ИЛИ 44 возникает раньше г-состояшця, Т(г-,). -По Т-такту счетчик 34 считывания переключается в положение один, регистр 49 обнуляется, на выходе элемента ШШ 46 появляется нуль; На выходе схемы 37 сравнения i появляется единица, которая блоки- . рует подачу единичного состояния элемента ИЛИ-44. Переполнения на выходе 27 нет, устройство находится в ожидании появления г-состояния на входе 25. Третий вариант. Количество групп . второго цикла меньше количества групп первого цикла, () состояние гвозникает раньше,В момент появления г-состояния счетчик 33 записи переключается I в положение два, на выходе схемы 37 сравнения о танетсй нуль, единичное состояние на выходе элемента ИЛИ 44 не возникает Код разрядности с выходов регистра 48 блока 13 каждым тактом цикла ввода записывается в регистр 54 блока 12 с номером один, в котором после г-такта запоминается. Есл подряд приходит несколько Г-состояний и в какой-то момент счетчик 33 записи сравнивается со счетчиком 34 считывания, на выходе схемы 37 сравнения появляется единица,а еди ничное состояние в триггере 31 не возникает, в регистре 49 обязательно будет единица, на выходе зле.мента ИЛИ 46 также будет единица В этом случае на выходе элемента И 38 появляется сигнал переполнения который подается на выход 27,на вход блокировки дешифратора 35 записи, на вход запрета.элемента 412 И 41, чем запрещается запись в регистры блоков 11 и 12, подача сигнала запуска на вход 24, Вводследующих чисел прекращается.- По (г+1/)-му такту обнуляются триггер 32 и регистр 48. Вьщача предыдущего частного продолжается, и по Т-такту переключается счетчик 34 считьшания, обнуляется регистр 49. На выходе схемы 37 сравнения возникает нуль,- снимается сигнал переполнения и возникает единичное состояние- на выходе элемента ИЛИ 44, разрешена подача сигнала запуска. Следующим(Т+1)-м тактом начинается выдача нового частного, в регистры блоков 11 и 12по положению счетчика 33 записи вводятся первые группы чисел нового цикла, J 1 -триггер 32 включается .в единичное .состояние. Первая группа чисел записывается первым прищедшим после снятия сигнала переполнения тактом.

77

| Патент США № 3293418, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

Авторы

Даты

1985-08-30—Публикация

1983-07-01—Подача