1

Изобретение относится к вычислиIтельной технике, а именно к устройствам для записи информации в оперативную память, и может быть использовано в координатных культах ввода, информации.

Целью изобретения является повышение быстродействия устройства.

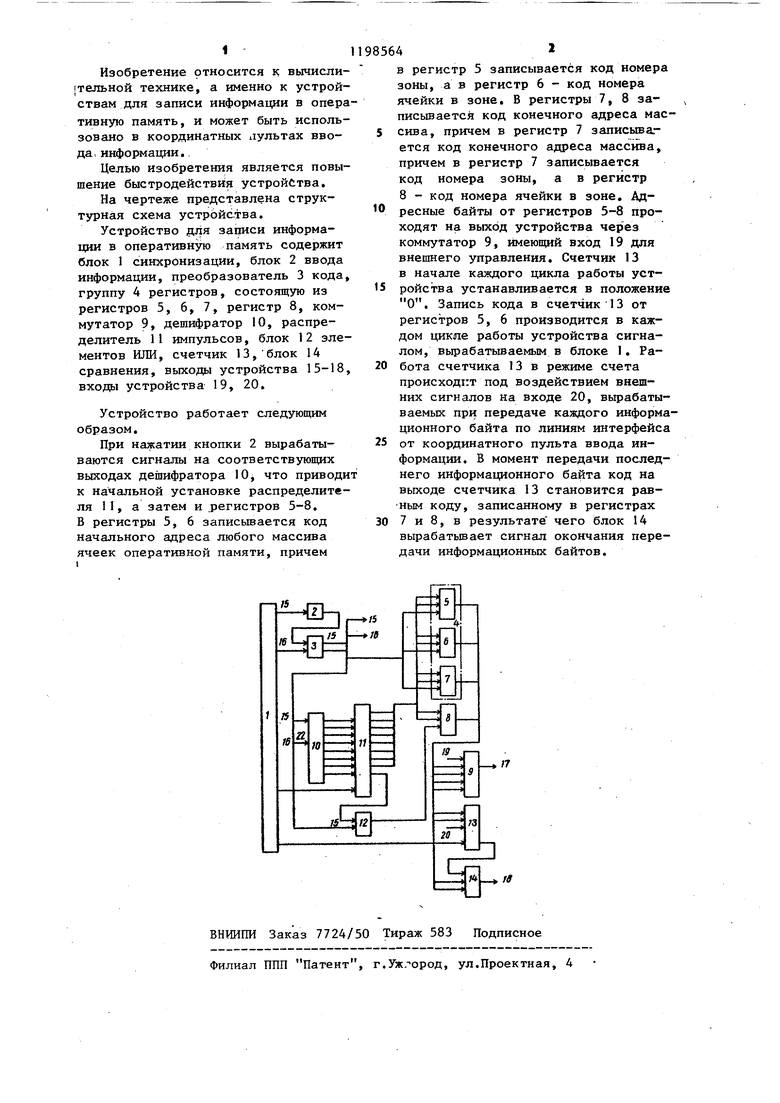

На чертеже представлена структурная схема устройства.

Устройство для зациси информации в оперативную память содержит блок 1 синхронизации, блок 2 ввода информации, преобразователь 3 кода, группу 4 регистров, состоящую из регистров 5, 6, 7, регистр 8, коммутатор 9, дешифратор 10, распределитель 1I импульсов, блок 12 элементов ИЛИ, счетчик 13,блок 14 сравнения, выходы устройства 15-18, входы устройства 19, 20.

Устройство работает следующим образом.

При нажатии кнопки 2 вырабатываются сигналы на соответствующих выходах дешифратора 10, что приводи к начальной установке распределителя 11, а затем и регистров 5-8. В регистры 5, 6 записьшается код начального адреса любого массива ячеек оперативной памяти, причем

8564

в регистр 5 записывается код номера зоны, а в регистр 6 - код номера ячейки в зоне. В регистры 7, 8 записывается код конечного адреса массива, причем в регистр 7 записывается код конечного адреса массива, причем в регистр 7 записывается код номера зоны, а в регистр 8 - код номера ячейки в зоне. Адресные байты от регистров 5-8 проходят на выход устройства через коммутатор 9, имеющий вход 19 для внешнего управления. Счетчик 13 в начале каждого цикла работы устройства устанавливается в положение О. Запись кода в счетчик 13 от регистров 5, 6 производится в каждом цикле работы устройства сигналом, вырабатьшаемым в блоке 1. Работа счетчика 13 в режиме счета происходит под воздействием внешних сигналов на входе 20, вырабатываемых при передаче каждого информационного байта по линиям интерфейса от координатного пульта ввода информации. В момент передачи последнего информационного байта код на выходе счетчика 13 становится равным коду, записанному в регистрах 7 и 8, в результате чего блок 14 вырабатьшает сигнал окончания передачи информационных байтов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1979 |

|

SU798913A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1049966A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство управления каналами | 1977 |

|

SU732870A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И КОНТРОЛЯ ИНФОРМАЦИИ - | 1979 |

|

SU826375A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИН«1)ОР14АЦИЧ В ОПЕРАТИВНУТа ПАМЯТЬ, содержащее блок синхронизации, выходы первой и второй групп которого соединены соответственно с вхо.дами блока ввода информации,входами преобразователя кода,выходы которого являются выходами устройства, группу регистров, входы первой группы которых соединены с соответствующими выходами преобразователя кода, выход блока ввода информации соединен с соответствующим входом преобразователя кода, регистр, выходы группы регистров и регистра подключены к входам коммутатора, управляющий вход которого является первым управляющим входом устройства, а выход - соответствующим выходом устройства, о т л и ч а- ю щ е е с я тем, что, с целью повьппения быстродействия, оно содержит дешифратор, распределитель импульсов, блок элементов ИЛИ, счетчик и блок сравнения, одни входы которого соединены с входами счетчика и входами коммутатора, выход блока сравнения является соответствующим выходом устройства, а другие входы сс.единены с выходами счетчика, первый управляющий вход которого является вторым управляющим входом устройства, а второй вход соединен с соответствующим выходом блока синхронизации, один из выходов ,оторого соединен с управ(Л ляющим входом распределителя импульсов , выход которого соединен с входом блока злементов ИЛИ, входы группы которого соединены с входами дешифратора и соответствующими выходами преобразователя кода, выходы дешифратора соединены с входами группы распределителя имсо пульсов , выходы группы которого 00 соединены с соответствующими входаел ми регистров группы и регистра, выа ходы блока элементов ИЛИ соединены . 4 с соответствующими входами регистра.

| Устройство для записи информации в оперативную память | 1974 |

|

SU482805A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для записи информации в оперативную память | 1975 |

|

SU516097A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-12-15—Публикация

1983-02-08—Подача