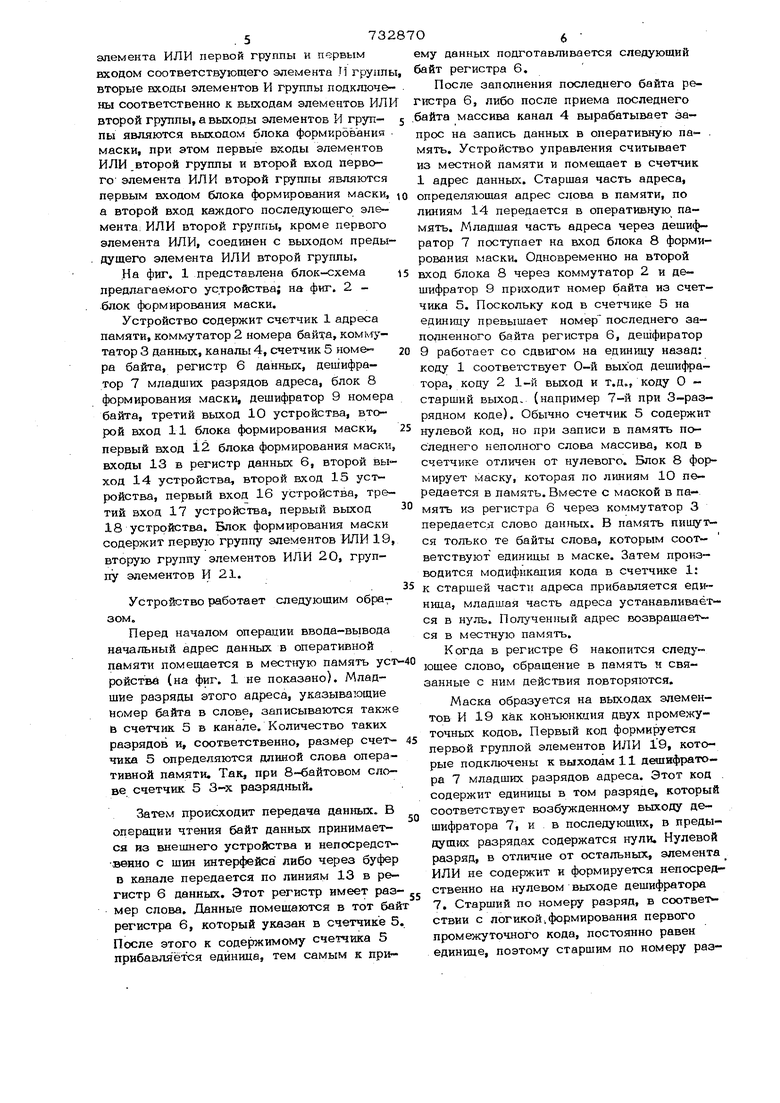

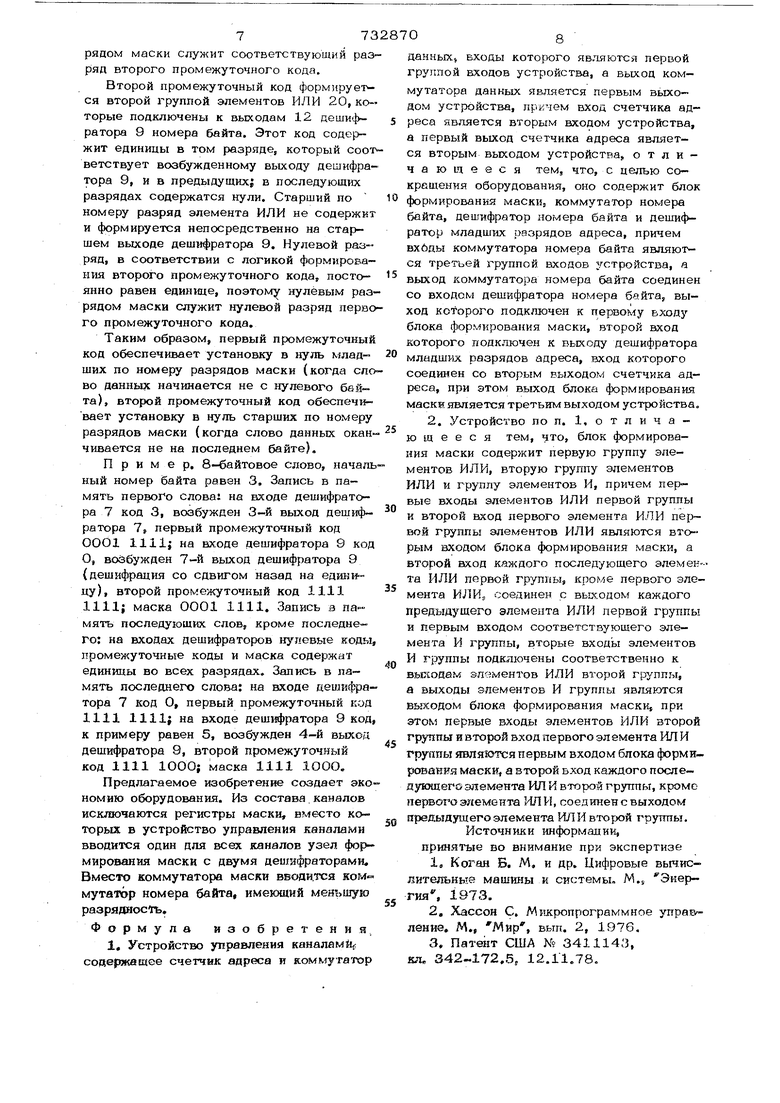

Изобретение относится к вычкспитепь- ной технике, а именно к устройствам состоящим из некоторого числа селекторных каналов и устройства управления, обслуживающего в режиме разделения времени все. каналы, каналы могут быть автономные, либо встроенные. При встроенных каналах роль устройства управления обычно выполняет процес сор. Если каналы йвтономные, функции устройства управления сводятся к коммутации соединений между каналами и оперативной памятью . Канал осуществляет обмен данными с внешними устройствами (ВУ). Передача данных между ВУ и каналом выполняется параллельными кодами, которые далее называются байтами и содержат в типичном случае 8 двоичных разрядов. В операции чтения канал принимает данные из ВУ и из полученных байтов формирует единицу информации, пригодную для записи в оперативную память (ОП) и называемую да- Лее словом. Размер слова определяется разрядность ю ОП и обычно составлят 2 и 4 либо 8 байтов. После сформирования каждого очередного слова канал передает его через устройство управления в ОП| для записи. Адрес СП хранится и модифицируется в канале либо в устройстве управления. Слово данных, передаваемое в ОП, обычно сопровождается маской. Маска управляет записью в ОП каждого байта слова. Разрядность маски равна числу байтов в слове, и каждый разряд маски соответствует одному байту слова: О-й разряд - О-му байту, 1-й разряд 1-му байту и т.д. Если разряд маски содержит единицу, соответствующий байт слова данных записывается в ОП, если нуль - не записывается и в ОП сохраняется прежний байт. В частности, если маска содержит единицы во всех разрядах, в ОП пишется полное слово. Чаще всего запись в ОП производится полными словами, но если границы массива данных не совпадают с границами слов в ОГ1, первое и .последнее слова массива не полные. Известно устройство, содержащее регистр, соединенный по входу и выходу с регистрами данных в каналах и с операти ной Памятью, Формирование слова выполняется микропрограммно. Слово, содержа щее два байта, считывается из ОП в регистр, где один т:.бо оба байта заменяют ся информацией из регистра данных кана- ла, затем слово возвращается в ОП 21, Р-1едостаток устройства затрата машинного времени на формирование слова. Наиболее близким к предлагаемому яв ляется устройство содержащее коммутатор адреса и коммутатор данных, входы которых соединены соответственно со счетчиками адреса и регистрами данных в каналах, а выходы подключены к опера тивной памяти 3. Устройство работает следующим образом. Перед началом операции ввода-вывода в счетчик помещается начальный адрес данных. Младшие разряды этого адреса, указывающие номер байта в слове, также записываются в счетчик. Количество таких разрядов и соответ ственно размер счетчика определяются длиной слова оперативной памяти. Так, при 8-байтовом слове счетчик 3-х разрядный. Затем происходит передача данных, В операции чтения байт данных принимается из внешнего устройства и непосредственно с шин интерфейса либо через буфер в канале передается, по линиям в регистр данных. Этот, регистр имеет размер слов Данные помещаются в тот байт регистра, который указан возбужденным вькодом дешифратора номера байта. Одновременно записывается единица в соответствующий разряд регистра маски. После этого к содержимому счетчика прибавляется един ца, тем самым к приему данных подготавливается следующий байт регистра. Первый байт массива данных, в зависимости от начального значения номера байта, может попасть, в начальный или любой другой байт слова, В последнем случае один или несколько левых {младших по номеру) разрядов маски, соответствующей этому слову, содержит нули. После заполнения последнего байта ре гистра канал вырабатывает запрос на запись данных Б оперативную память. Через коммутатор из счетчика в память передается адрес данных, затем через ком мутаторы - соответственно маска и данные. В память пишутся только те байты, которым соответствуют единицы в маске. После записи слова в память очищается регистр и увеличивается адрес: к содержимому счетчика прибавляется число, равное длине слова в байтах. Затем в регистре, начиная с нулевого байта, формируется очередное слово. Обращение к памяти и связанныэ с ним действия повторяются после накопления в регистре каждого очередного слова. Если массив оканчивается не на границе слова, последнее слово не полное и соответствующая этому слову маска содержит нули в одном либо нескольких правых (старших по номеру) разрядах. Недостатком известного устройства яв- пяется расход оборудования, связанный с наличием в каждом канале регистра маски. Цель изобретения - сокращение оборудования за счет экономичного построения узла формирования маски. Поставленная цель достигается тем, что в устройство, содержащее счетчик адреса и коммутатор данныХ|входы которого являются первыми входами устройства, выход коммутатора данных, является первым выходом устройства,- вход счетчика адреса является вторым входом устройства, а Первый вькод счетчика адреса - вторым выходом устройства, введены блок формирования маски, коммутатор номера байта, дешифратор номера байта и дешифратор младшиХ разрядов адреса, причем входы коммутатора номера байта являются третьей группой входов устройства, а выход коммутатора номера байта соединен со входом дешифратора номера байта, выход которого подключен к первому входу блока формирования маски, второй вход которого подключен к вьосоду дешифратора младших разрядов адреса, вход которого соединен со вторым выходом счетчика адреса, при этом выход блока формирования маски является третьим в.ыходом устройства, EinoK формирования маски содержит первую группу элементов ИЛИ, вторую группу элементов ИЛИ и группу элементов И, пркчем первые входы эле.ментов ИЛИ первой группы и второй вход перво-го элемента ИЛЙ первой группы элементов ИЛИ являются вторым входом блока формирования маски, а второй вход каждо го последующего элемента ИЛИ первой группы, кроме первого элемента ИЛИ, соединен с выходом каждого предыдущего 573 элемента ИЛИ первой группы и первым яходом соответствующего элемента II групп вторые входы элементов И группы подкгаоче ны соответственно к выходам элементов ИЛ второй группы, а выходы элементов И группы являются выходом блока формирования маски, при этом первые входы элементов ИЛИ второй группы и второй вход первого элемента ИЛИ второй группы являются первым входом блока формирования маски, а второй вход каждого последующего элемента: ИЛИ второй группы, кроме первого элемента ИЛИ, соединен с выходом предыдущего элемента ИЛИ второй груплы, .На фиг, 1 представлена блок-схема предлагаемого устройства на фиг. 2 блок формирования маски. Устройство содержит счетчик 1 адреса памяти, коммутатор 2 номера байта, KOMi iyтатор 3 данных, каналы 4, счетчик 5 номе ра байта, регистр 6 данных, дешифратор 7 младших разрядов адреса, блок 8 формирования маски, дешифратор 9 номера байта, третий выход 10 устройства, второй вход 11 блока формирования маски, первый вход 12 блока формирования маски входы 13 в регистр данных 6, второй вЫ ход 14 устройства, второй вход 15 уст ройства, первый вход 16 устройства, третий вход 17 устройства, первый выход 18 устройства. Блок формирования маски содержит первую группу элементов ИЛИ 19, вторую группу элементов ИЛИ 20, группу элементов И 21, Устройство работает следующим образом. Перед началом операции ввода-вывода начальный адрес данных в оперативной в местную память ус1 памяти помещается ройства (на фиг. 1 не показано). Младщие разряды этого адреса, указывающие номер байта в слове, записываются также в счетчик 5 в канале. Количество таких разрядов и, соответственно, размер счетчика 5 определяются длиной слова оперативной памяти. Так, при 8-байтовом слове счетчик 5 3-х разрядный. Затем происходит передача данных, В операции чтения байт данных принимается из внешнего устройства и непосредс венно с шин интерфейса либо через буфер в канале передается по линиям 13 в регистр 6 данных. Этот регистр имеет раз мер слова. Данные помещаются в тот бай регистра 6, который указан в счетчике 5 После этого к содержимому счетчика 5 прибавляётся единица, тем самым к при- О ему данных подготавливается следующий байт регистра 6. После заполнения последнего байта реистра 6, либо после приема последнего байта массива канал 4 вырабатывает запрос на запись данных в оперативную па- , мять. Устройство управления считывает из местной памяти и пометает в счетчик 1 адрес данньгх. Старшая часть адреса, определяющая адрес слова в памяти, по линиям 14 передается в оперативную память. Младшая часть адреса через дешифратор 7 поступает на вход блока 8 формирования маски. Одновременно на второй вход блока 8 через коммутатор 2 и дешифратор 9 приходит номер байта из счетчика 5, Поскольку код в счетчике 5 на единицу превышает номер последнего заполненного байта регистра 6, дешфиратор 9 работает со сдвигом на единицу назад: коду 1 соотве1х;твует 0-й выход дешифратора, коду 2 1-й выход и т.д., коду О старший ВЫХОД- (например 7-й при 3-разрядном коде). Обычно счетчик 5 содержит нулевой код, но при записи в память последнего неполного слова массива, код в счетчике отличен от нулевого. Блок 8 формирует маску, которая по линиям 10 передается в память. Вместе с маокой в память из регистра 6 через коммутатор 3 передается слово данных. В память пишутся Только те байты слова, которым coot ветствуют единицы в маске. Затем производится модификация кода в счетчике 1: к старшей части адреса прибавляется единица, младшая часть адреса устанавливаёГся в нуль. Полученный адрес возвращает- ся в местную память. Когда в регистре 6 накопится следу обращение в память м связанные с ним действия повторяются, .Маска образуется на выходах элементов И 19 как конъюнкция двух промежуточных кодов. Первый код формируется первой группой элементов ИЛИ 19, которые подключены к выходам 11 дешифратора 7 младших разрядов адреса. Этот код содержит единицы в том разряде, который соответствует возбужденнсыу выходу дешифратора 7, и в последующих, в предыдущих разрядах содержатся нули. Нулевой разряд, в отличие от остальных, элемента ИЛИ не содержит и формируется непосредственно на нулевом выходе дешифратора 7. Старший по номеру разряд, в соответствии с логикойiформирования первого промежуточного кода, постоянно равен единице, поэтому старшим по номеру раз773рядом маски служит соответствующий разряд второго промежуточного кода. Второй промежуточный код формируется второй группой элементов ИЛИ 20, которые подключены к выходам 12 дешИфратора 9 номера байта. Этот код содержит единицы в том разряде, который соот ветствует возбужденному выходу дешифратора 9, и в предыдущих; в последующих разрядах содержатся нули. Старший по номеру разряд элемента ИЛИ не содержит и формируется непосредственно на старшем выходе дешифратора 9, Нулевой разряд, в соответствии с логикой формирования второго промежуточного кода, постоянно равен единице, поэтому нулевым разрядом маски служит нулевой разряд перво го промежуточного кода. Таким образом, первый промежуточный код обеспечивает установку в нуль млад- щих по номеру разрядов маски (когда слово данных начинается не с нулевого байта), второй промежуточный код обеспечивает установку в нуль старших по номеру разрядов маски (когда слово данных оканчивается не на последнем байте). Пример, 8-байтовое слово, началЬ ный номер байта равен 3. Запись в память первого слова: на входе дешифратора 7 код 3, возбужден 3-й выход дешифратора 7, первый промежуточный код OOOl 1111| на входе дешифратора 9 код О, возбужден 7-й выход дешифратора 9 (дешифрация со сдвигом назад на единицу), второй промежуточный код 11131111; маска ОО01 1111. Запись в память последующих слов, кроме последнего: на входах дешифраторов нулевые коды, промежуточные коды и маска содержат единицы во всех разрядах. Запись в память последнего слова: на входе цешифратора 7 код О, первый промежуточный код 1111 1111; на входе дешифратора 9 код, к примеру равен 5, возбужден 4-й вьосод дешифратора 9, второй промежуточный код 1111 1ООО; маска 1111 1ООО. Прюдлагаемое изобретение создает экономию оборудования. Из состава,каналов исключаются регистры маски, вместо которых в устройство управления каналами вводится один для всех каналов узел формирования маски с двумя дешифраторами. Вместо коммутатора маски вводи.тся коммутатор номера байта, имеющий меньшую разрядное ib. Формула изобретения 1, Устройство управления каналам содержащее счетчик адреса и коммутатор 0 данных, входы которого являются первой группой входов устройства, а выход коммутатора данных является первым выходом устройства, причем вход счетчика ад- реса является вторым входом устройства, а первый выход счетчика адреса является вторым выходом устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит блок формирования маски коммутатор номера байта, дешифратор номера байта и дешифратор младших разрядов адреса, причем вхбды коммутатора номера байта являются третьей группой входов устройства, а выход коммутатора номера байта соединен со входом дешифратора номера байта, выход которого подключен к первому входу блока формирования маски, второй вход которого подключен к выходу дешифратора младших разрядов адреса, вход которого соединен со вторым выходом счетчика адреса, при этом выход блока формирования маски является третьим выходом устройства, 2. Устройство по п. 1, о т л и ч а JQ щ g g 3 g то, блок формирова„j,g маски содержит первую группу элементов ИЛИ, вторую группу элементов ИЛИ и группу элементов И, причем первые входы элементов ИЛИ первой группы и второй вход первого элемента ИЛИ nei вой группы элементов ИЛИ являются втоРЫМ входом блока формирования маски, а второй ВХ.ОЦ каждого последующего элемек-та ИЛИ первой группы, кроме первого элемента ИЛИ. соединен с выходом каждого предыдущего элемента ИЛИ первой группы и первым входом соответствующего элемента И группы, вторые входы элементов И группы подключены соответственно к вькодам элементов ИЛИ второй группы, а выходы элементов И группы являются вьгходом блока формирования маски, при этом первые входы элементов ИЛИ второй группы и второй вход первого элемента ИЛ И группы являются первым входом блока формирювання маски, а второй вход каждого последующего элемента ИЛ И второй группы, кроме первого элемента ИЛИ, соединен с выходом предыдущего элемента ИЛ И второй группы Источники информадии, принятые во внимание при экспертизе 1, Коган Б. М, и др. Цифровые вычислительные машины и системы. M.s Энергия, 1973. 2,Хассон С. М{ кропрограммное управление М., Мир, вып. 2, 1976. 3.Патент США 3411143, кл. 342-172,5, 12.11.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

Авторы

Даты

1980-05-05—Публикация

1977-11-14—Подача