Изобретение относится к вычисли-, тельной технике и может быть использовано для передачи информации от медленно действующих устройств к быстродействующей ЭВМ.

Цель изобретения - повьшгение пропускной способности устройства.

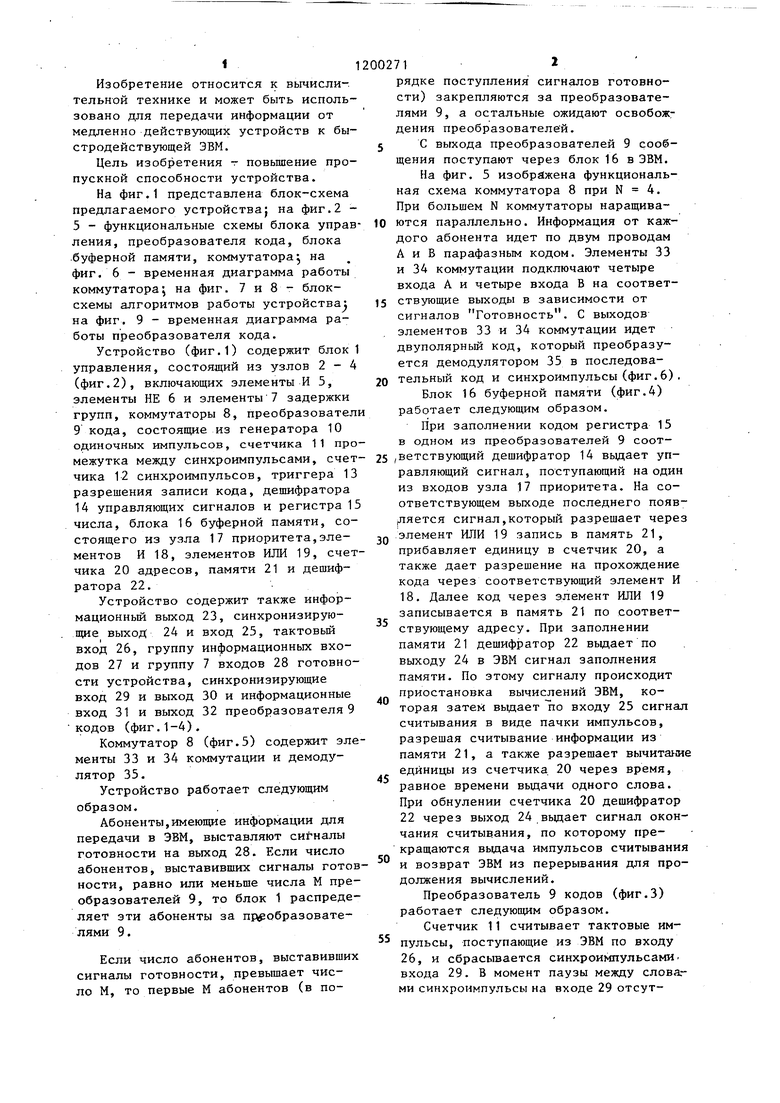

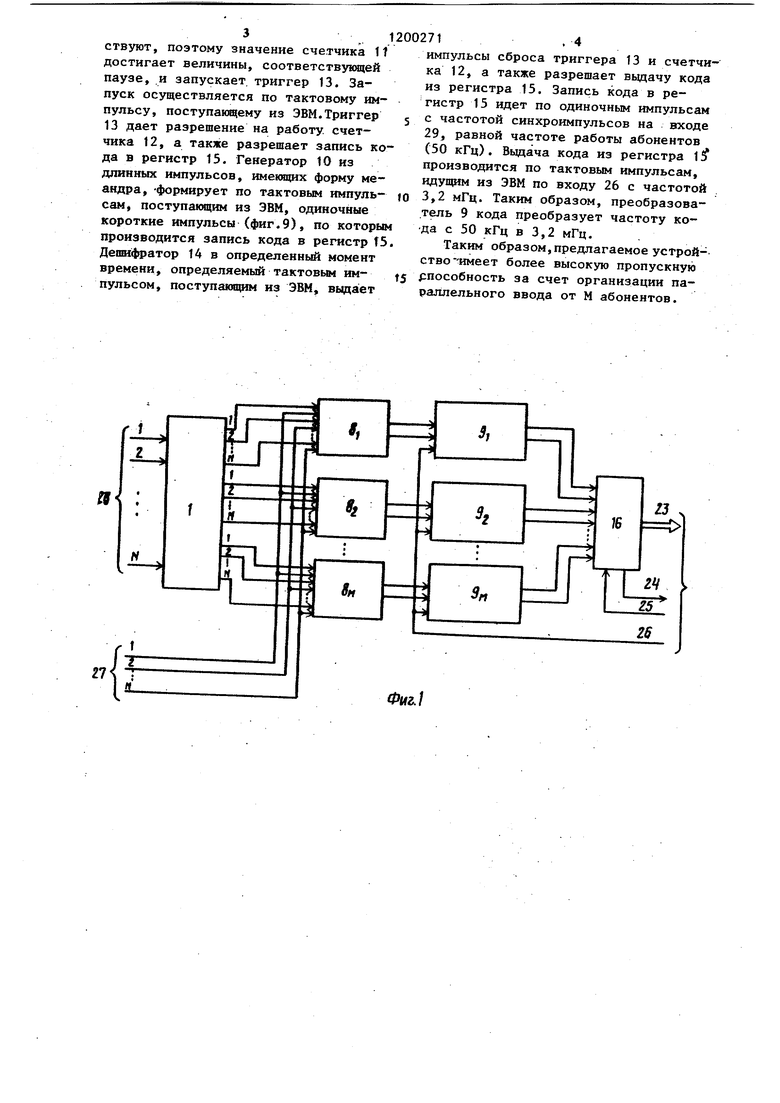

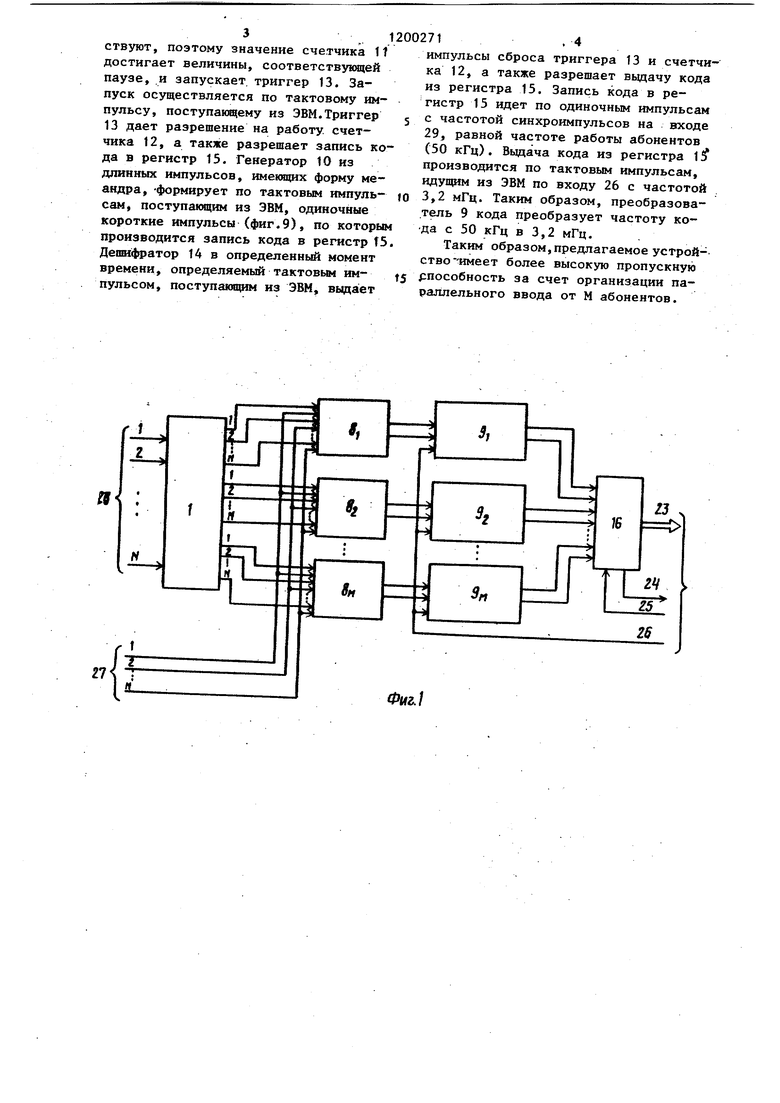

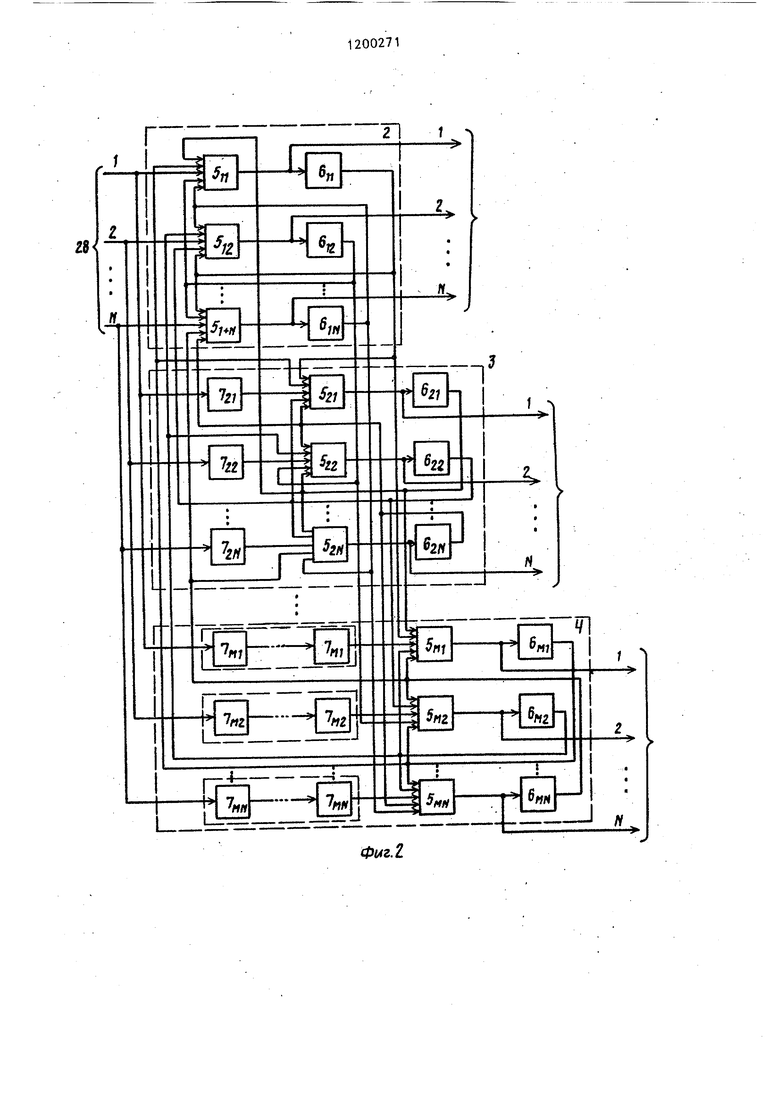

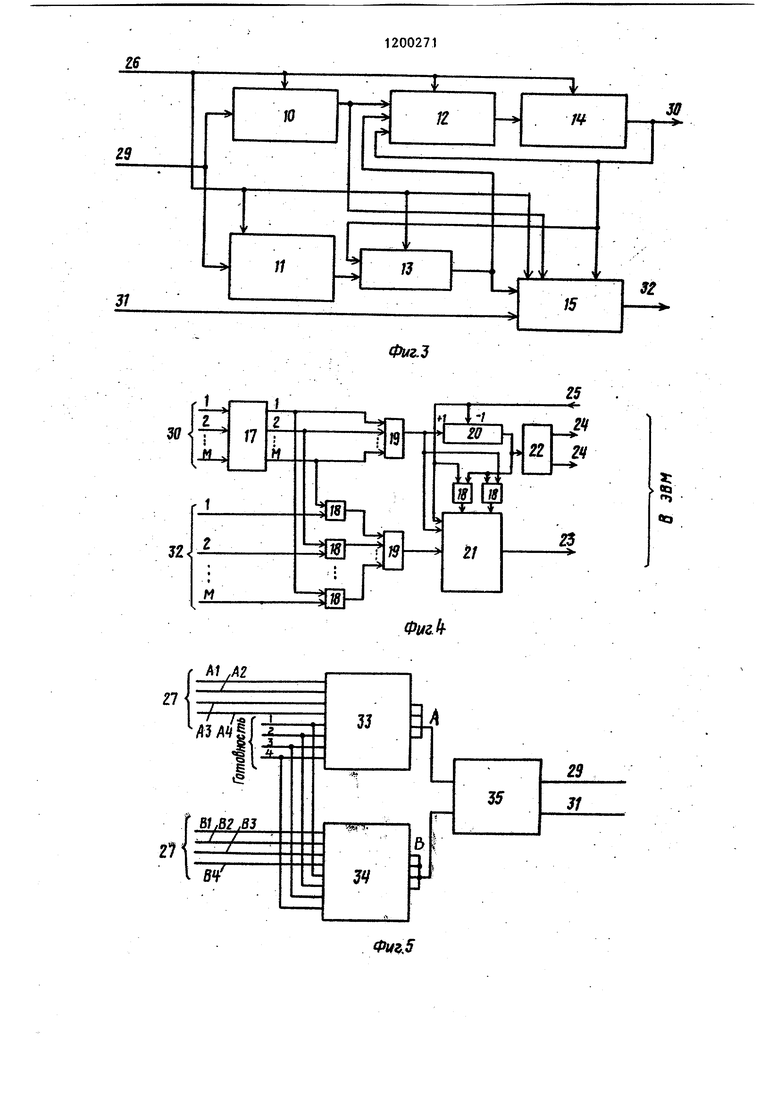

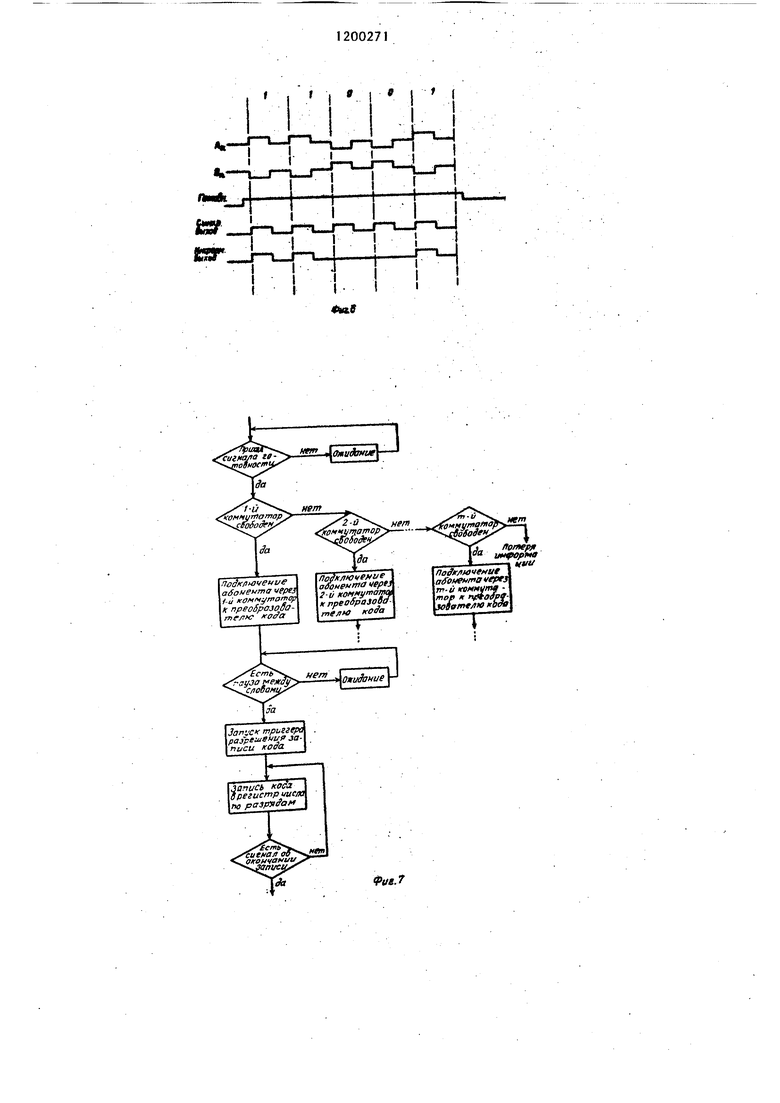

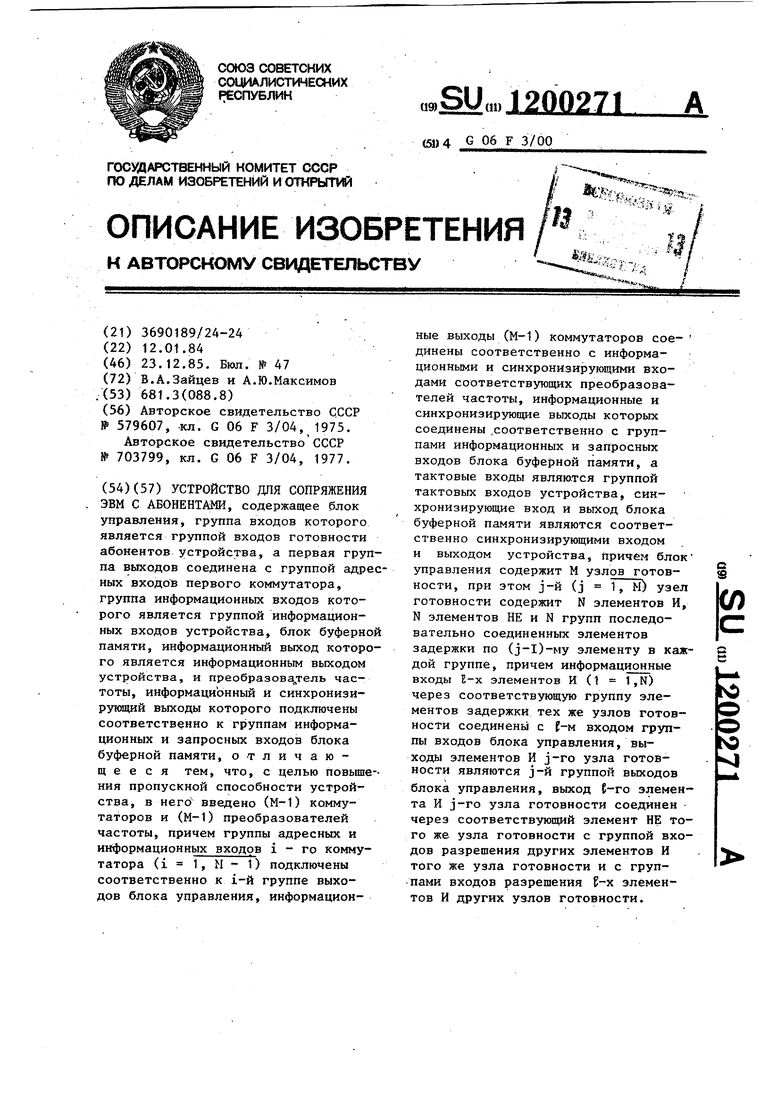

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 5 - функциональные схемы блока управления, преобразователя кода, блока буферной памяти, коммутатораj на фиг. 6 - временная диаграмма работы коммутатораJ на фиг. 7 и 8 - блоксхемы алгоритмов работы устройства: на фиг. 9 - временная диаграмма работы преобразователя кода.

Устройство (фиг.1) содержит блок 1 управления, состоящий из узлов 2-4 (фиг.2), включающих элементы И 5, элементы НЕ 6 и элементы 7 задержки групп, коммутаторы 8, преобразователи 9 кода, состоящие из генератора 10 одиночных импульсов, счетчика 11 промежутка между синхроимпульсами, счетчика 12 синхроимпульсов, триггера 13 разрешения записи кода, дешифратора 14 управляющих сигналов и регистра 15 числа, блока 16 буферной памяти, состоящего из узла 17 приоритета,элементов И 18, элементов ИЛИ 19, счетчика 20 адресов, памяти 21 и дешифратора 22.

Устройство содержит также информационный выход 23, синхронизирующие выход 24 и вход 25, тактовый вход 26, группу информационных входов 27 и группу 7 входов 28 готовности устройства, синхронизирующие вход 29 и выход 30 и информационные вход 31 и выход 32 преобразователя 9 кодов (фиг.1-4).

Коммутатор 8 (фиг.5) содержит элементы 33 и 34 коммутации и демодулятор 35.

Устройство работает следующим образом.

Абоненты,имеющие информации для передачи в ЭВМ, выставляют сигналы готовности на выход 28. Если число абонентов, выставивших сигналы готовности, равно или меньше числа М преобразователей 9, то блок 1 распределяет эти абоненты за пр образователями 9.

Если число абонентов, выставивших сигналы готовности, превышает число М, то первые М абонентов (в порядке поступления сигналов готовности) закрепляются за преобразователями 9, а остальные ожидают освобождения преобразователей.

С выхода преобразователей 9 сообщения поступают через блок 16 в ЭВМ.

На фиг. 5 изображена функциональная схема коммутатора 8 при N 4. При большем N коммутаторы наращиваются параллельно. Информация от каждого абонента идет по двум проводам А и В парафазньм кодом. Элементы 33 и 34 коммутации подключают четыре входа А и четыре входа В на соответствующие выходы в зависимости от сигналов Готовность. С выходов элементов 33 и 34 коммутации идет двуполярньй код, который преобразуется демодулятором 35 в последовательный код и синхроимпульсы (фиг.6) .

Блок 16 буферной памяти (фиг.4) работает следующим образом.

При заполнении кодом регистра 15 в одном из преобразователей 9 соот5 (Ветствующий дешифратор 14 выдает управляющий сигнал, поступающий на один из входов узла 17 приоритета. На соответствующем выходе последнего появдяется сигнал,который разрешает через

Q элемент ИЛИ 19 запись в память 21, прибавляет единицу в счетчик 20, а также дает разрешение на прохождение кода через соответствующий элемент И 18. Далее код через элемент ИЛИ 19 записывается в память 21 по соответствующему адресу. При заполнении памяти 21 дешифратор 22 выдает по выходу 24 в ЭВМ сигнал заполнения памяти. По этому сигналу происходит приостановка вычислений ЭВМ, которая затем выдает по входу 25 сигнал считывания в виде пачки импульсов, разрешая считывание информации из памяти 21, а также разрешает вычитание единицы из счетчика. 20 через время, равное времени вьщачи одного слова. При обнулении счетчика 20 дешифратор 22 через выход 24 вьщает сигнал окончания считывания, по которому прекращаются выдача импульсов считывания и возврат ЭВМ из перерывания для продолжения вычислений.

Преобразователь 9 кодов (фиг.З) работает следующим образом.

Счетчик 11 считывает тактовые импульсы, поступающие из ЭВМ по входу 26, и сбрасывается синхроимпульсами. входа 29. В момент паузы между словами синхроимпульсы на входе 29 отсутствуют, поэтому значение счетчика It достигает величины, соответствз мцей паузе, ,и запускает, триггер 13. Запуск осуществляется по тактовому импульсу, поступающему из ЭВМ.Триггер 13 дает разрешение на работу счетчика 12, а также разрешает запись кода в регистр 15. Генератор 10 из длинных импульсов, имекнцих форму меандра, -формирует по тактовым импульсам, поступакяцим из ЭВМ, одиночные короткие импульсы (фиг.9), по которым производится запись кода в регистр Т5. Дешифратор 14 в определенный момент времени, определяемый тактовым импульсом, поступакицим из ЭВМ, вьщает

импульсы сброса триггера 13 и счетчика 12, а также разрешает выдачу кода из регистра 15. Запись кода в регистр 15 идет по одиночным импульсам с частотой синхроимпульсов на входе 29, равной частоте работы абонентов (50 кГц). Вьздача кода из регистра 15 производится по тактовым импульсам, идущим из ЭВМ по входу 26 с частотой 3,2 мГц. Таким образом, преобразователь 9 кода преобразует частоту кода с 50 кГц в 3,2 мГц.

Таким образом,предлагаемое устройство-имеет более высокую пропускную рпособность за счет организации параллельного ввода от М абонентов.

Фмг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство сопряжения | 1981 |

|

SU993240A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С АБОНЕНТАМИ, содержащее блок управления, группа входов которого является группой входов готовности абонентов устройства, а первая группа ВЫХОДОВ соединена с группой адресных ВХОДОВ первого коммутатора, группа информационных входов которого является группой информационных ВХОДОВ устройства, блок буферной памяти, информационный выход которого является информационным выходом устройства, и преобразова тель частоты, информационный и синхронизирунлций ВЫХОДЫ которого подключены соответственно к группам информационных и запросных ВХОДОВ блока буферной памяти, отличающееся тем, что, с целью повыше-ния пропускной способности устройства, в Herd введено (М-1) коммутаторов и (М-1) преобразователей частоты, причем группы адресных и информационных входов i - го коммутатора (i 1, Н - 1) подключены соответственно к i-й группе выходов блока управления, информационные ВЫХОДЫ (М-1) коммутаторов соединены соответственно с информационными и синхронизирующими входами соответствующих преобразователей частоты, информационные и синхронизирующие выходы которых соединены ,соответственно с группами информационных и запросных ВХОДОВ блока буферной памяти, а тактовые входы являются группой тактовых ВХОДОВ устройства, синхронизирующие ВХОД и ВЫХОД блока буферной памяти являются соответственно синхронизирующими ВХОДОМ и ВЫХОДОМ устройства, причем блок о € управления содержит М узлов готовности, при этом j-й (J 1, М) узел (Л готовности содержит N элементов И, N элементов НЕ и N групп последовательно соединенных элементов задержки по (j-l)-My элементу в каждой группе, причем информационные ВХОДЫ Е-х элементов И

v|

Фиг. IfФиъ,5

fc

сигнал ff ffAwf jafjucufo

фувозо npeof pasoffome

ffa

Ожидание

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1975 |

|

SU579607A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1977 |

|

SU703799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1984-01-12—Подача