соединены с вторыми входами соответствующих элементов блоков элементов 2И, третий выход блока управления соединен с вторым входом блока триггера команд, соответствующие выходы блока контроля соединены с соответствующими входами дешифратора, первая тактовая шина соединена с вторым входом блока контроля и вторым входом блока управления, вторая тактовая шина соединена с нулевым входом блока коммутации, объединенными первьп и входами блока элементов ЗИ-Ш1И, объединенными вторыми входами блока элементов 4И и третьим входом блока управления, шина Готовность соединена с нулевым входом блока управления, причем с первого По четвертый выходы блока управления, выходы блока элементов 4И, выход первого элемента И, выходы блоков элементов 2И соединены с соответствующими выходными шина.ми.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1242966A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

| Устройство для передачи и приема данных | 1982 |

|

SU1098104A1 |

| Многоканальное устройство для ввода информации от двухпозиционных датчиков | 1988 |

|

SU1550521A1 |

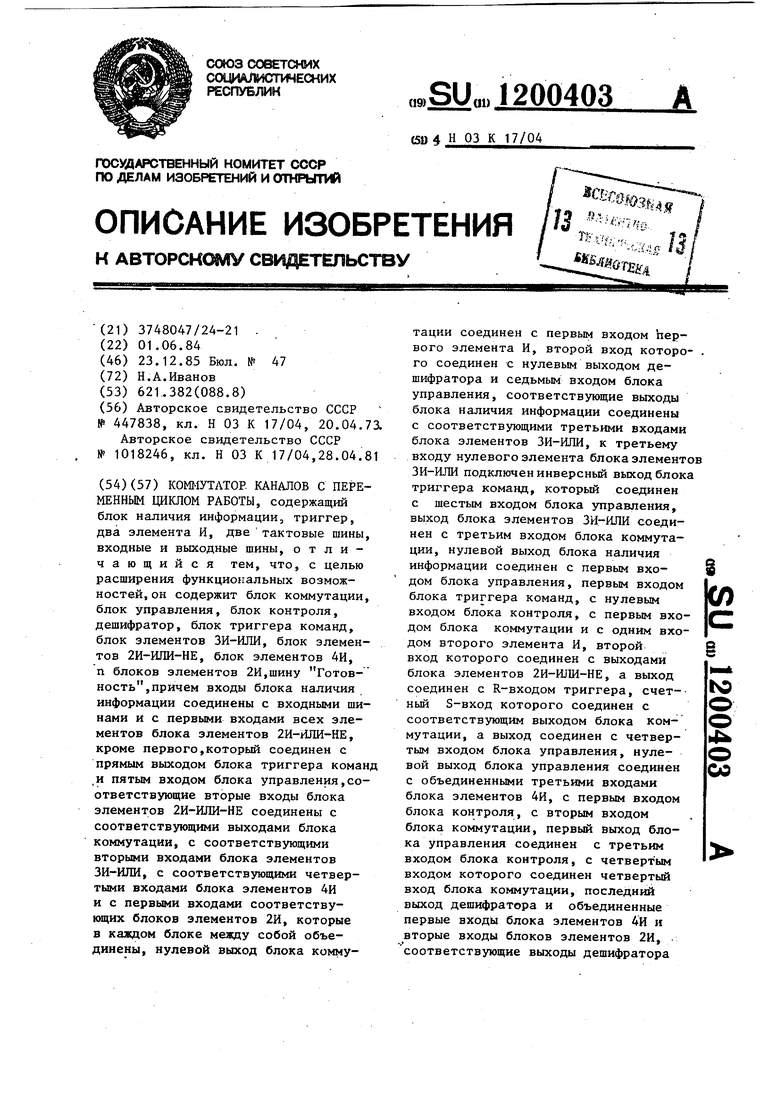

КОММУТАТОР. КАНАЛОВ С ПЕРЕМЕННЫМ ЦИКЛОМ РАБОТЫ, содержащий блок наличия информации, триггер, два элемента И, две тактовые шины, входные и выходные шины, отличающийся тем, что, с целью расширения функциональных возможностей, он содержит блок коммутации, блок управления, блок контроля, дешифратор, блок триггера команд, блок элементов ЗИ-ИЛИ, блок элементов 2И-РШИ-НЕ, блок элементов 4И, п блоков элементов 2И,шину Готовность,причем входы блока наличия информации соединены с входными шинами и с первыми входами всех элементов блока элементов 2И-ИЛИ-НЕ, кроме первого,который соединен с прямым выходом блока триггера команд ,и пятым входом блока управления,соответствующие вторые входы блока элементов 2И-ИЛИ-НЕ соединены с соответствующими выходами блока коммутации, с соответствующими вторыми входами блока элементов ЗИ-ИЛИ, с соответствующими четвертыми входами блока элементов 4И и с первыми входами соответствующих блоков элементов 2И, которые в каждом блоке между собой объединены, нулевой выход блока коммутации соединен с первым входом первого элемента И, второй вход которо- . го соединен с нулевым выходом дешифратора и седьмым входом блока управления, соответствующие выходы блока наличия информации соединены с соответствующими третьими входами блока элементов ЗИ-ИЛИ, к третьему входу нулевого элемента блока элементов ЗИ-ИЛИ подключен инверсный вькод блока триггера команд, который соединен с шестым входом блока управления, выход блока элементов ЗИ-ИЛИ соединен с третьим входом блока коммутации, нулевой выход блока наличия g информации соединен с первым входом блока управления, первым входом блока триггера команд, с нулевым входом блока контроля, с первым входом блока коммутации и с одним входом второго элемента И, второй вход которого соединен с выходами блока элементов 2И-Ш1И-НЕ, а выход 1Ю соединен с R-входом триггера, счет-о ный S-вход которого соединен с о соответствующим выходом блока ком4: мутации, а выход соединен с четверО СО тым входом блока управления, нулевой выход блока управления соединен с объединенными третьими входами блока элементов 4И, с первым входом блока контроля, с вторым входом блока коммутации, первый выход блока управления соединен с третьим входом блока контроля, с четвертым входом которого соединен четвертый вход блока коммутации, последний выход дешифратора и объединенные первые входы блока элементов 4И и вторые входы блоков элементов 2И, соответствующие выходы дешифратора

Изобретение относится к импульсно технике, в частности к устройствам электронной коммутации цепей, и може быть использовано в системах передач информации, адаптирующихся к объ.емам и скорости передаваемой информации.

Цель изобретения - расширение функциональных возможностей за счет обеспечения коммутирования многотактной информации и автоматической подстройки частоты коммутации под частоту приемного устройства.

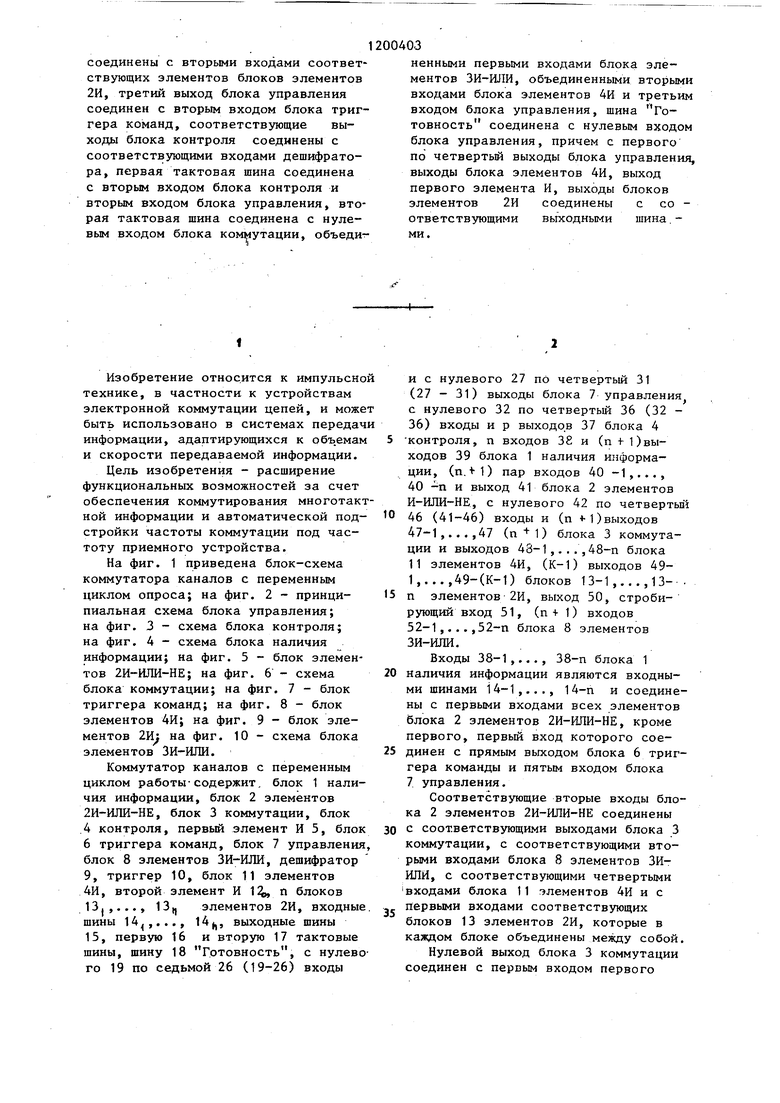

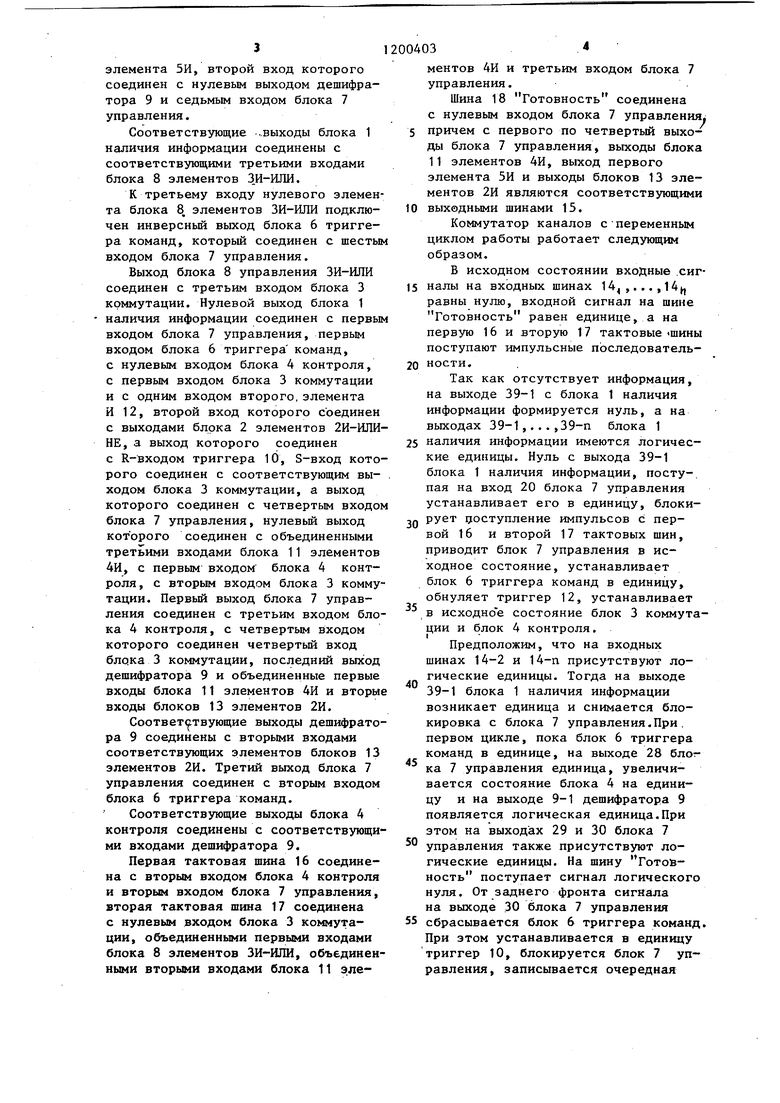

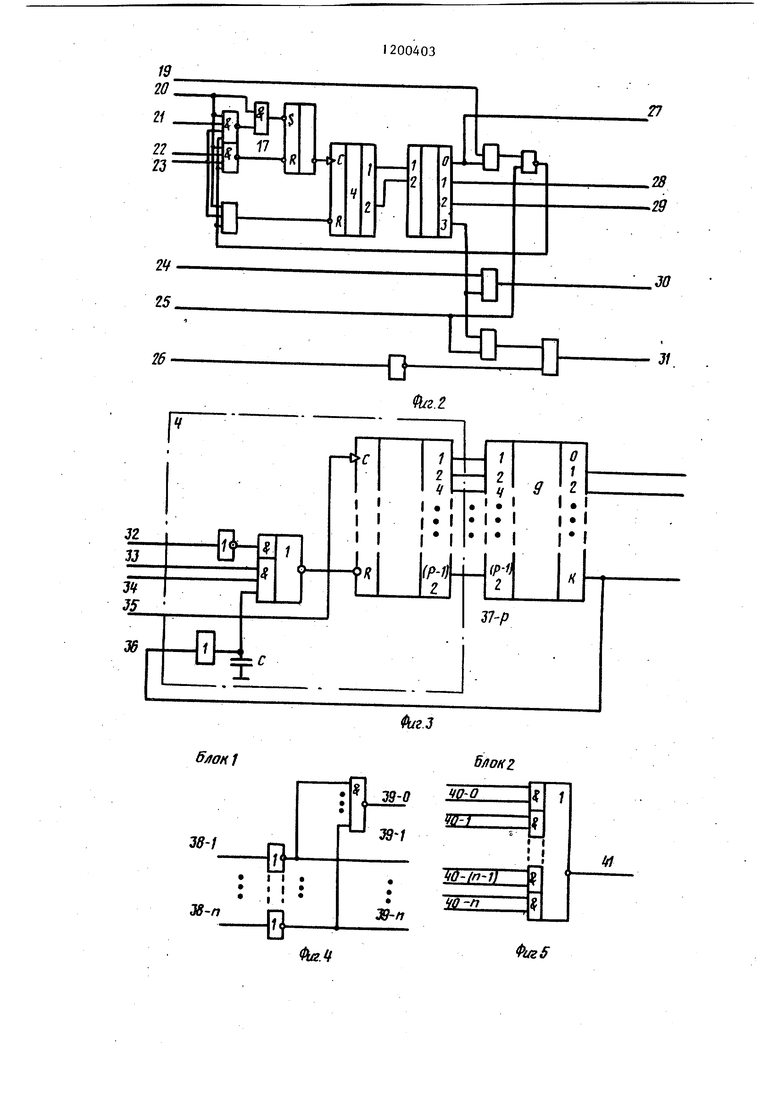

На фиг. 1 приведена блок-схема коммутатора каналов с переменным циклом опроса; на фиг. 2 - принципиальная схема блока управления; на фиг. 3 - схема блока контроля; на фиг, 4 - схема блока наличия информации; на фиг. 5 - блок элементов 2И-ИЛИ-НЕ; на фиг. 6 - схема блока коммутации; на фиг. 7 - блок триггера команд; на фиг. 8 - блок элементов 4И; на фиг. 9 - блок элементов 2И: на фиг. 10 - схема блока элементов ЗИ-ИЛИ.

Коммутатор каналов с переменным циклом работы-содержит, блок 1 наличия информации, блок 2 элементов 2И-ШШ-НЕ, блок 3 коммутации, блок 4 контроля, первый элемент И 5, блок 6 триггера команд, блок 7 управления блок 8 элементов ЗИ-ИЛИ, дешифратор 9, триггер 10, блок 11 элементов 4И, второй элемент И 1 п блоков

13м элементов 2И, входные

13

шины 14,..., 14, выходные шины 15, первую 16 и вторую 17 тактовые шины, шину 18 Готовность, с нулевого 19 по седьмой 26 (19-26) входы

и с нулевого 27 по четвертый 31 (27 - 31) выходы блока 7 управления, с нулевого 32 по четвертый 36 (32 36) входы и р выходо.в 37 блока 4

-контроля, п входов 38 и (п+1)выходов 39 блока 1 наличия информации, (п. -1) пар входов 40 -1,..., 40 и выход 41 блока 2 элементов И-ИЛИ-НЕ, с нулевого 42 по четвертьй

46 (41-46) входы и (п Овыкодов 47-1,...,47 (п t 1) блока 3 коммутации и выходов 48-1,...,48-п блока 11 элементов 4И, (К-1) выходов 491,...,49-(К-1) блоков 13-1,...,13- .

п элементов 2И, выход 50, стробирующий вход 51, ( 1) входов 52-1,...,52-п блока 8 элементов ЗИ-ИЛИ.

Входы 38-1,..., 38-п блока 1

наличия информации являются входными шинами 14-1 14-п и соединены с первыми входами всех элементов блока 2 элементов 2И-ИЛИ-НЕ, кроме первого, первьш вход которого сое-

динен с прямым выходом блока 6 триггера команды и пятым входом блока 7 управления.

Соответствующие вторые входы блока 2 элементов 2И-ИЛИ-НЕ соединены

с соответствующими выходами блока 3 коммутации, с соответствующими вторыми входами блока 8 элементов ЗИИЛИ, с соответствующими четвертыми входами блока 11 элементов 4И и с

первыми входами соответствующих блоков 13 элементов 2И, которые в каждом блоке объединены между собой. Нулевой выход блока 3 коммутации соединен с первым входом первого

3

элемента 5И, второй вход которого соединен с нулевым выходом дешифратора 9 и седьмым входом блока 7 управления.

Соответствующие ..выходы блока 1 наличия информации соединены с соответствующими третьими входами блока 8 элементов ЗИ-ШШ.

К третьему входу нулевого элемента блока 8 элементов ЗИ-ИЛИ подключен инверсньй выход блока 6 триггера команд, которьш соединен с шестым входом блока 7 управления.

Выход блока 8 управления ЗИ-ИЛИ соединен с третьим входом блока 3 коммутации. Нулевой выход блока 1 наличия информации соединен с первым входом блока 7 управления, первым входом блока 6 триггера команд, с нулевым входом блока 4 контроля, с первым входом блока 3 коммутации и с одним входом второго, элемента И 12, второй вход которого соединен с выходами блока 2 элементов 2И-ИЛИНЕ, а выход которого соединен с R-входом триггера 10, S-вход которого соединен с соответствующим выходом блока 3 коммутации, а выход которого соединен с четвертым входом блока 7 управления, нулевьй выход которого соединен с объединенными третьими входами блока 11 элементов 4И, с первым входом блока 4 контроля , с вторым входом блока 3 коммутации. Первьш выход блока 7 управления соединен с третьим входом блока 4 контроля, с четвертым входом которого соединен четвертый вход блрка 3 коммутации, последний выход дешифратора 9 и объединенные первые входы блока 11 элементов 4И и вторые входы блоков 13 элементов 2И.

Соответ твующие выходы дешифратора 9 соединены с вторыми входами соответствующих элементов блоков 13 элементов 2И. Третий выход блока 7 управления соединен с вторым входом блока 6 триггера команд.

Соответствующие выходы блока 4 контроля соединены с соответствующими входами дешифратора 9.

Первая тактовая шина 16 соединена с вторым входом блока 4 контроля и вторым входом блока 7 управления, вторая тактовая шина 17 соединена с нулевым входом блока 3 коммутации, объединенными первыми входами блока 8 элементов ЗИ-ИЛИ, объединенными вторыми входами блока 11 эле00403

ментов 4И и третьим входом блока 7 управления.

Шина 18 Готовность соединена с нулевым входом блока 7 управления

5 причем с первого по четвертый выходы блока 7 управления, выходы блока 11 элементов 4И, выход первого элемента 5И и выходы блоков 13 элементов 2И являются соответствующими

to выходными шинами 15.

Коммутатор каналов спеременньм циклом работы работает следующим образом.

В исходном состоянии входные сигналы на входных шинах 14,...,14 равны нулю, входной сигнал на шине Готовность равен единице, а на первую 16 и вторую 17 тактовые «шины поступают импульсные последовательности.

Так как отсутствует информация, на выходе 39-1 с блока 1 наличия информации формируется нуль, а на выходах 39-1,...,39-п блока 1

25 наличия информации имеются логические единицы. Нуль с выхода 39-1 блока 1 наличия информации, посту-, пая на вход 20 блока 7 управления устанавливает его в единицу, блоки, рует поступление импульсов с первой 16 и второй 17 тактовых шин, приводит блок 7 управления в исходное состояние, устанавливает блок 6 триггера команд в единицу, обнуляет триггер 12, устанавливает в исходное состояние блок 3 коммутации и блок 4 контроля.

Предположим, что на входных шинах 14-2 и 14-п присутствуют логические единицы. Тогда на выходе

40 39-1 блока 1 наличия информации возникает единица и снимается блокировка с блока 7 управления.При . первом цикле, пока блок 6 триггера команд в единице, на выходе 28 бло45ка 7 управления единица, увеличивается состояние блока 4 на единицу и на выходе 9-1 дешифратора 9 появляется логическая единица.При этом на выходах 29 и 30 блока 7

управления также присутствуют логические единицы. На шину Готовность поступает сигнал логического нуля. От заднего фронта сигна1ла на выходе 30 блока 7 управления

55 сбрасывается блок 6 триггера команд. При этом устанавливается в единицу триггер 10, блокируется блок 7 управления, записывается очередная 5 единица в блоке 4 контроля. Поэтому на выходе 47-1 блока 3 коммутации присутствует логическая единица По условию присутствия логического нуля на выходной шине 14-1 отсутствует сброс триггера 10. Поэтому по условию присутствия единицы на выходе 27 блока 7 управления подтверждается установка в единицу триггера 10 и модифицируется на единицу сос.тояние при логическом нуле на выходе 47-1 блока 3 коммутации. При это 1, но так как PD ч лvvf л, и 1, по п логических единицах на выходах 47-2 блока 3 коммутации и входной шине 14-2 устанавливается в ноль триггер 10 и блок 7 управления начинает второй цикл работы. По появлению единицы второго цикла на выходе 28 блока 7 управления уве личивается на единицу состояние бло 036 ка 4 контроля, что вызывает строб на выходе 9-1 дешифратора 9. Так как На выходе 47-2 блока коммутации единица, то строб с выхода 9-1 проходит только через блок 13-2 элементов 2И. При возникновении единицы на выходе 31 блока 7 управления снимается сигнал с шины 18 Готовность и блокируется блок 7 управления.При повторном появлении нуля на шине 18 Готовность блок 7 управления разблокируется и начинается третий цикл работы. При каждом.повторном цикле по единице на выходе 28 блока 7 управления заносится в блок 4 контроля единица и появляется соответструющий строб на выходе дешифратора 9, которым опрашивается очередной такт информации, пока не закончатся все К обращений.

kl2.tf

Фиг5

| Адаптивный коммутатор | 1973 |

|

SU447838A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Коммутатор каналов с переменным циклом работы | 1981 |

|

SU1018246A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-23—Публикация

1984-06-01—Подача