Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке универсальных систем обработки цифровой информации.

Цель изобретения - расширение функциональных возможностей путем реализации функции полусумматора.

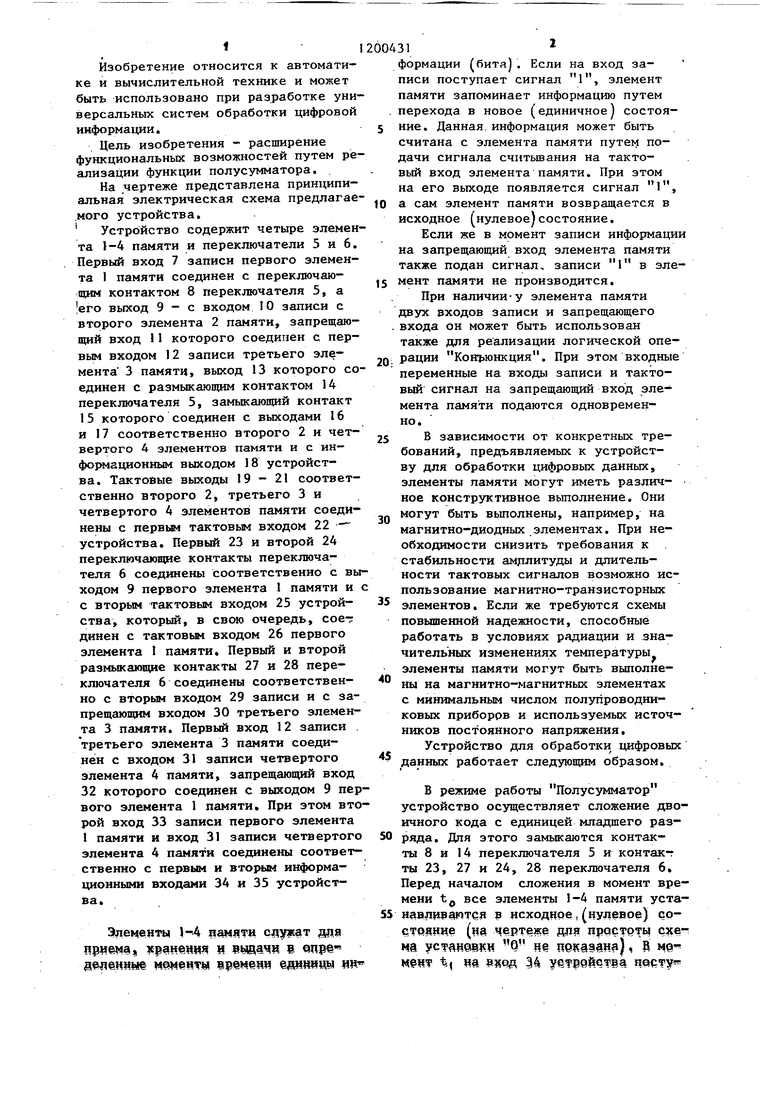

На чертеже представлена принципиальная электрическая схема предлагае.мого устройства,

Устройство содержит четыре элемента 1-4 памяти и переключатели 5 и 6. Первый вход 7 записи первого элемента 1 памяти соединен с переключающим контактом 8 переключателя 5, а его выход 9 - с входом 10 записи с второго элемента 2 памяти, запрещающий вход I1 которого соединен с первым входом 12 записи третьего элемента 3 памяти, выход 13 которого соединен с размыкающим контактом 14 переключателя 5, замыкающий контакт 15 которого соединен с выходами 16 и 17 соответственно второго 2 и четвертого 4 элементов памяти и с информационным выходом 18 устройства. Тактовые выходы 19-21 соответственно второго 2, третьего 3 и четвертого 4 элементов памяти соединены с первьи тактовым входом 22 - устройства. Первый 23 и второй 24 переключаювр1е контакты переключателя 6 соединены соответственно с выходом 9 первого элемента 1 памяти и с вторым тактовым входом 25 устройства, который, в свою очередь, соет динен с тактовым входом 26 первого элемента 1 памяти. Первый и второй размыкаки1ще контакты 27 и 28 переключателя 6 соединены соответственно с вторым входом 29 записи и с запрещающим входом 30 третьего элемента 3 памяти. Первый вход 12 записи третьего элемента 3 памяти соединён с входом 31 записи четвертого элемента 4 памяти, запрещающий вход 32 которого соединен с выходом 9 первого элемента 1 памяти. При этом второй вход 33 записи первого элемента 1 памяти и вход 31 записи четвертого элемента 4 памяти соединены соответственно с первым и вторым информационными входами 34 и 35 устройства,

Эленекты 1-4 QnyjcjiT да RpHfsMai,, И i вире дедеийш мемеити времени еданйци ««

формации (бита). Если на вход записи поступает сигнал I, элемент памяти запоминает информацию путем . перехода в новое (единичное состоя-

ние. Данная, информация может быть считана с элемента памяти путем подачи сигнала счнтьшания на тактовый вход элемента памяти. При этом на его выходе появляется сигнал 1,

а сам элемент памяти возвращается в исходное (нулевое)состояние.

Если же в момент записи информации на запрещающий вход элемента памяти также подан сигнал, записи 1 в элемент памяти не производится.

При наличии-у элемента памяти двух входов записи и запрещающего . входа он может быть использован также для реализации логической one-

Q. рации Кощ юнкция. При этом входные переменные на входы записи и тактовый сигнал на запрещающий вход элемента памяти подаются одновременно,

5 В зависимости от конкретных требований, предъявляемых к устройству для обработки цифровых данных, элементы памяти могут иметь различное констр5тетивное вьтолнение. Они

Q могут быть вьшолнены, например, на магнитно-диодных элементах. При необходимости снизить требования к стабильности амдлитуды и длительности тактовых сигналов возможно использование магнитно-транзисторных

элементов. Если же требуются схемы повышенной надежности, способные работать в условиях радиации и значительных изменениях температуры элементы памяти могут быть вьшолнены на магнитно-магнитных элементах с минимальным числом полупроводниковых приборов и используемых источников постоянного напряжения.

Устройство для обработки цифровых данных работает следующим образом,

В режиме работы Полусумматор устройство осуществляет сложение двоичного кода с единицей младщего разряда, Дпя этого замыкаются контакты 8 и 14 переключателя 5 и контакты 23, 27 и 24, 28 переключателя 6. Перед началом сложения в момент времени tp все элементы 1-4 памяти уста5 навлирещте Р исходнре, (нулевое) среТОЯйИе (ча чертеже дл иростеты| устййевкй О не рокаэай), В ме ме«т t: на 34 ygfpQftoTia пестуя пает единица младшего разряда, которая запоминается в элементе 1 памя ти. Одновременно действующийсигнал первого такта на входе 22 устроит ства не изменяет исходного состояния элементов 2-А памяти. В момент t на вход 35 устройства поступает первый разряд двоичного кода, а на его вход 25 - сигнал второго такта. Если первый разряд двоичного кода равен 1, то он запрещает запись в элементе 2 памяти единицы, считанной с элемента 1 памя ти. Аналогично сигнал с выхода 9 эле мента 1 запрещает запись в элемент 4 первого разряда двоичного кода. Для элемента 3 памяти в такте t единичные сигналы поступают на оба его входа 12 и 29 записи. Одновремен но тактовый сигнал с входа 25 устрой ства поступает на его запрещающий. вход 30. Суммарное действие единичных сигналов на входах 12 и 29 оказы вается больше, чем действие запрещающего сигнала на входе 30 (т.е. происходит превышение порога, устанавли екого сигналов запрета), в результат чего элемент 3 памяти переходит в со стояние 1, реализуя тем самым логическую операцию Конъюнкция. В но .вом такте t эта 1 в качестве сигнала переноса от суммирования двух. единиц по входам полусумматора появ. ляетея на выходе 13 элемента 3 памяти и через контакты 14 и 8 переключателя 5 записывается в элемент I памяти для последующего суммирования с очередным (вторвлм) разрядом двоичного кода. При этом сигнал на выходе 18 устройства отсутствует, так как элементы .2 и 4 памяти не из- меняют своего исходного состояния, т.е. первый разряд результата сложения соответствует О. (При этом и последующих тактах t сигналы на вход 34 не подаются . Если второй разряд двоичного кода также равен I, то в новом такте t на вход 35 устройства вновь поступает единичный сигнал, запрещающий запись информации в элемент 2 памяти. Аналогично сигналом с выхода 9 элемента 1 запрещается запись информации в элемеит 4 памяти. При этом в элемент 3 памяти записывает§я ciiQBa М % которая в следующем t, э к§честве д|{11И|цы nftpe- ilQca sffiiiHeffflSeTQg g 1 ттп тй, 6 чьесед 18 Фнш§ется 0, wm как элементы 2 и 4 памяти по-прежнему не изменили своего исходного состояния. Если в третьем разряде двоичного кода будет нуль, то в очередном такте t 2 информация с элемента 1 памяти перепишется в элемент 2 памяти, но в результате действия тактового сигнала на входе 30 не запишется в элемент 3 памяти. Следующий тактовый сигнал ti на входе 22 устройства считает 1 с элемента 2 памяти, которая поступит на выход 18 устройства (т.е. третий разряд результата сложения будет равен 1). При этом переноса в старший разряд не будет и элемент памяти 1 сохранит свое состояние О и т.д.. Следовательно, устройство при , данной коммутации контактов ключей 5 и 6 обеспечивает реализацию функций полусумматора. Для работы устройства в режиме преобразования двоичного кода в код Грея достаточно замкнуть контакты 8 и 14 переключателя 5 и разомкнуть контакты 23, 27 и 24, 28 переключателя 6. При этом вход 34 устройства не используется, а на вход 35 при каждом такте t подаются разряды преобразуемого, двоичного кода (старшими разрядами вперед). При этом каждый разряд двоичного кода запоминается в элементе 3 памяти, затем в такте t переписьтается в элемент 1 памяти для последующего сложения с очередным разрядом двоичного кода, также поступающим на вход 35 устройства.. Разряды кода Грея (старшим разрядом эперед J снимаются при каждом последующем такте t с выхода 18 устройства. Дпя обратного преобразования кода Грея в двоичный код достаточно замкнуть контакты 8 и 15 переключателя 5 и разомкнуть контакты 23, 27 и 24, 28 переключателя 6. При этом вход 34 устройства также не используется, а на вход 35 при каждом такте t подаются разряды преобразуемого кода Грея старшим разрядом вперед . При каждом последующем такте t с выхода 18 устройства снимается очередной разряд кода Грея, который также, благодаря рбратной связи, запоминается в эл§н§ЙТе 1 памяти, В следр)щем тактр fejj д ущестрлрется слоще«

51200431 .6

ние его со следующим разрядом кода его выхода 13 могут быть использоГрея на элементах 2 и 4 памяти и ваны для индикации работы устройства т.д.или для передачи информации с входа

Элемент 3 памяти в этом режиме ра- 35 данного устройства на вход другоботы не используется-, но сигналы с 5 о устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки цифровых данных | 1986 |

|

SU1424008A1 |

| Устройство для обработки цифровых данных | 1985 |

|

SU1405048A1 |

| Преобразователь кода Грея в двоичный код и обратно | 1982 |

|

SU1089571A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1986 |

|

SU1505257A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Устройство дискретной обработки информации | 1980 |

|

SU884140A1 |

| Фотоэлектрический преобразователь перемещения в код | 1984 |

|

SU1211889A1 |

| Устройство для моделирования ветви графа | 1986 |

|

SU1348847A1 |

9 п

Авторы

Даты

1985-12-23—Публикация

1984-06-19—Подача