(,)

f VV«;;

а

4

Ю

4

00

k.)

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке универ- caл7JИ Ix систем обработки цифровой информации, в частности при моделировании работы системы управления подвижными звеньями специализированных роботов-манипуляторов .

Цель изобретения - расширение функ циональных возможностей путем подсум- мирования переноса из предыдущего разряд а с

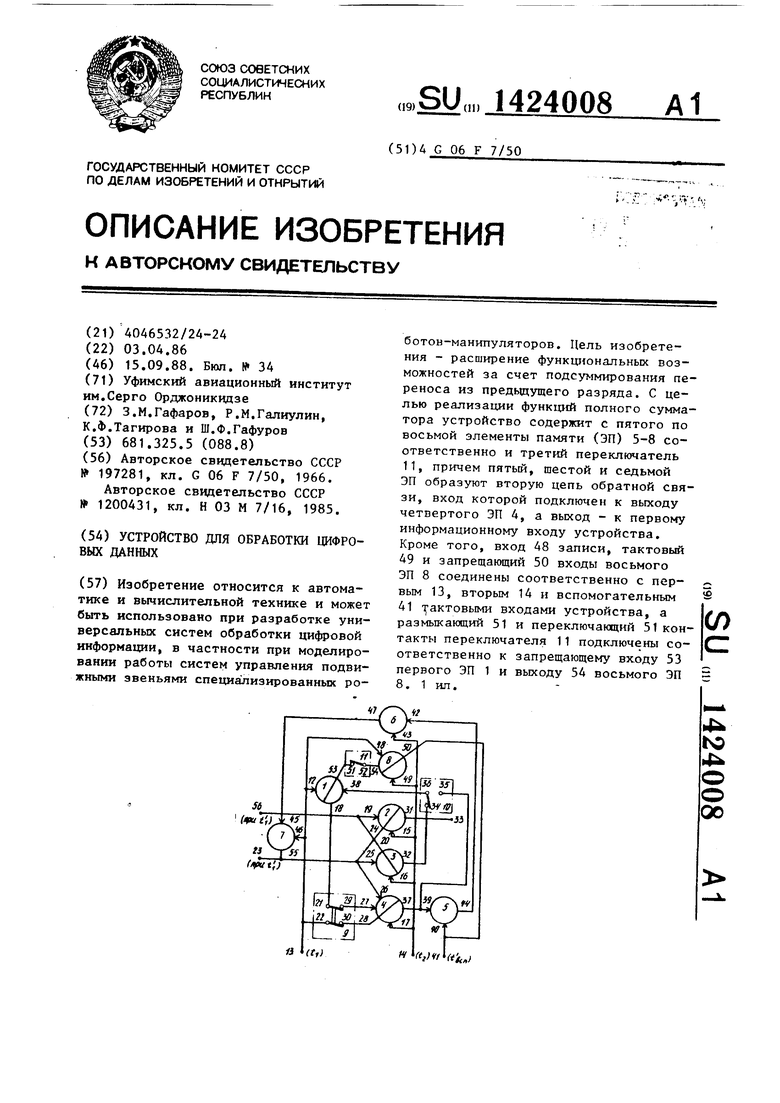

На чертеже представлена структурная схема устройства для обработки ци(}ф о вых д а н ных о

Устройство для обработки цифровых даниьк содержит восемь элементов 1-8 памяти и три переключателя 9-11. Тактовый вход 12 первого элемента 1 памяти соединен с первым тактовым входом 13 устройства, второй тактовьй вход 14 которого подключен к тактовым вкодам 15-17 соответственно вто

5

0

соответственно с выходом АА пятого элемента 5 памяти и вторым тактовым входом 14 устройства, вход 45 записи и тактовый вход 46 седьмого элемента 7 памяти подключены соответственно к выходу 47 шестого элемента 6 памяти и к первому тактовому входу 13 устройства, вход 48 записи, тактовьй 49 и запрещающий 50 входы восьмого эпе- мента 8 соединены соответственно с первым 13, вторым 14 и вспомогательным 41 тактовыми входами устройства, размьжающий 51 и переключающий 52 контакты третьего переключателя 11 подключены соответственно к запрещающему входу 53 первого 1 и выходу 54 восьмого 8 элементов памяти, а выходы 18 и 55 первого 1 и седьмого 7 соответственно элементов памяти соединены с вторым 56 и первым 23 соответственно информационными входами устройства.

Элементы 1-8 памяти служат для

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки цифровых данных | 1984 |

|

SU1200431A1 |

| Устройство для обработки цифровых данных | 1985 |

|

SU1405048A1 |

| Преобразователь кода Грея в двоичный код и обратно | 1982 |

|

SU1089571A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке универсальных систем обработки цифровой информации, в частности при моделировании работы систем управления подвижными звеньями специализированных роботов-манипуляторов. Цель изобретения - расширение функш1ональных возможностей за счет подсуммирования переноса из предьщущего разряда. С целью реализации функций полного сумматора устройство содержит с пятого по восьмой элементы памяти (ЭП) 5-8 соответственно и третий переключатель 11, причем пятый, шестой и седьмой ЭП образуют вторую цепь обратной связи, вход которой подключен к выходу четвертого ЭП 4, а выход - к первому информационному входу устройства. Кроме того, вход 48 записи, тактовый 49 и запрещающий 50 входы восьмого ЭП 8 соединены соответственно с первым 13, вторым 14 и вспомогательным 41 актовыми входами устройства, а размыкающий 51 и переключающий 51 контакты переключателя 11 подключены соответственно к запрещающему входу 53 первого ЭП 1 и выходу 54 восьмого ЭП 8. 1 ип. (Л

рого 2, третьего 3 и четвертого 4эле-25 приема, хранения и вьщачи в определенные моменты времени единицы (1 бита) информации. Если на вход записи поступает сигнал 1, элемент памяти запоминает информацию путем перехода в новое (единичное) состояние. Длинная информация может быть считана с элемента памяти путем подачи сигнала считывания на тактовый вход элемента памяти. При этом на его выходе появля30

ется сигнал 1, а элемент памяти

ментов памяти, выход 18 первого элемент 1 памяти соединен с входом 19 записи второго элемента 2. памяти, с затгрещаю цпм входом 20 третьего элемента 3 па1 :ят11 и переключающим контактом 21 первого переключателя 9, B i opoH переключающий контакт 22 которого подключен к первому тактовому иходу 13 ycTpoiicTBa, первьй ииформа- UHOiCibTi i вход 23 которого соединен с запрсща оаи1м входом 24 второго элемен- 35 возвращается в исходное (нулевое) состояние.

Если же в момент записи информации на запрещающий вход элемента памяти i также подан сигнал, запись 1 в элемент памяти не производится.

При наличии двух входов записи и запрещающего входа элемент памяти может быть использован для реализации (на входе) логической onepaumi И, при этом входные переменные на входы записи и тактовый импульс на запрещающий вход элемента памяти подаются одновременно.

При объединении выходов двух элементов памяти на их общем выходе реализуется логическая операция ИЛИ.

Операция ИЛИ в устройстве реализована также на одном элементе (элементе 5) памяти. Входные переменные 55 подаются на один и тот же вход 39 элемента, но в разные моменты вреуе- ни. При считьшании информации с данного элемента на его выходе 44 появта пгмяти, с входом 25 записи третьего элемента 3 памяти и первым входом 26 записи четвертого элемента 4 памяти, BTOpoii вход 27 записи и запрещающий вход 28 которого подключены 40 соотнетстленио к первому 29 и второг-гу 30 разьп.П са101Д11м контактам первого пе- рекльэчателя 9, выходы 31 и 32 соответственно второго 2, третьего 3 эле- ментов памяти соединены с выходом 33 45 устрс5Йства и размыкающим контактом 34 irroporo переключателя 10, замыкающий 35 и переключающ1ш 36 контакты которого подключены соответственно к 37 четвертого 4 и входу 38 записи первого элемента 1 памяти.

Вход 39 записи л тактовый вход 40 пятого элемента 5 памяти подключены соответственно к выходу 37 четвертого элемента 4 памяти и вспомогатель- тактовому входу 41 устройства, вход 42 записи и тактовый вход 43 шестого элемента 6 памяти соединены

50

ется сигнал 1, а элемент памяти

возвращается в исходное (нулевое) стояние.

ляется сигнал, соответствующий логической входных переменных;.

Устройство для обработки цифровых данных работает следурощим образом.

В режиме работы Полный сумматор замыкаются контакты 21,29 и 22,30 переключателя 9, контакты 34,36 переключателя 10 и контакты 51,52 переключателя 11.

Перед суммированием в момент времени все элементы 1-8 памяти устанав- Л1-гааются в исходное (нулевое) состояние (для простоты схема установки О не показана).

R момент времени t на тактовый вход 13 устройства подается импульс первого такта, на тактовый вход 41 - импульс вспомогательного такта, а на информационные входы 23 и 56 устройства - сигналы, соответствующие раз- рядаь1 Х| и Yi слагаемых (,2, 3.. .п) (в устройстве 1

представляется наличием, а О - отсутствием сигнала).

Если , то в элемент 3 памяти записывается 1 и запрещается запись информации в элемент 2 памяти. Если Yj 1, то в элемент 2 памяти записывается l, а запись информации в эле

мент 3 запреп(ается. Если , то запись информации в элементы 2,3 пам уи не происходит.

Действие каждого сигнала и Вчотдельности ira входах 26,27 элемента 4 памяти выбрано г- еньимм действия тактового сигнапа на его входе 28, поэтому запись информации данный элемент производится лишь при (происходит превьппение порога, устанавливаемого сигналом запрета) .

Записи 1

в элемент

памяти по

ходное состояние элементов 1,5, мяти соответствует О, при t/ сигего входу 48 при t не происходит

1

вследствие того, что на его запрещающем входе 50 присутствует импульс такта tjjy, . Кроме того, так как ис 7 па- 0, при t/ налы на их выходах отсутствуют.

В момент времени t на вход 14 устройства подается импульс второго такта, считывающий информацию с элементов 2-4, 6,8 памяти, при этом на общем выходе элементов 2,3 памяти реализуется логическая операция

, +XrY;. I

где с - частичная сумма, образующаяся при сложении двух разрядов Xi и Y{ слагаемых.

Значение С/ записывается при ti в элемент 1 памяти по его входу 38,

На выходе 37 элемента 4 памяти появляется сигнал, соответствующий

Пг XiYi ,

Q

где Пг - частичный перенос, образующийся при сложении двух разрядов X; и Y- слагаемых. f t- t.

Значение П{ записывается при t в элемент 5 памяти по его входу 39. При этом сигналы на выходах 47,54 эле5 ментов 6,8 памяти отсутствуют.

В новом такте (такте t) с подачей импульса на вход 13 устройства (на входе 41 тактовый импульс при этом отсутствует) происходит считыQ вание информации с элемента 17 памяти и запись 1 в элемент 8 памяти. При этом на выходе 18 элемента 1 памяти появляется сигнал С , поступающий на входы 19,20,27 элементов 2-4

5 памяти, а на выходе 55 элемента 7 памяти появляется сигнал Rv-i переноса от сложения предьщущих разрядов и , поступающий на входы 24-26 элементов 2-4 памяти (в данном случае Хг - Yj П{- 0) .

В новом такте (такте tj ) с подачей импульса на вход 14 устройства происходит считывание информатдии с элементов 2-4, 6, 8 памяти, при этом на обп1ем выходе элементов 2,3 памяти

5

реализуется логическая операция

С , + С/ П..,,

где С - результат сложения (сумма) 40 разрядов Xj и Yj слагаемых. Значение С поступает в момент t на выход 33 устройства, но запись его в элемент 1 памяти при этом не происходит, так как на его входе 53 при- 45 сутствует запрещающий сигнал, считан- Hbtfi с элемента 8 памяти.

При t/ на выходе 37 элемента 4 памяти поягшяется также сигнал, соот- ветствующий

50

п; с,п,,|,

где П; - частичньй перенос, образо- ванньш при сложении значения частичной суммы со зна- MeiiHeM переноса из предыдущего (i-l)-ro разряда. Значение П/ записывается при t/

в элемент 5 памяти по его иходу 39,

55

при этом сигнал на выходе 47 элемента 6 памяти отсутствует. j

В следующем такте (такте t) вновь происходит подача тактовых импульсов на входы 13,41 устройства и подача значений Х; и Y, на входы 23,56 устройства. В результате значение , поступает на входы 24-26 элементов 2-4, значение {4 - на входы 20, 19,27 элементов 2-4, а на выходе 44 элемента 5 появляется сигнал, соответствующий

П1 Пг ,

где П - значение переноса в следующий (1+1)-й (старший) разряд, появляющийся в резуль- тлте сложения разрядов X; и Y слагпемь-х.

пялюггие Пг записывается,при t,, в эломепт 6 памяти по его входу 42, при птом запись 1 в элемент 8 памяти отсутг.тпз ет вследствие наличия за- прещг.ющсго ит-тульса л его входе 50. П следующем такте (tj) происходит i)Oij:nT-Tonn tne сигнала С X..; + а общем иькодо элементов пиачеиио котс-рого записы- пам.чтп, формт-фова- Y., па выходе 37 , значеипс которого за11И)п; О-тсгг )3 племепт 5 памяти, и пес озлппс- . зиачештя /7 из элемента 6

х,. Y;M

2,3 пл -т ;т1

ваетоя л элемент 1 /

НПО гмг :- ;; /7; Х,-,

в :):ie:.tr TiT 7 памяти (па |.1ходе 54 эле- щий собой результат сложения двух мента 8 памяти сигнал огсутствует) . разрядов, а с выхода 37 элемента 4

вход 38 элемента 1 памяти

В слодуичдсм такте (t ) тактовьп импульс подается только на вход 13 устро1гства, в результате чего происходит считывание информац1ги с элементов 1,7 памяти и запись 1 в элемент 8 памятиt На выходе 18 элемента 1 по40

памяти на вход 38 элемента 1 поступает сигнал переноса от сложения указанпьк разрядов, который в по следующтс тактах складывается с оче редн1-1м разрядом двоичного кода, и т.д.

Я1зляется сигнал С

14-/

поступаюш.Ш па

входм 19,20,27 элементов 2-4, на BIJ- ходе 35 элемента 7 появляется сиг иол /1,, поступающий па входы 24-26 зле- меитон 2-4.

PJ следующий момент (т&кт tj) с подачей импульса на вход 14 устройства происходит считывание информации с элементов 2-4,6,8 памяти. В результате па общем вькоде элементов 2,3 па- мяти реализуется сигнал С:, + +Ct-ti -i. записьтаемый в элемент 1 памяти, на выходе 37 элемента 4 памяти реализуется сигнал П , i. за- писыБае -1ый в элемент 5 памяти, на выходе 54 элемента 8 памяти появляется г-игнал 1, запрещающий запись значе

ния Сг +1 п элемент 1 памяти, на выходе 47 элемента 6 памяти при этом присутствует сигнал О.

В новом такте (такте t) с поступлением тактовых импульсов на входы 13,41 происходит считывание значения П-|ц Л t с элемента 5 памяти и подача значений Xjf {,.г информационные входы 23,56 устройства. В дальнейшем работа устройства аналогична описанной выше.

Ecjni после появления на выходе 33 устройства сигнала С, на элементе 5

g памяти сформировалось значепие , то оно последующими тактовыми импульсами продвигается через элементы 6,7, 8 памяти и с выхода 32 элемента 3 памяти поступает на выход 33 устройства в качестве старшегоразряда С„,1 суммы, т.е. устройство правильно работает при любых значениях Х, Y ,П,--( .

При работе устройства в режиме Полусумматор замыкаются контакты

2 21,29 и 22,30 переключателя 9, контакты 35,36 переключателя 10 и размыкаются контакты 51,52 переключателя 11, при этом устройство осуществляет сложение двоичного кода с 1 млад- щего разряда. Последняя подается на

0

0

вход 56 устройства в момент t одновременно с первым разрядом двоичного кода, поступающим на вход 23 устройства. В такте С, на выходе 33 устройства появляется сигнал, про.дставляювход 38 элемента 1 памяти

0

5

памяти на вход 38 элемента 1 поступает сигнал переноса от сложения указанпьк разрядов, который в по- следующтс тактах складывается с оче- редн1-1м разрядом двоичного кода, и т.д.

Тактопьй вход 41 устройства при работе его в режимп Полусумматор по используется.

Я 1я работы устройства в режиме Двоичный Грея достаточно замкнуть контакты 35,36 переютючате- лл 10 и разомкнуть контакты 21,29 и 22,30 переключателя 9 и контакты 51, 52 переключателя 11, при этом входы 41,56 з -тройства на используются, а па нход 23 при каждом такте t подаются разряды преобразуемого двоично- 5 го кода (старшими разрядами вперед). Ка:вдый разряд двоичного кода запоминается в элементе 4 памяти, затем в такте tj переписьгаается в элемент 1 памяти для последующего сложения с

0

очередным разрядом двоичного кода, поступающим на вход 23 устройства. Разряды кода Грея (старшим разрядом вперед) снимаются при каждом такте с выхода 33 устройства.

Для обратного преобразования кода Грея в двоичный код достаточно замкнуть контакты ЗА,36 переключателя 10 и разомкнуть контакты 21,29 и 22, 30 переключателя 9 и контакты 51,52 переключателя 11. При этом входы 41, 56 устройства также не используются, а на вход 23 при каждом такте t подаются разряды преобразуемого кода Грея (старшим разрядом вперед). При каждом такте tj, с вькода 33 устройства снимается очередной разряд двоичного кода, который благодаря обратной связи также запоминается R элементе 1 памяти. В Следующем такте t/ осуществляется сложение его со следующим разрядом кода Грея на элементах 2,3 памяти и т.д.

Формула изобретения

Устройство для обработки цифровых данных, содержащее четыре элемента памяти и первый и второй переклюнате- ли, причем тактовый вход первого элемента памяти соединен с первым тактовым входом устройства, второй тактовый вход которого подключен к тактовым входам второго, третьего и четвертого элементов памяти, выход первого элемента памяти соединен с входом записи второго элемента памяти, с запрещающим входом третьего элемента памяти и первым переключающим контактом первого переключателя, второй переключающий контакт которого подключен к первому тактовому входу устройства, первый информационный вход которого соединен с запрещающим вхоДОМ второго элемента памяти, с входом 45 ройства.

0

5

0

записи третьего элемента памяти и первым входом записи четвертого элемента памяти, второй вход записи и запрещающий вход которого подключены соответственно к первому и второму размыкающим контактам первого переключателя, выходы второго и третьего элементов памяти соединены с выходом устройства и размыкающим контактом второго переключателя, замыкающий и переключающий контакты которого подключены соответственно к выходу четвертого и входу записи первого элементов памяти, отличающееся тем, что, с целью расширения функциональных возмо жностей за счет возможности подсуммирования переноса из предьщущего разряда, оно содержит пятый элемент памяти, вход записи и тактовьй вход которого подключены соответственно к выходу четвертого элемента памяти и вспомогательному тактовому входу устройства, шестой

g элемент памяти, вход записи и тактовый вход которого соединены соответственно с выходом пятого элемента памяти и вторым тактовым входом устройства, седьмой элемент памяти, вход записи и тактовый вход которого подключены соответственно к выходу шестого элемента памяти и первому тактовому входу устройства, восьмой элемент памяти, вход записи, тактовый и запрещающий входы которого соединены

5 соответственно с первым, вторым и вспомогательнь тактовым входами устройства, и третий переключатель, размыкающий и переключающий контакты которого подключены соответственно к запрещающему входу первого и выходу восьмого элементов памяти, а выходы nepBord и седьмого элементов памяти соединены соответственно с вторым и первым информационными входами уст0

0

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 0 |

|

SU197281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки цифровых данных | 1984 |

|

SU1200431A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-15—Публикация

1986-04-03—Подача