Изобретение относится к автоматике и импульсной технике и используется для формирования исполнительной команды через определенный промежуток времени, задаваемый кодом перед запуском таймера.

Целью изобретения является увеличение достоверности контроля.

На фиг. 1 приведена функциональная схема таймера; на фиг.2 - временные диаграммы его работы в режимах записи и контроля.

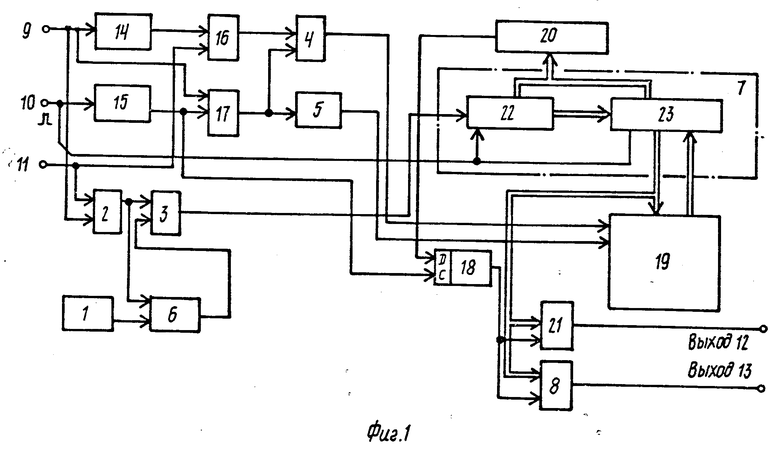

Таймер содержит задающий генератор 1, элемент 2 сложения по модулю два, элементы ИЛИ 3,4, элемент 5 задержки, делитель 6 частоты, счетчик 7 в коде Грея, блок 8 ключей, вход 9 разрешения записи, вход 10 начальной установки, вход 11 разрешения контроля, выход 12 сбоя, группу 13 информационных выходов, формирователи 14, 15 импульсов, элементы И 16, 17, триггер 18, блок 19 памяти, блок 20 свертки по модулю два, дешифратор 21. Счетчик 7 в коде Грея содержит группу младших разрядов 22, группу старших разрядов 23.

В качестве формирователя 14 импульсов может быть использован селектор импульсов по амплитуде, селектор импульсов по длительности, что определяется необходимостью защиты от помех.

В качестве формирователя 15 импульсов можно применить любой формирователь, формирующий импульсы по заднему фронту входного сигнала.

В состав блока 19 памяти могут быть включены любые элементы, сохраняющие информацию в отсутствие напряжения питания, например трансформаторы на сердечниках с ППГ, ЗУ на основе ЦМД, ЗУ на стеклообразных полупроводников, ЗУ на основе керамики.

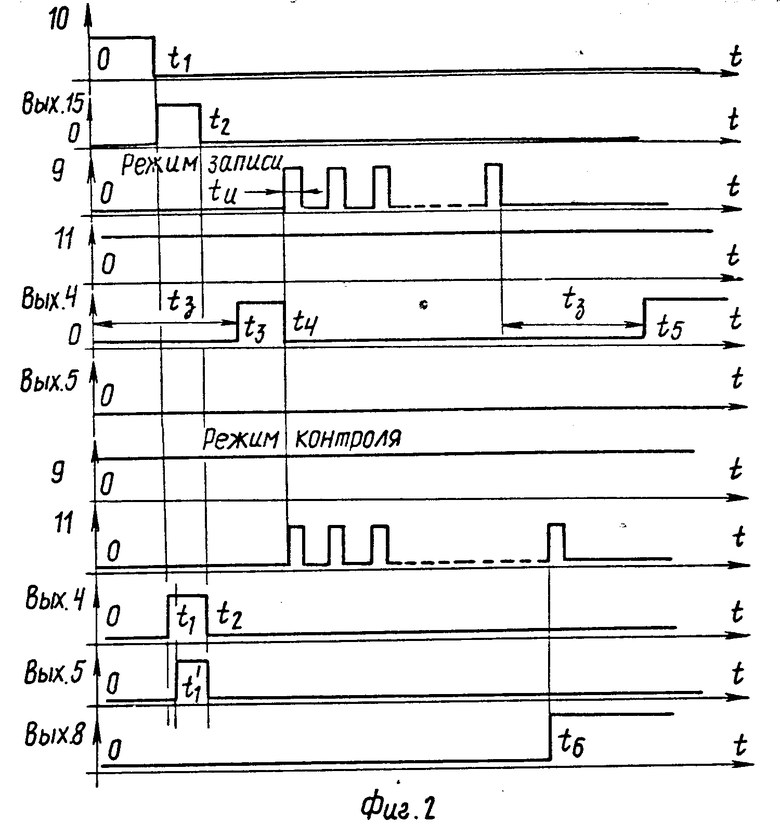

Работа таймера поясняется временной диаграммой, на которой сигналы обозначаются номерами соответствующего элемента или входа-выхода таймера.

В начале работы по входу 10 подается импульс начальной установки, устанавливающий в исходное состояние младшие 22 и старшие 23 разряды счетчика 7 (0-t1, фиг.4).

Задающий генератор 1 вырабатывает импульсы, поступающие на вход делителя 6 частоты. Импульс, поступающий по входу 10, проходит через формирователь 15 импульсов, который формирует по заднему фронту импульс начальной установки (t1 - t2, фиг.4), триггер 18 производит опрос выхода блока 20. На выходе блока 20 свертки по модулю два формируется сигнал, который несет информацию о состоянии разрядов счетчика: в режиме записи - о состоянии разрядов после приведения их в исходное состояние, в режимах контроля и отработки уставки - о состоянии разрядов после приведения их в исходное состояние и считывания информации из элементов памяти.

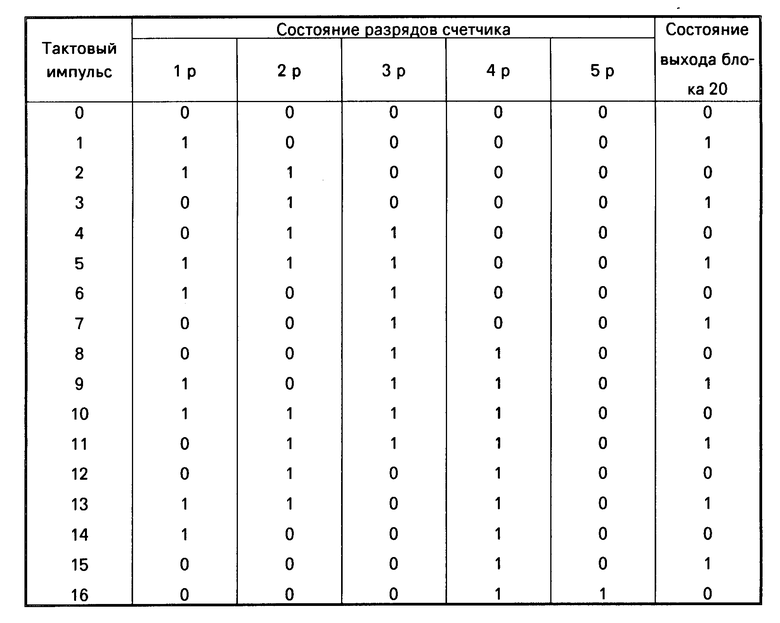

В режиме записи по входу 9 подается потенциал "лог.0", по входу 11 - потенциал "лог.1", последний разрешает прохождение сигнала записи на выход элементов И 16 и ИЛИ 4 (t3 - t4, фиг.4). В режиме записи младшие 22 и старшие 23 разряды счетчика предварительно обнуляются сигналом по входу 10 устройства. По сигналу записи (t3-t4, фиг.4) нулевое состояние старших разрядов счетчика записывается в элементы памяти блока 19 (очистка памяти). Затем по счетному входу счетчика поступают кодовые сигналы, количество которых определяется величиной задаваемой уставки. Указанные сигналы изменяют состояние счетчика в соответствии с кодом Грея. При организации счетчика в режиме сложения нечетными тактовыми сигналами переключается первый (самый младший) разряд счетчика, четными - разряд, следующий за самым младшим разрядом о состоянии "лог.1". Коды выходных сигналов счетчика, организованного в режиме сложения, приведены в таблице.

В приведенном в таблице примере все начальные состояния счетчика для простоты выбраны нулевыми. В устройстве начальные состояния старших разрядов счетчика определяются кодом задаваемой уставки.

На ход самого младшего из старших разрядов 23 первый тактовый сигнал поступит через 2m тактов работы.

После окончания последовательности кодовых сигналов в схеме повторно формируется сигнал записи, по которому состояние старших разрядов счетчика записывается в элементы блока 19 памяти (вых4, t5, фиг.4). Этим сигналом запрещается прохождение импульса считывания на выход элементов 17 и 5. Через время (t3), определяемое задержкой формирователя 14 импульсов, сигнал формируется на выходе элемента ИЛИ 14 в виде потенциала "лог.1". При поступлении сигнала записи в блок 19 памяти записывается нулевое состояние старших разрядов счетчика. На выходе элемента сложения 2 в течение рассмотренного интервала времени формируется сигнал, удерживающий разряды делителя 6 частоты импульсов в исходном состоянии, счетные сигналы на выходы элемента ИЛИ 3 отсутствуют. С поступлением на вход 9 кодовых импульсов формирование сигнала записи ("лог.1" на выходе элемента ИЛИ 4) заканчивается (момент t4 на фиг.4), одновременно кодовые импульсы через элементы 2 и 3 поступают на счетный вход счетчика 7. Кратковременная разблокировка делителя 6 по входу на время кодового импульса, поступающего по входу 9, не приводит к появлению импульсов на выходе делителя 6, так как длительность кодового импульса (t4) выбирается меньше, чем полупериод последовательности на выходе делителя 6.

Количество кодовых импульсов в режиме записи соответствует задаваемому значению временной установки, при этом с учетом дополнительных m младших разрядов 22 информация в старших разрядах 23 счетчика 7 изменяется только каждым 2m-М импульсом кодовой посылки. При выборе номинального числа кодовых импульсов в середине зоны нечувствительности старших разрядов (2m-1-1) можно реализовать отсутствие ошибок при записи как в случае появления в кодовой последовательности 2m-1 "лишних" импульсов, так и в случае пропадания (2m-1-1) импульсов в посылке. Необходимо также отметить, что номинальные числа кодовых импульсов для всех уставок должны выбираться такими, чтобы коды чисел, записываемых в старшие разряды, были четными. Для выполнения этого условия номинальные значения числа кодовых импульсов должны отстоять одно от другого на величину 2m+1. Это позволяет, во-первых, при выбранной организации счетчика получить постоянную дискретность ряда уставок; во-вторых, организовать обнаружение ошибок, связанных с искажением числа кодовых импульсов помехами за пределами зоны нечувствительности. После окончания последовательности кодовых импульсов через время t3 на выходе элемента ИЛИ 4 формируется сигнал записи (момент t5 на фиг.4), при этом в блок 19 памяти записывается информация с триггерных устройств старших разрядов 23, соответствующая заданной уставке.

Режим контроля записанной уставки может осуществляться как непосредственно после режима записи, так и после перерыва в питании неограниченной длительности. В режиме контроля записанной уставки так же предварительно младшие и старшие разряды счетчика обнуляются. Затем формируется система сигналов считывания (t1-t2; t21-t2, фиг.4), которая осуществляет считывание в старшие разряды счетчика информации из элементов памяти, причем считывание происходит только в те разряды счетчика, в которых соответствующие им элементы памяти находятся в состоянии "лог.1". В результате считывания старшие разряды счетчика находятся в состояниях, соответствующих величине уставки, записанной в предыдущем цикле записи. Затем на счетный вход счетчика поступают кодовые сигналы до тех пор, пока счетчик не заполнится. Заполнение счетчика осуществляется по описанному алгоритму кода Грея. Количество контрольных кодовых импульсов, поступивших в счетчик до его заполнения, несет информацию о времени отработки счетчиком заданной уставки, контроль указанного количества импульсов позволяет сделать вывод о правильности записанной уставки и работоспособности счетного блока.

В режиме отработки уставки счетчик импульсов работает так же, как и в режиме контроля, с той лишь разницей, что на его вход поступают низкочастотные тактовые сигналы с выхода делителя 6 через элемент ИЛИ 3.

Режим контроля может осуществляться многократно при однократной записи. В режиме контроля по входу 9 подается потенциал "лог.1", по входу 11 - потенциал "лог.0". В рассматриваемом режиме сигнал считывания проходит на выход элемента И 17 и элемента ИЛИ 4 (t1-t2, фиг.4), на выходе элемента задержки 5 формируется сигнал считывания с задержанным фронтом (t11-t2).

Сигналы из блока 19 памяти поступают на входы установки в "единицу" триггеров старших разрядов 23 счетчика 7, поскольку в начале цикла контроля разряды счетчика были приведены в начальное (нулевое) состояние, а в элементы памяти записана информация, соответствующая заданной установке.

Затем по входу 11 поступают кодовые импульсы, проходящие через элементы 2 и 3 на вход младших разрядов 22 счетчика 7. Кратковременная разблокировка по входу делителя 6 так же, как и в цикле записи, не приводит к появлению счетных сигналы на выходе делителя 6 импульсов.

После того, как счетчик 7 достигает нужного значения, на выходе блока 8 ключей появляется сигнал, используемый дальше при сравнении заданного и полученного кодов уставки (момент времени t6 на диаграмме фиг.4). Сигнал на выходе 12 ВУ в режиме контроля не формируется, поскольку дешифратор 21 блокируется стробом.

Поскольку в счете импульсов участвует m младших разрядов 22, схема, как и в цикле записи, нечувствительна к ошибкам в диапазоне от минус (2m-1-1) до 2m-1 импульсов от номинального значения, выбранного в середине зоны нечувствительности. В случае, если ошибка в количестве импульсов при записи составила величину, находящуюся в диапазоне от (2m-1-2-2m) до (2m-1-2) импульсов при пропадании, и величину, находящуюся в диапазоне от (2m-1+1) до (2m-1+1+2m) при появлении "лишних" импульсов, а также при отказах элементов схемы, приводящих к неустановке в исходное состояние одного из разрядов счетчика 7 и возможному искажению, вследствие этого величины отрабатываемой уставки, триггер 18 при опросе импульсом с выхода блока 20 установится в состояние "лог.1", запрещающее формирование сигнала на выходе блока 8 ключей. Отсутствие сигнала на выходе 13 в режиме контроля является информацией о неготовности к отработке заданной уставки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1832976A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1769611A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| ПРОГРАММНЫЙ ТАЙМЕР | 2001 |

|

RU2215367C2 |

| Делитель частоты с программируемым коэффициентом деления | 1987 |

|

SU1649659A1 |

| Устройство управления гелиостатом | 1983 |

|

SU1291925A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

Изобретение относится к автоматике и импульсной технике и используется для формирования исполнительной команды через определенный промежуток времени, задаваемый кодом перед запуском таймера. Цель изобретения - увеличение достоверности контроля. Отличительной особенностью таймера является то, что он контролирует одиночные отказы в схеме счетчика (неустановка разрядных триггерных устройств в исходное состояние, отказы логических схем типа "лог. 0" и "лог.1", отказы элементов памяти); устройство нечувствительно к ошибкам в кодовых посылках при записи на величину плюс 1, минум 1 импульс, в устройстве также обнаруживаются ошибки в кодовых посылках при записи на величину плюс 3 ... 6, минус 2 ... 5 импульсов (при номинальных значениях в середине зоны нечувствительности), устройство позволяет многократно (проверено при нескольких десятках включений) считывать, контролировать и отрабатывать однократно заданную уставку. Целью изобретения является увеличение достоверности контроля, поставленная цель достигается введением элемента ИЛИ 4, формирователей 14, 15 импульсов, элементов И 16, 17, элемента 5 задержки, блока 19 памяти. 2 ил., 1 табл.

ТАЙМЕР С КОНТРОЛЕМ, содержащий задающий генератор, делитель частоты, блок свертки по модулю два, счетчик в коде Грея, дешифратор, триггер, блок ключей, первый элемент ИЛИ, отличающийся тем, что, с целью увеличения достоверности контроля, в него введены элемент сложения по модулю два, второй элемент ИЛИ, два формирователя импульсов, два элемента И, элемент задержки и блок памяти, причем выход задающего генератора соединен с информационным входом делителя частоты, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом элемента сложения по модулю два и с входом сброса в "ноль" делителя частоты, первый вход элемента сложения по модулю два соединен с первым входом первого элемента И и является входом разрешения контроля таймера, второй вход элемента сложения по модулю два соединен с входом первого формирователя импульсов, с первым входом второго элемента И и является входом разрешения записи таймера, выход первого формирователя импульсов соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с входом элемента задержки, выход второго формирователя импульсов соединен с вторым входом второго элемента И и с синхровходом триггера, выход второго элемента ИЛИ соединен с входом разрешения записи блока памяти, вход разрешения считывания которого соединен с выходом элемента задержки, вход сброса в "ноль" счетчика в коде Грея соединен с входом второго формирователя импульсов и является входом начальной установки таймера, выход первого элемента ИЛИ соединен со счетным входом счетчика в коде Грея, разрядные выходы которого соединены с входами блока свертки по модулю два, выход которого соединен с информационным входом триггера, выход которого соединен со стробирующим входом дешифратора и с управляющим входом блока ключей, выход дешифратора является выходом таймера, группа выходов блока ключей является группой информационных выходов таймера, выходы блока памяти соединен с входами установки в "единицу" старших разрядов счетчика в коде Грея, группа старших разрядов которого соединена с группой информационных входов дешифратора и с группой информационных входов блока ключей.

| Датчик времени | 1984 |

|

SU1221646A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-15—Публикация

1986-04-07—Подача