Изобретение относится к автоматике Ц вычислительной технике и может быть использовано при обработке универсаль Цых систем обработки цифровой инфор- , в частности при моделировании работы преобразователей типа переме- дение-код, используемых в системах управления подвижными звеньями робо- тов-манипуля торов.

Цель изобретения - расширение функциональных возможностей путем обеспечения преобразования кода Баркера в двоичный код.

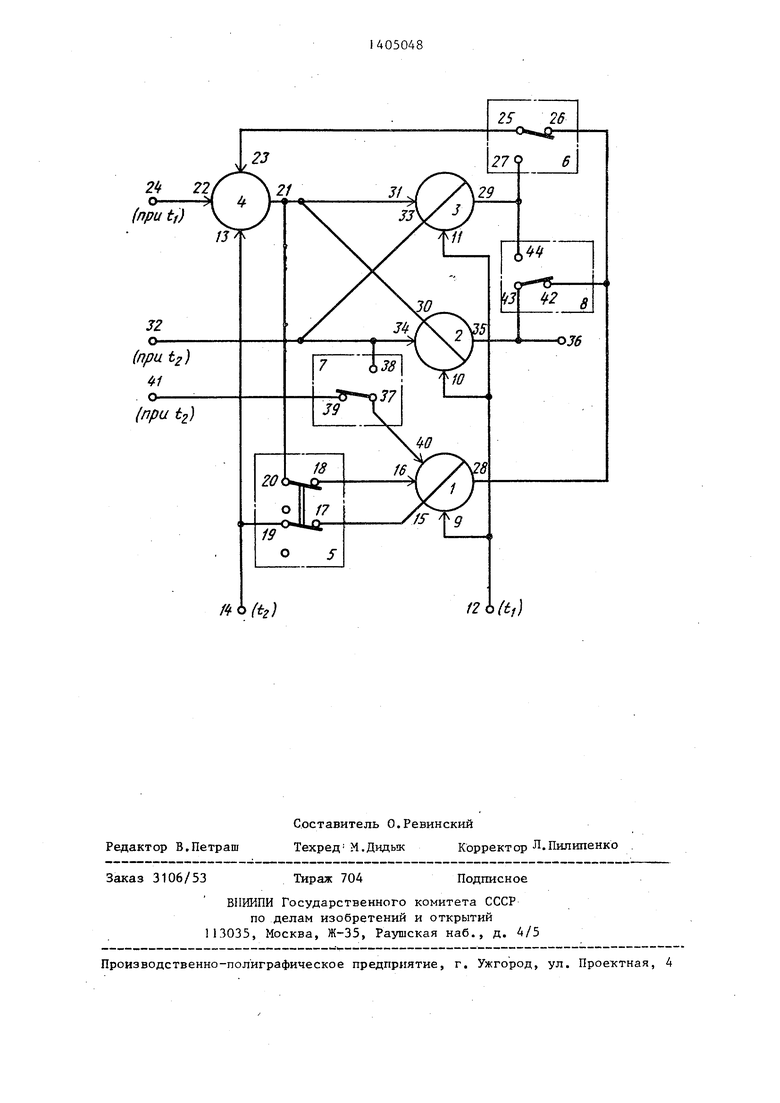

На чертеже приведена функциональ- нал схема устройства.

Устройство содержит элементы 1-4 памяти, переключатели 5-8, тактовые входы 9-11 элементов 1-3 памяти, тактовый вход 12 устройства, тактовьш вход 13 элемента 4 памяти, тактовьй вход 14 устройства, первьй вход 15 записи и запрещающий вход 16 элемента 1 памяти, первый 17 и второй 18 размыкающие контакты переключателя 5, первьм 19 и второй 20 переключающие контакты переключател Я 5, выход 21 элемента 4 памяти, первый 22 и второй 23 входы записи элемента 4, первьй информационный вход 24 устройства, переключающий 25, размыкающий 26 и замыкающий 27 контакты второго перек- лючат.еля 6, выходы 28 и 29 соответственно элементов 1 и 3 памяти, запрещающий вход 30 элемента 2 памяти, вход 31 записи элемента 3 памяти, вто рой информационный вход 32 устройства, запрещающий вход 33 элемента 3 памяти, вход 34 записи и выход 35 элемента 2 памяти, выход 36 устройства, переключающий 37, замыкающий 38 и размьшающий 39 контакты третьего переключателя 7, второй вход 40 записи элемента 1 памяти, третий информационный вход 41 устройства, размыкающий 42, переключающий 43 и замыкающий 44 контакты четвертого переключателя 8.

Элементы 1-4 памяти служат для приема, хранения и выдачи в опреде- ленные моменты времени единицы (1 бит) информации. Если на вход записи поступает сигнал элемент памяти запоминает информацию путем перехода в новое (единичное) состояние. Данная информация может быть считана с элемента памяти путем подачи сигнала считывания на тактовый вход элемента памяти. При этом на его выходе появ

о 0

5

,

мяти возвращается в исходное (нулевое) состояние. Если в момент записи информации на запрещающий вход элемента также подан сигнал, запись 1 в элемент памяти не производится.

При наличии у элемента памяти двух входов записи и запрещающего входа он может быть использован для реализации (на входе) лргичегкой операции конъюнкции. При этом входные переменные на входы записи и тактовый сигнал на запрещающий вход элемента памяти подаются одновременно. При объединении выходов двух элементов памяти на их общем вьпсоде реализуется логическая операция дизъюнкция. Элементы памяти могут быть выполнены, например, на магнитно-диодных , магнитно-транзисторных или магнитно-магнитных элементах.

При работе устройства в режиме Код Баркера- двоичный код замыкаются контакты 17, 19 и 18, 20 переключателя 5, контакты 25 и 26 переключателя 6, контакты 37 и 39 переключателя 7 и контакты 42 и 43 переключателя 8. При этом в нем реализуется логическая функция вида

р . р А V р. т.

1+1 ft-i

где p. , Pj - значения i-го и (i+1)- го разрядов двоичного кода;

А.., , {. значения сигналов под- разрядов А и В (i+1)- го разряда, что соответствует следующему правилу преобразования: если в i-M разряде считан О, то в (i+1)M разряде считывание осуществляется с чувствительного элемента подразряда А преобразователя перемещение-код, если в i-M разряде считана 1, то в (i+t)-M разряде считывание осуществляется с чувстви- тельного элемента под- разряда В преобразователя перемещение-код.

Последовательность работы элементов устройства следующая.

при этом импульс второго такта по DX ду 16 запрещает запись 1 в элемен 1 памяти. В результате в новом такт t, на выходе 36 сигнал 1 отсутств ет:

Pi 1 -О V О- 1 0.

10

Перед началом преобразования в момент времени t все элементы 1-4 памяти устанавливаются в исходное (нулевое) состояние (схема установки О не показана). В следующий момент с поступлением тактового импульса t на вход 12 производится считывание информации с элементов 1 и 2 памяти соответственно по их входам 9 и 10. Так как, последние при этом находятся в исходном состоянии О, импульс на выходе 36 отсутствует, что соответст- вуе т Рр 0.

В следующий момент t на вход 14 15 поступает импульс второго такта, а на входы 32 и 41 устройства подаются соответственно информационные сигналы А и В;,. При этом, если , то на входы 32 и 41 подаются соответст- 20 ного элемента подразряда А. вующие им импульсы, поступающие на входы 34 и 40 элементов 2 и 1 памяти. Так как запрет записи информации в элемент 2 памяти по его входу

Если А, В О, то в обоих такт t и t-j элементы 1 и 2 памяти сохра няют свое исходное состояние О и на выходе 36 устройства имеем

, 1-0 V .

Следовательно, в начале работы уст- poficTBa (т.е. при РО 0) считывание всегда осуществляется с чувствитель

В новом такте t- на входы 32 и 4 устройства подаются информационные

п -ос сигналы, соответствующие А, и В.

30 отсутствует и последний переходит . „ .

.цг( / ПА 1 1 7 Если . 1,то сигн

в состояние 1 (т.е. P. 1).„.„ ,,. ,

.° 11 с выхода 21 элемента 4 памяти

сигнал выхода

запрещает по входу 30 запись 1 в элемент 2 памяти. Суммарное действи

Элемент 1 памяти при этом сохраняет исходное состояние О, так как импульс второго такта по входу 15 зал-„ „

, f сигналов и соответственно рещает запись в него информации (т.е. 30, с ,„

п п п 1 пчи входах 1Ь и 40 превышает деистви

Го 1 -1 и .

В новом такте t, производится считывание информации с элементов 1 и 2 памяти. При этом элемент 2 памяти возвращается в состояние О, а на. 35 имеем его выходе 35 возникает импульс, поступающий на выход 36 устройства и записывающий 1 в элемент 4 памяти по его входу 23. Следовательно, при этом на выходе 36 устройства реализуется 40 логическая операция дизнонкция:

входах 1 и и превышает действие второго тактового сигнала на входе 16, благодаря чему в элемент 1 памя записывается 1. В результате в сл дующем такте на выходе 36 устройств

Р PI A,jV Р,В 0-1 V 1- 1 1.

Если , Б 1, PI 1, то 1 в такте t записывается только в элемент 1 памяти, в результате чего на выходе 36 устройства имеем

, а элемент 1 сохра- 0. В новом

Р, P(,-A,V Р„- В, 1 V .

Если же А 1 и Б 0, то в такте t/2 информационньш сигнал поступает только на вход 32 устройства. В результате элемент 2 памяти переходит в состояние 1 няет исходное состояние такте t, на выходе 36 устройства реализуется логическая операция дизъюнкция : .

Р PoA,V , 1 -1 V 0-0 1.

Если А ,0 и В,0, то в такте t информационньш сигнал 1 поступает только на вход 41 yctpoйcтвa. Однако

при этом импульс второго такта по DXO- ду 16 запрещает запись 1 в элемент 1 памяти. В результате в новом такте t, на выходе 36 сигнал 1 отсутствует:

Pi 1 -О V О- 1 0.

ного элемента подразряда А.

Если А, В О, то в обоих тактах t и t-j элементы 1 и 2 памяти сохраняют свое исходное состояние О и на выходе 36 устройства имеем

, 1-0 V .

Следовательно, в начале работы уст- poficTBa (т.е. при РО 0) считывание всегда осуществляется с чувствительного элемента подразряда А.

В новом такте t- на входы 32 и 41 устройства подаются информационные

. „ .

Если . 1,то сигн

„.„ ,,. ,

1 с выхода 21 элемента 4 памяти

сигнал выхода

запрещает по входу 30 запись 1 в элемент 2 памяти. Суммарное действие

„ „

сигналов и соответственно , с ,„

и входах 1Ь и 40 превышает деистви

имеем

входах 1 и и превышает действие второго тактового сигнала на входе 16, благодаря чему в элемент 1 памяти записывается 1. В результате в следующем такте на выходе 36 устройства

ем

Р PI A,jV Р,В 0-1 V 1- 1 1.

имеем

Если , Б 1, PI 1, то в такте t записывается только элемент 1 памяти, в результате на выходе 36 устройства имеем

45

Р2 P.AjV. 0-0 V М 1.

Если , , , то в такте 11 элементы 1 и 2 памяти сохраняют свое исходное состояние О, так как

5Q под действием сигнала Р,1 с выхода 21 элемента 4 памяти запрещается запись информации на элемент 2 памяти, а действие этого сигнала по входу 13 оказывается недостаточным для переgg вода элемента 1 памяти в состояние 1. И результате в такте ц на выходе 36 устройства имеем

,A.;V Р,В,,0:1 V .

Если , то в такте t элементы 1 и 2 сохраняют свое состояние О и на выходе 36 устройства имеем

Р, В, 0-0 V 1- .

Следовательно, если Р,1, считыва- ние при любых А н В осуществляется только с чувствительного элемента В преобразователя перемещение-код.

Приведенные примеры показывают, что устройство правильно работает при любых значениях А, В и Р.

При работе устройства в данном режиме вход 24 и элемент 3 памяти не используются.

При работе устройства в режиме код Грея- двоичный код замыкаются контакты 25 и 27 переключателя 6 и контакты 43 и 44 переключателя 8 (состояние переключателей 5 и 7 безразлично). При этом входы 24 и 41 и элемент 1 памяти устройства не ис- польз5потся, а на вход 32 при каждом

такте tj подаются разряды преобразуемого кода Грея (старшими разрядами вперед). При каждом последующем такте с выхода 36 устройства снимается оче050486

ного кода (старшими разрядами вперед). При этом каждый разряд двоичного кода запоминается на элементе 1 памяти и далее в новом такте t переписывается в элемент 4 памяти для последующего сложения по модулю два с очередным разрядом двоичного кода (на элементах 2 и 3 памяти), также поступаю- 10 щим на вход 32 устройства. Разряды кода Грея (старимми разрядами вперед) снимаются при каждом последующем такте t с выхода 36 устройства. При работе устройства в режиме

полусумматора замыкаются контакты 17, 19 и 18,20 переключателя 5, контакты 25 и 26 переключателя 6, контакты 37 и 38 переключателя 7 и контакты 43 и 44 переключателя 8. При этом вход 41

не используется, а устройство осуществляет сложение двоичного кода с единицей младшего разряда. Последняя подается на вход 24 устройства в момент t и запоминается на элементе 4 памяти. В следующий момент t на вход 32 устройства поступает первьш разряд двоичного кода. При этом на элементах 2 и 3 памяти реализуются логические операции Запрет, а на элементе 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки цифровых данных | 1986 |

|

SU1424008A1 |

| Устройство дискретной обработки информации | 1980 |

|

SU884140A1 |

| Устройство для обработки цифровых данных | 1984 |

|

SU1200431A1 |

| Преобразователь кода Грея в двоичный код и обратно | 1982 |

|

SU1089571A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

редной разряд двоичного кода, который 30 памяти - логическая операция конъюнкция. В новом такте t, информация, записанная на элементе 1 памяти в качестве сигнала переноса от сложения двух разрядов, переписывается на элемент 4 памяти для последующего суммирования с очередным разрядом двоичного кода. Одновременно на объединенном выходе элементов 2 и 3 памяти реализуется логическая операция

35

также благодаря обратной связи запоминается в элементе 4 памяти. В следующем такте t осуществляется сравнение его со следующим разрядом кода Грея (путем сложения по модулю два на элементах 2 и 3 памяти),

Дпя работы устройства в режиме двоичньй код Грея достаточно замкнуть контакты 25 и 26 переключателя

ля 7, контакты. 43 и 44 переключателя 8 и разомкнуть контакты 17, 19, и 18, 20 переключа.теля 5, При этом входы 24 и 41 устройства также не используются, а на вход 32 при каждом такте подаются разряды преобразуемого двоич-контакты 37 и 38 переключате- 40 Дизъюнкция, результат которой в виде

результата сложения двух разрядов появляется на выходе 36 устройства.

Таким образом, в устройстве обеспечивается возможность преобразования кода Баркера и кода Грея в двоичный ОД, а также функции полусумматора.

(при tf)

(при t2

(при

(i:2)

Редактор В.Петраш

Составитель О.Ревинский

Техред М.Дидык Корректор Л.Пилипенко

Заказ 3106/53

Тираж 70А

ВИИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

f2b(6i)

Подписное

| Авторское свидетельство СССР № 913364, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки цифровых данных | 1984 |

|

SU1200431A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-23—Публикация

1985-07-04—Подача