1

Изобретение относится к устройствам для обработки цифровых данных.

Известно адаптивное вычислительное устройство, содержащее два многофункциональных логических блока, блоки сравнения и блок настройки 1. Это известное устройство характеризуется значительными затратами оборудования на два параллельно работающих многофункциональных блока. Наиболее близким к изобретению является известное адаптивное вычислительное устройство, содержащее входной регистр, основные многофункциональные блоки, подключенные к одним выходам распределителя функций, другие выходы которого соединены с соответствующими элементами «И, подключенными к выходному блоку и основным многофункциональным блокам 2. Это известное устройство требует больших аппаратурных затрат и имеет низкую надежность, так как в устройстве требуется память для хранения информации о типах потерянных функций каждого блока и их ресурсах.

Целью изобретения является упрощение схемы и новыщение надежности работы. В предложенном устройстве это достигается тем, что оно содержит дополнительные многофункциональные одноразрядные блоки, дополнительные элементы «И, сдвигающий регистр и блок сравнения, выходы которого подключены ко в.ходам выходного олока, сдвигающего регистра и распределителя функций, а входы- к выходу распределителя функций и к выходам дополнительных элементов «И первой и второй групп, одни входы которых соединены с выходами сдвигающего регистра, а другие - с выхода.ми входного регистра и с соответствующими элементами «И, одни входы дополнительных многофункциональных одноразрядных блоков подключены ко входам соответствующих основных многофункциональных блоков, а выходы и другие входы - к соответствующим дополнительным элементам «PI третьей группы, подключенным к одному из входов блока сравнения и соответствующим вы.ходам распределителя функций.

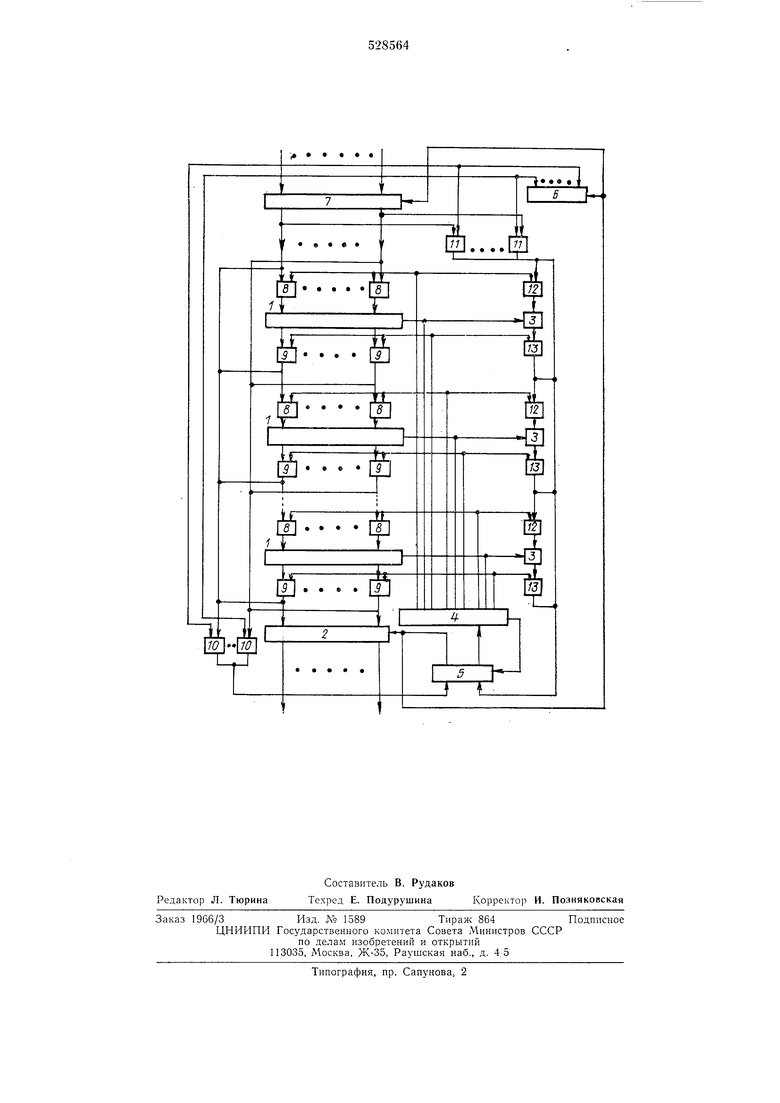

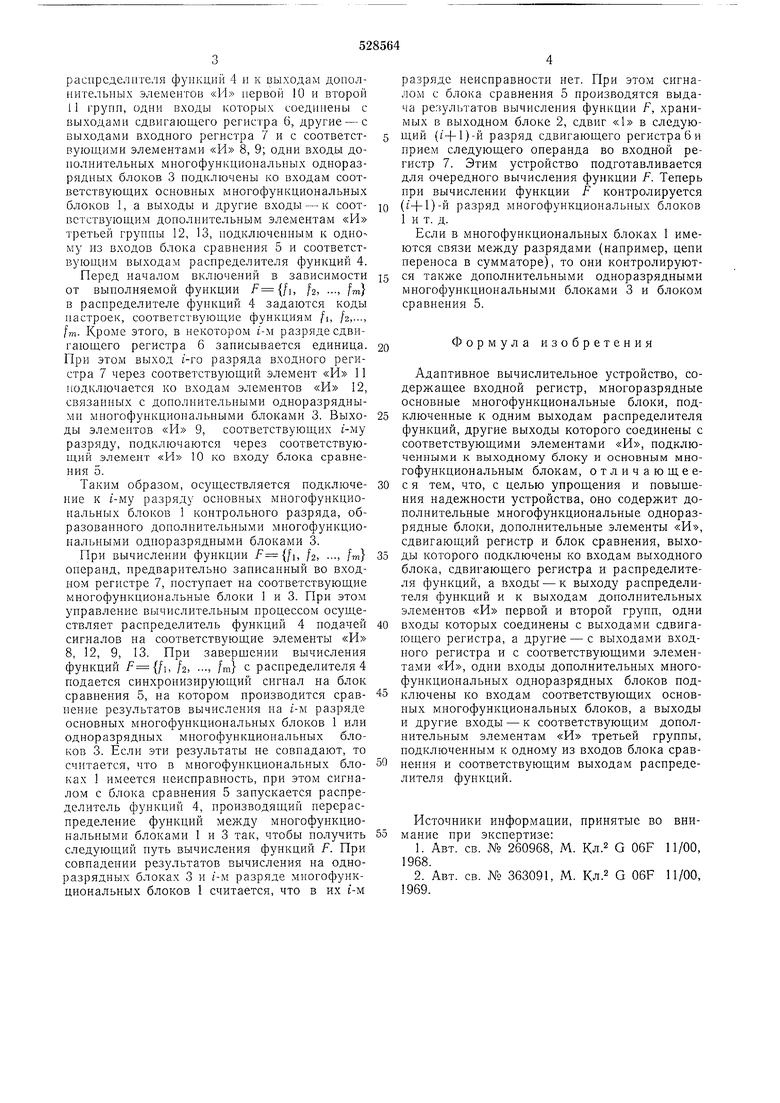

На чертеже представлена блок-схема предложенного устройства.

Оно содержит многоразрядные основные многофункциональные блоки 1, выходной блок 2, дополнительные одноразрядные многофун1сциональные блоки 3, распределитель функций 4, блок сравнения 5. сдвигающий регистр 6, входной регистр 7, основные элементы «И 8, 9, дополнительные элементы «И 10 первой группы, элементы 11 второй группы и элементы 12 и 13 третьей группы. Выходы блока сравнения 5 подключены ко входам вы.ходного блока 2, сдвигающего регистра 6 и распределителя функций 4, а его входы - к выходу

распределителя функций 4 и к выходам доиолнительиых элемеитов «И первой 10 и второй 11 груии, один входы которых соедииены с выходами сдвигающего регистра 6, другие - с выходами входиого регистра 7 и с соответствующими элементами «И 8, 9; одии входы дополнительных многофункциональных одноразрядных блоков 3 подключены ко входам соответствующих основных многофункциональных блоков 1, а выходы и другие входы - к соотвстствующим дополнительным элементам «И третьей группы 12, 13, подключенным к одному из входов блока сравнения 5 и соответствуюпи1м выходам распределителя функций 4.

Перед началом включений в зависимости от выполняемой функции , /2, ..., fm} в распределителе функций 4 задаются коды настроек, соответствующие функциям fi, /2,..., fm. Кроме этого, в некотором t-M разряде сдвигающего регистра 6 записывается единица. При этом выход t-ro разряда входного регистра 7 через соответствующий элемент «И 11 подключается ко входам элементов «И 12, связанных с дополнительными одноразрядными миогофункциональными блоками 3. Выходы элементов «И 9, соответствующих t-му разряду, подключаются через соответствующий элемент «И 10 ко входу блока сравнения 5.

Таким образом, осуществляется подключение к 1-му разряду основных многофункциональных блоков 1 контрольного разряда, образованного дoпOv нитeльными многофункциональными одноразрядными блоками 3.

При вычислении функции , /2, ..., f™} онеранд, предварительно записанный во входном регнстре 7, поступает на соответствующие многофункциональные блоки 1 и 3. При этом управление вычислительным процессом осуществляет распределитель функций 4 подачей сигналов на соответствующие элементы «И 8, 12, 9, 13. При заверщении вычисления функций , /2, ..., fm} с раснределителя 4 подается синхронизирующий сигнал на блок сравнения 5, на котором производится сравнение результатов вычисления на i-м разряде основных многофункциональных блоков 1 или одноразрядных многофункциональных блоков 3. Если эти результаты не совпадают, то считается, что в многофункциональных блоках 1 имеется неисправность, при этом сигналом с блока сравнения 5 запускается распределитель функций 4, производящий перераспределение функций между многофункциональными блоками 1 и 3 так, чтобы получить следующий путь вычисления функций Р. При совпадении результатов вычисления на одноразрядных блоках 3 и г-м разряде многофункциональных блоков 1 считается, что в их t-M

разряде неисправности нет. При этом сигналом с блока сравнения 5 производятся выдача результатов вычисления функции F, хранимых в выходном блоке 2, сдвиг «1 в следующий (1-|-1)-й разряд сдвигающего регистра 6 и прием следующего операнда во входной регистр 7. Этим устройство подготавливается для очередного вычисления функции F. Теперь при вычислении функции F контролируется (|:-|-1)-й разряд многофункциональных блоков 1 и т. д.

Если в многофункциональных блоках 1 имеются связи между разрядами (например, цепи переноса в сумматоре), то они контролируются также дополнительными одноразрядными многофункциональными блоками 3 и блоком сравнения 5.

Формула изобретения

Адаптивное вычислительное устройство, содержащее входной регистр, многоразрядные основные многофункциональные блоки, подключенные к одним выходам распределителя функций, другие выходы которого соединены с соответствующими элементами «И, подключенными к выходному блоку и основным многофункциональным блокам, отличающеес я тем, что, с целью упрощения и повышения надежности устройства, оно содержит дополнительные многофункциональные одноразрядные блоки, дополнительные элементы «И, сдвигающий регистр и блок сравнения, выходы которого нодключены ко входам выходного блока, сдвигающего регистра и распределителя функций, а входы - к выходу распределителя функций и к выходам дополнительных элементов «И первой и второй групп, одни входы которых соединены с выходами сдвигающего регистра, а другие - с выходами входного регистра и с соответствующими элементами «И, одни входы дополнительных многофункциональных одноразрядных блоков подключены ко входам соответствующих основных многофункциональных блоков, а выходы и другие входы - к соответствующим дополнительным элементам «И третьей группы, подключенным к одному из входов блока сравнения и соответствующим выходам распределителя функций.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. № 260968, М. Кл. G 06Е 11/00, 1968.

2.Авт. св. № 363091, М. Кл. G 06F 11/00, 1969.

IfllI

LiU....UU

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1991 |

|

RU2045769C1 |

| Адаптивное вычислительное устройство | 1974 |

|

SU529456A1 |

| ОДНОРОДНАЯ СТРУКТУРА | 1973 |

|

SU399848A1 |

| Устройство для вычисления показательно-степенной функции | 1980 |

|

SU920717A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

-9

« « 3 I

fij .

Авторы

Даты

1976-09-15—Публикация

1974-10-11—Подача