1

(61) 1444783 (21)4763201/24 (22)27.11.89 (46)23.11.91. Бюл. №43 (71) Рыбинский авиационный технологический институт

(72)И.З.Альтерман, М.А.Гладштейн, В.М.Комаров и Н.А.Шубин (53)681.3(088.8)

(56)Авторское свидетельство СССР Nfc 1444783, кл. G 06 F 11/28, 1987.

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРА

(57)Изобретение относится к вычислительной технике и может найти применение при

построении микропроцессорных устройств для повышения их надежности. Цель изобретения - расширение функциональных возможностей за счет контроля содержимого указателя стека микропроцессора при выполнении стековых команд. Устройство для контроля микропроцессора содержит счетчик 1, схему 2 сравнения, регистры 4 и 5, блок постоянной памяти 6, сумматор 7, мультиплексор 8, элементы И 3, 9 - 11, триггеры 13, 14 и элемент НЕ 12. В устройство введены дешифратор 15, регистры 16, 17, сумматор 18, схема сравнения. 19, счетчик 20, мультиплексор 21, блок задания 22 границы стека, .элементы И 23-25, элементы ИЛИ 27 - 29 и триггер 30. 1 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1817096A1 |

| Устройство для контроля микропроцессора | 1987 |

|

SU1444783A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Программируемый контроллер | 1986 |

|

SU1328815A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

г

31

(Л

С

о ю

00

о

ю

Изобретение относится к вычислительной технике и является усовершенствованием устройства по авт.св. № 1444783.

Цель изобретения - расширение функциональных возможностей за счет контроля содержимого указателя стека микропроцессора при выполнении стековых команд.

На-чертеже изображена структурная схема устройства.

Устройство для контроля микропроцессорной системы содержит первый счетчик 1, первую схему 2 сравнения и первый 3 элемент И, первый 4 и второй 5 регистры, блок 6 постоянной памяти, первый сумматор 7, первый мультиплексор 8, второй 9, третий 10 и четвертый 11 элементы И, элемент НЕ 12, первый 13 и второй 14 триггеры, дешифратор 15, третий 16 и четвертый 17 регистры, второй сумматор 18, вторую схему 19 сравнения, второй счетчик 20, второй мультиплексор 21, блока 22 задания границы стека, пятый элемент И 23, шестой 24 и седьмой 25 элементы И, контролируемый микропроцессор 26, первый 27, второй 28 и третий 29 элементы ИЛИ и третий триггер 30, выход 31 неисправности устройства.

Устройство- работает следующим образом.

После включения питания в схеме контролируемого микропроцессора 26 формируется сигнал сброса RESET, который через шину управления поступает на входы сброса первого счетчика 1, второго регистра 5 и триггеров 13, 14 и 30, что приводит к их установке в нулевое состояние. Одновременно счетчик команд микропроцессора 26 также устанавливается в нулевое состояние. Затем микропроцессор 26 начинает последовательную выборку и исполнение команд по заданной программе. Для микропроцессора КР580 последние могут быть однобайтными, двухбайтными и трех- байтными. В результате этого адрес следующей команды может быть больше адреса предыдущей команды соответственно на одну, две или три единицы младшего разряда при условии правильного функционирования микропроцессора. Кроме того, в системе команд микропроцессора имеются команды переходов, которые могут скачком изменять содержимое счетчика команд микропроцессора.

Момент считывания первого байта команды легко идентифицируется по совпадению сигналов на линиях выборки первого байта команды (М1) и чтения памяти (MEMR), шины управления микропроцессора 26. В этот момент срабатывает третий элемент И 10 и код первого байта команды, установленный в это время на шине данных

фиксируется в первом регистре 4. Этот байт поступает на адресные входы блока 6 постоянной памяти, в результате чего на его основном выходе будет установлен код,

равный количеству байт в команде, а на дополнительном выходе - код типа команд (операционная команда - команда перехода).

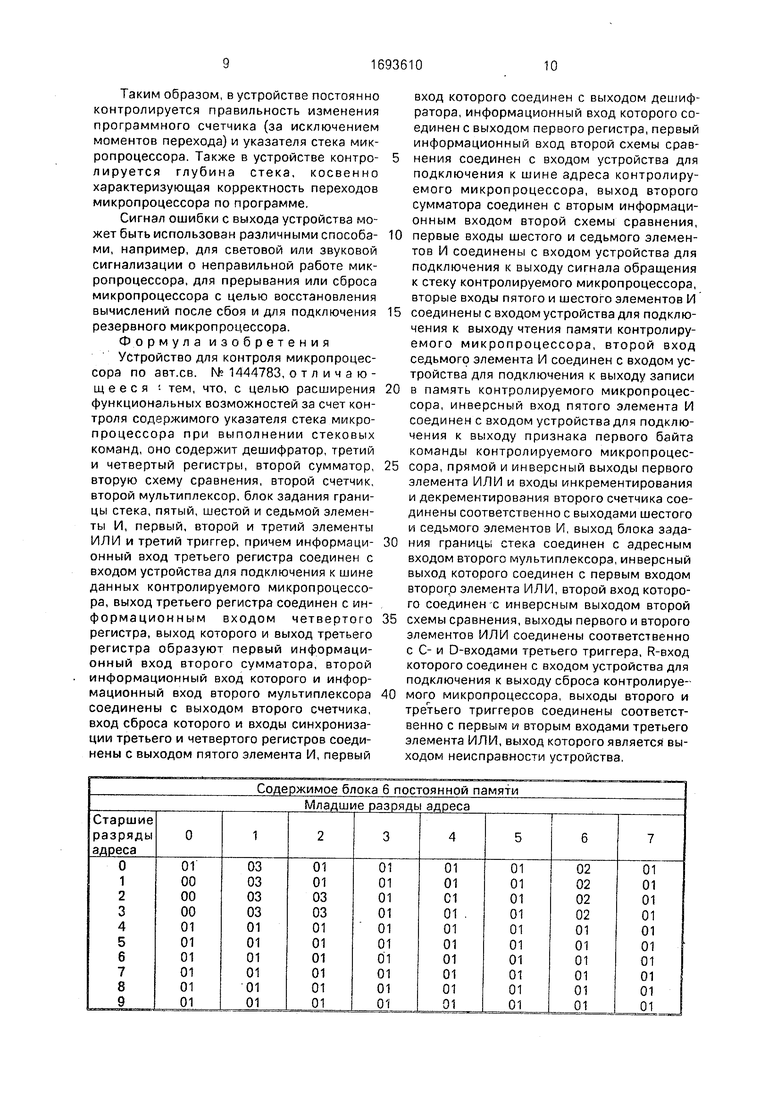

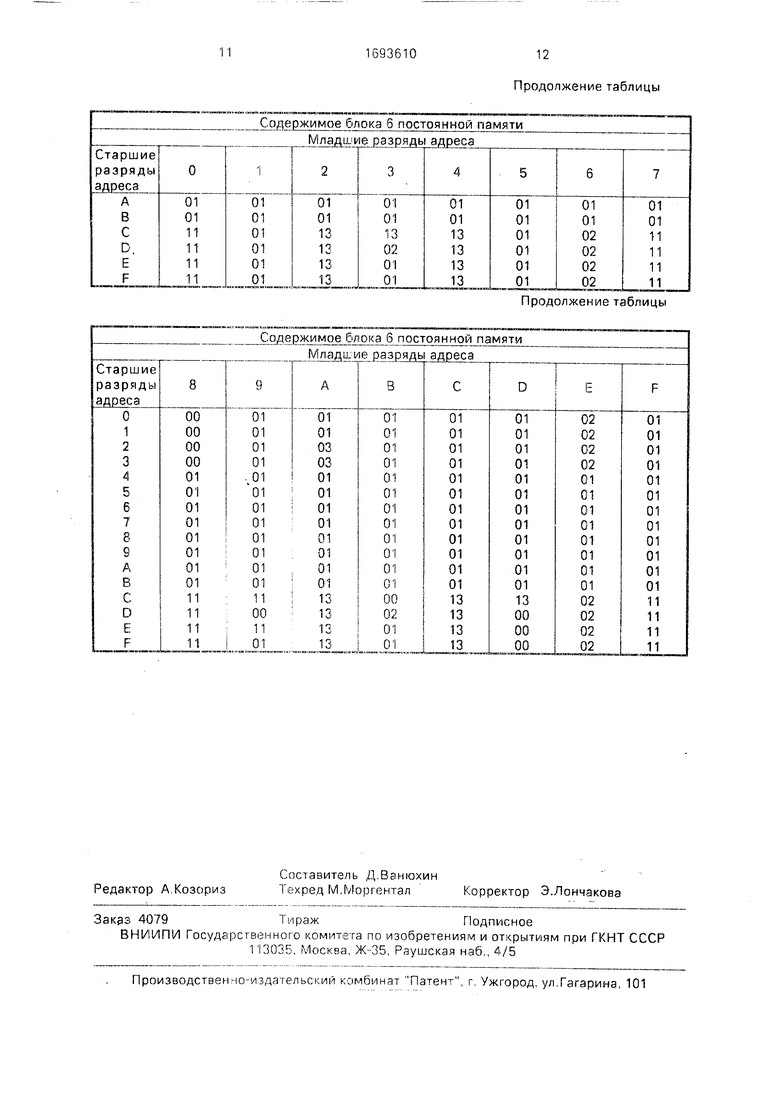

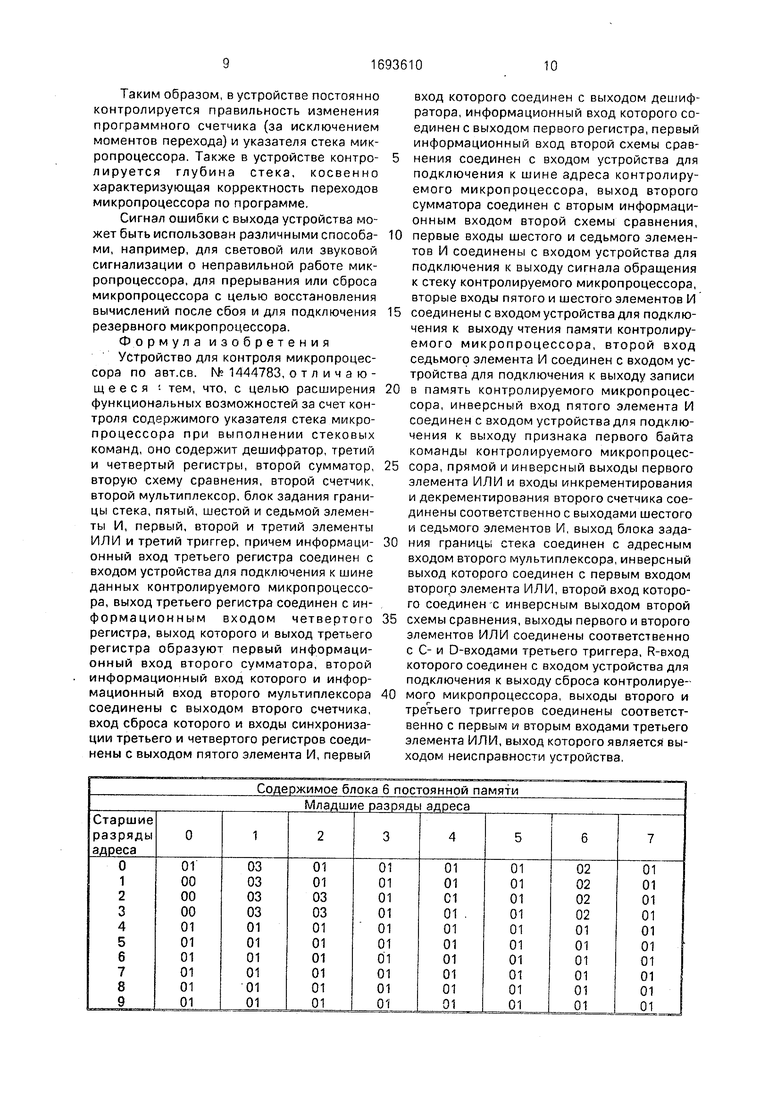

В частности, для контроля микро0 процессора серии КР580 коды, хранимые данные в блбке 6 постоянной памяти, должны соответствовать данным, приведенным в табл.1. Каждая клеточка этой таблицы соответствует одному из 256 воз5 можных адресов. Код в каждой клетке состоит из двух цифр. Правая цифра соответствует десятиричному эквиваленту двоичного кода, формируемого на основном выходе блока 6 постоянной памяти и

0 равна количеству байт (1,2 или 3) команды микропроцессора. Левая цифра соответствует состоянию дополнительного выхода блока 6 постоянной памяти и равна единице, если адресный байт соответствует ко5 манде перехода, в противном случае равна нулю.

Таким образом, на выходах блока 6 постоянной памяти непосредственно после момента фиксации первого байта очеред0 ной команды в первом регистре 4 будет установлен код в соответствии с данными таблицы.

В результате возможны две ситуации: очередная команда не является командой

5 перехода; очередная команда - команда перехода.

В первом случае на вход D первого триггера 13 поступает сигнал логического О, и по окончании сигнала с выхода третьего эле0 мента И 10 первый триггер 13 не изменяет своего состояния. Код байтности очередной команды с основного выхода блока 6 постоянной памяти поступает на первый вход сумматора 7, а на второй его вход через

5 первый мультиплексор 8 поступает код из второго регистра 5.

По этим данным первый сумматор 7 формирует сумму и перенос (для микропроцессора КР580 мультиплексор 8, сумматор 7

0 и регистр 5 содержат по два двоичных разряда, так как двоичный код байтности может быть только 01,10 или 11). Сумма поступает на вход второго регистра 5 и записывается в него по заднему фронту сигнала с выхода

5 третьего элемента И 10 благодаря элементу НЕ 12. Сигнал с выхода последнего проходит также на вход инкрементирования первого счетчика 1 через второй элемент И 9г если значение переноса на выходе первого сумматора 7 равно логической 1.

Таким образом в первом счетчике 1 (старшие разряды) и во втором регистре 5 (младшие разряды) формируется ожидаемый код адреса первого байта следующей команды, Этот код поступает на вход первой схемы 2 сравнения. В момент извлечения первого байта следующей команды микропроцессор 26 формирует ее адрес на шине адреса и сигналы М1 и MEMR на шине управления.

Если микропроцессор работает без сбоев, то выданный адрес совпадает с ожидаемым адресом, поступающим из первого счетчика 1 и второго регистра 5. В этом случае на инвертирующем выходе первой схемы 2 сравнения устанавливается нулевой потенциал, что обеспечивает пассивный логический уровень на выходе первого элемента И 3.

Если же имеет место сбой, то адреса будут неравны, на выходе первой схемы 2 сравнения появляется сигнал логической единицы. Совпадение этого сигнала с активным сигналом с инверсного выхода первого триггера 13 и сигналом с выхода третьего элемента И 10 вызывает срабатывание первого элемента И 3, установку второго триггера 14 и появление на выходе третьего элемента ИЛИ 29, т.е. на выходе 31 устройства, активного сигнала, свидетельствующего о неправильной работе микропроцессора.

Если же очередная команда - команда перехода, то на дополнительном выходе блока 6 постоянной памяти будет установлен единичный сигнал. В результате по заднему фронту сигнала с выхода третьего элемента И 10, благодаря элементу НЕ 12, первый триггер 13 переходит в единичное состояние. Сигнал с его инверсного выхода блокирует контроль совпадения адресов при извлечении следующей команды с помощью первого элемента И 3. Кроме того, происходит переключение первого мультиплексора 8 и он подключает к второму входу первого сумматора 7 младшие разряды шины адреса контролируемого микропроцессора.

Таким образом, при извлечении первого байта команды следующий за командой перехода контроль не проводится, а ее адрес плюс байтность команды (ожидаемый адрес следующей команды) фиксируется в первом счетчике t и втором регистре 5. Фиксация старших разрядов адреса в счетчике 1 производится сигналом с выхода четвертого элемента И 11, работа которого разрешается единичным сигналом с выхода триггера 13,

Запись младших разрядов, представляющих собой сумму младших разрядов адреса очередной команды с ее байтностью с выхода первого сумматора во второй регистр 5, а также учет переноса с выхода сумматора 7 в счетчик 1 происходит совер- 5 шенно аналогично первому случаю. Кроме того, по окончании считывания команды, следующей за командой перехода (если она. конечно, сама не является командой перехода), происходит возврат первого триггера

0 13 в состояние логического О и, следовательно, восстанавливается режим контроля. Контроль за изменением программного счетчика при выполнении команд перехода

5 проводится в устройстве на основе контроля содержимого указателя стека микропроцессора. При сбое программного счетчика при выполнении команд перехода происходит выполнение ложного потока команд, в

0 результате чего указатель стека выходит за допустимые границы, которые заранее могут быть определены программистом.

Кроме того, возможный сбой указателя стека микропроцессора сам становится

5 причиной неправильной установки программного счетчика, не обнаруживаемой описанной частью устройства.

Для контроля за поведением указателя стека микропроцессора 2 дешифратор 15

0 настраивается на селекцию только одной команды - Загрузка указателя стека. В системе команд микропроцессора КР580 этой командой является команда LXf SP, D16. Когда в первом регистре 4 фиксируется

5 код этой команды, единичный сигнал с выхода дешифратора разрешает работу пятого элемента И 23. В результате в следующих циклах выполнения этой команды по сигналу MEMR на шине управления производится

0 запись в регистры 16 и 17 данных, адресующих вершину стека.

Эти же данные фиксируются в указателе стека микропроцессора 26. Одновременно с записью данных в регистры 16 и 17 по сиг5 налу с выхода пятого элемента И 23 производится очистка второго счетчика 20. Данные о вершине стека с выходов регистров 16 и 17 постоянно присутствуют на первом входе второго сумматора 18. На второй

0 вход сумматора 18 поступает код с выхода счетчика 20, являющийся текущим смещением указателя стека микропроцессора 26 или, иначе, индексом относительно вершины стека.

5 Разрядность счетчика 20 в общем случае определяется разрядностью адреса, поступающего на первый вход сумматора 18. Однако разрядность счетчика 20 может быть существенно уменьшена с учетом выполнения реальных программ В этих случаях старшие разряды второго входа сумматора

18 должны быть подключены к потенциалу Лог.1, так как сумматор 18 реализует функцию вычитания вершины стека и индекса, т.е. для корректного отслеживания указателя стека микропроцессора индекс должен быть установлен на втором входе сумматора 18 в дополнительном коде.

В момент обращения к стеку микропроцессора 26 формируется сигнал STACK на шине управления, который разблокирует элементы И 24 и 25. При реализации цикла Запись в стек сигнал микропроцессора MEMW с шины управления через элемент И 25 поступает на вход декрементирования второго счетчика 20, в результате чего его состояние уменьшается на единицу, и код на выходе сумматора 18 также уменьшается на единицу. Таким образом, на выходе сумматора 18 формируется ожидаемый код указателя стека микропроцессора 26. Этот код поступает на вход второй схемы 19 сравнения.

Если микропроцессор 26 работает без сбоев, то выданный адрес ячейки стека совпадает с ожидаемым адресом, поступающим из сумматора 18. В этом случае на инвертирующем выходе второй схемы 19 сравнения устанавливается нулевой потенциал, что обеспечивает пассивный логический уровень на входе второго элемента ИЛИ 28.

Если же имеет место сбой указателя стека, то адреса не равны, на выходе второй схемы 19 сравнения появляется сигнал логической 1 которыйчерезэлементИЛИ28 проходит на вход третьего триггера 30. Установка его в единичное состояние произойдет в момент среза сигнала MEMW, который через инверсный вход первого элемента ИЛИ 27 поступает на синхровход третьего триггера 30. Единичный сигнал с триггера 30 поступает через третий элемент ИЛИ 29 на выход устройства 31 и свидетельствует о неправильной работе микропроцессора 26.

Таким образом, после реализации цикла записи информации в стек на выходе второго сумматора 18 всегда устанавливается адрес последней заполненной ячейки стека. Этот же адрес фиксируется в указателе стека микропроцессора 26 по окончании выполнения стековой команды.

Если сбои указателя стека микропроцессора 26 не имеют место, то в цикле Чтение из стека микропроцессор 26 выдает на шину адреса адрес ячейки стека, соответствующий адресу на выходе сумматора 18. Тогда на инвертирующем выходе второй схемы 19 сравнения устанавливается нулевой потенциал, свидетельствующий о равенстве адресов на ее входах. Результат сравнения адресов фиксируется в третьем триггере 30 по фронту синхросигнала, поступающего на соответствующий вход триггера 30 через элементы И 24 и ИЛИ 27 в момент совпадения сигналов STACK и MEMR на шине управления микропроцессора 26.

Одновременно этот же сигнал, поступая

0 на вход инкрементирования счетчика 20, увеличивает на единицу индекс на его выходе, соответственно увеличивая на единицу индекс на его выходе, соответственно увеличивая на единицу адрес на выходе сумма5 тора 18. Это полностью согласуется с действиями микропроцессора 26, который по окончании каждого цикла Чтение из стека увеличивает содержимое указателя стека на единицу.

0 В случае сбоя указателя стека микропроцессора 26 фиксация сигнала ошибки на выходе 31 устройства при выполнении цикла Чтение из стека производится аналогично.

5 Для контроля глубины стека, нарушаемой вследствие ложных переходов программного счетчика микропроцессора 26, второй мультиплексор 21 производит сопоставление индекса на выходе счетчика 20 с кодом,

0 установленным в блоке 22 задания. Двоичный коде выхода блока 22 задания подключает на инвертирующий выход мультиплексора 21 соответствующий разряд с выхода счетчика 20. Данный разряд выбирается пользовате5 лем с помощью блока 22 задания в качестве границы стека, исходя из программы, выполняемой микропроцессором. Например, если глубина стека равна 64 ячейкам памяти, то в качестве контрольного выбирается 6

0-7 разряд счетчика 20. Появление на нем сигнала логического О в момент реализации стековой программы будет свидетельст- вовать о переполнении стека, т.е. о нарушении выбранной глубины.

5 В результате на инверсном выходе мультиплексора 21 появляется единичный сигнал, который через элемент ИЛИ 28 поступает на D-вход триггера 30 и вызывает его установку. Единичный сигнал с выхода

0 триггера 30 через элемент ИЛИ 29 поступает на выход ошибки 31 устройства, свидетельствуя тем самым о нарушении правильного функционирования микропроцессора 26.

5 Если микропроцессор 26 работает без сбоев, то при реализации обращения к стеку на выбранном входе мультиплексора 21 всегда присутствует сигнал логической 1. который не может перевести триггер 30 в активное состояние.

Таким образом, в устройстве постоянно контролируется правильность изменения программного счетчика (за исключением моментов перехода) и указателя стека микропроцессора. Также в устройстве контро- лируется глубина стека, косвенно характеризующая корректность переходов микропроцессора по программе.

Сигнал ошибки с выхода устройства может быть использован различными способа- ми, например, для световой или звуковой сигнализации о неправильной работе микропроцессора, для прерывания или сброса микропроцессора с целью восстановления вычислений после сбоя и для подключения резервного микропроцессора.

Формула изобретения

Устройство для контроля микропроцессора по авт.св. № 1444783, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля содержимого указателя стека микропроцессора при выполнении стековых команд, оно содержит дешифратор, третий и четвертый регистры, второй сумматор, вторую схему сравнения, второй счетчик, второй мультиплексор, блок задания границы стека, пятый, шестой и седьмой элементы И, первый, второй и третий элементы ИЛИ и третий триггер, причем информаци- онный вход третьего регистра соединен с входом устройства для подключения к шине данных контролируемого микропроцессора, выход третьего регистра соединен с информационным входом четвертого регистра, выход которого и выход третьего регистра образуют первый информационный вход второго сумматора, второй информационный вход которого и информационный вход второго мультиплексора соединены с выходом второго счетчика, вход сброса которого и входы синхронизации третьего и четвертого регистров соединены с выходом пятого элемента И, первый

вход которого соединен с выходом дешифратора, информационный вход которого соединен с выходом первого регистра, первый информационный вход второй схемы сравнения соединен с входом устройства для подключения к шине адреса контролируемого микропроцессора, выход второго сумматора соединен с вторым информационным входом второй схемы сравнения, первые входы шестого и седьмого элементов И соединены с входом устройства для подключения к выходу сигнала обращения к стеку контролируемого микропроцессора, вторые входы пятого и шестого элементов И соединены с входом устройства для подключения к выходу чтения памяти контролируемого микропроцессора, второй вход седьмого элемента И соединен с входом устройства для подключения к выходу записи в память контролируемого микропроцессора, инверсный вход пятого элемента И соединен с входом устройства для подключения к выходу признака первого байта команды контролируемого микропроцессора, прямой и инверсный выходы первого элемента ИЛИ и входы инкрементирования и декрементирования второго счетчика соединены соответственно с выходами шестого и седьмого элементов И, выход блока задания границы стека соединен с адресным входом второго мультиплексора, инверсный выход которого соединен с первым входом второг.о элемента ИЛИ, второй вход которого соединен-с инверсным выходом второй схемы сравнения, выходы первого и второго элементов ИЛИ соединены соответственно с С- и D-входами третьего триггера, R-вход которого соединен с входом устройства для подключения к выходу сброса контролируемого микропроцессора, выходы второго и третьего триггеров соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого является выходом неисправности устройства.

Продолжение таблицы

Продолжение таблицы

Авторы

Даты

1991-11-23—Публикация

1989-11-27—Подача