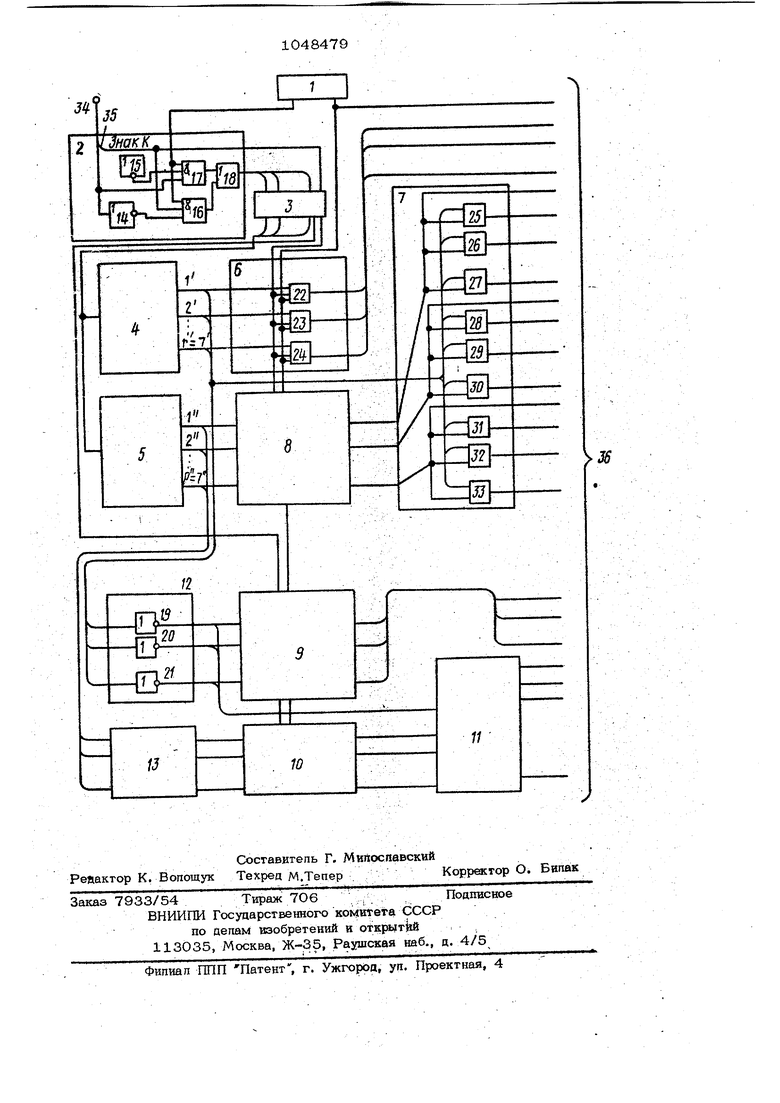

Изобретение относится к вычиспитёпьной технике, в частности к специапизированным вычислитепьным устройствам, и . может быть использовано для вычисления значений фаз излучателей антенной решетки при симметричном фазовом распределении. Известно устройство, содержащее регистр, вход которого является входом устройства, и блок сумматоров, выходы которого являются выходами устройства, два блока умножения, элемент НЕ, два логических коммутатора, кажаь й из когорых содержит две группы элементов И iio 1 элементов И в каждой группе и по ( i -1) элементов ИЛИ, причем выходы регистра через первый и второй блоки умножения соединены с первыми входами элементов И первой и второй rpyim каждого логического коммутатора, вторые входы элементов И первой группы каждого логического коммутатора объединены и и соединены со знаковым выходом регист ра и входом элемента НЕ, выход которого соединен с вторыми входами элементов И второй группы каждого логического коммутатора, выходы ( ( -1 )-го элемента И второй группы каждого логического . коммутатора соединены с первыми входа ми соответствующих элементов ИЛИ того же логического коммутатора, выходы i -1, i -2,... 2, 1 элементов И первой группы каждого логического коммутатора соединены с вторыми входами 1, 2, .... 1-2, i -1 элементов ИЛИ того же логического коммутатора, выходы i -х элементов И первой и второй групп и элементов ИЛИ каждого логического коммутатора соединены с соответствующими входами блока сумматоров ll . Недостатком данного устройства является то, что для формирования управляющих кодов фазовращателей одной половины решетки и симметрично - расположенны .фазовращателей другой половины используются аналогичные схемы, содержащие множительные и суммирующие блоки. Это ведет к избыточным аппаратурным затратам. Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее входной регистр, информационные выходы которого через первый и второй множительные блоки и логические коммутаторы соединены с входами первого сум .мирующего блока, выходы которого подключены ко входам второго и третьего суммирующих блоков, управляющие входы которых соединены с управляющим выходом входного регистра, а выходы - через блок инверторов с входами четвертого, пятого и шесто1Ч) суммирующих блоков, при этом выходы второго, третьего, четвертого, пятого и шестого суммирзпющих блоков являются информационными выходами устройства 2, Однако установка блока инверторов для каждого расположенного симметрично относительно центра решетки фазовращателя, Т.е. для половины решетки, требует дополнительных аппаратурных затрат, особенно при использовании симметрии в решетках с эфирным распределением СВЧ-энергии между излучателями, а также при вычислении управляющих кодов по координате в плоской и цилиндрической антенных решетках с фидерным питанием. -Кроме того, устройство имеет невысокое быстро действие, поскольку все блоки, формирующие управляющие коды для антенной решетки, включены последовательно. Цель изобретения- упрощение и повышение быстродействия устройства. Поставленная цель достигается тем, Что в устройстве, содержащем формирователь прямого И-инверсного кодов, инфор мационные входы которогхэ представляют собой информационные входы устройства, первый управляющий вход представляет собой управляющий вход устройства и соединен с входом знакового разряда регистра, второй управляющий вход соединен с первым выходом блока управления, а информационные выходы - с информационными входами регистра, инфбрмационные выходь; которого соединены соответственно с входами первого и второго множите льнытс блоков, Щ)И этом выходы первого и второго множительных блоков соединены соответственно с объединенными первыми входами первого и второго сум- мирующих блоков и первыми входами третьего суммирующего блока, причем управляющие входы первого и третьего суммирующих блоков соединены с вторым выходом блока управления и представляют собой первый информационный выход устройства, первый и второй блоки инвер торов; выходы которых соединены соответственно с входами четвертого и пятого суммирующих блоков, управляющие входы котор 1х соединены с вторым выходом блока управления, и шестой суммирующий блок, при этом выходы всех суммирующих блоков представляютсобой последующие информационные выходы устройства, причем выходы третьего суммирующего бпока соединены соответсТвеннЬ с вторыми входами второго суммирующего бпока, выходы первого и второго множительных блоков соединены соответственно с входами первого и второго блоков инверторов, выходы первого блока инверторов и пятого суммирующего бпока соединены соответственно с первыми и вторыми входами шестого суммирующего бпока причем допопнитепьныё управляющие входы четвертсчго и пятого суммирующих бло ков додкпючены к инверсному выходу знаково1ч разряда регистра, прямой выход знакового разряда которого соединен с допопнитепьными управгшющими входами первого и третьего суммирующих блоков. На чертеже представлена функциональная схема устройства для числа рядов фазовращатепей М-127. Схема содержит блок 1 управления, формирователь 2 прямого и инверсного кодов, регистр 3, первый и второй множитепьные бгюки 4 и 5, первый, второй, третий, четвертый, пятый и шестой суммирующие блоки 6-11, первый и второй блоки 12 и 13 инверторов, инверторы 14 и 15, ключевые схемы 16 и 17, схемы ИЛИ 18, инверторы 19-2Г йш аллельные сумматоры 22-33. Величина К знак К набега фазы на расстоянии между излучателями по координате поступают соответственно на информационный и управляющий входы 34 и 35 устройства. Формирователь 2 прямого и инверсного кодов обеспечивает запись прямого или инверсного значения величины набега фазы в регистр 3 в зависимости от знака К набега фазы. Выходы регистра 3 сое- динены с входами первого и второго множительных блоков 4 и 5, выполняющих соответственно умножение входных величин на числа 1, 2, ... г и (г +1), 2(ч-1),...р (i н-1). С выходов 1, 2 ... Г первого множительного бпока 4, где соответственно формируются значения произведений входной величины на числа 1, 2, ...Г , информация поступает на первые входы и второго суммирующих блоков 6 и 7 (соответственно на тервые входы сукыаторов 22-24 и 25-33) G выходов 1,2 ,... р второго множительного блока 5, где.соответствевно формируются значения произведений вход.ной величины на числа (t +1), 2(+1),. р(Р+1), информация поступает на.первые входы третьего суммирующего блока 8, аналогичного по структуре первому суммирующему блоку 6. С выходов третьего суммирующего блока 8 информация поступает соответственно на вторые входы второго суммирующего блока 7 (на . вторые входы сумматоров 25-33). Кроме этого, значения произведений с выходов первого и второго множительных блоков 4 и 5 поступают на входы первого и второго блоков 12 и 13 инверторов, содержащих инверторы 19-21. Выходы первого и второго блоков 12 и 13 инверторов соединены соответственно с первыми входами четвертого и пятого суммирующих блоков 9 и 1О, причем выходы первого блока 12 инверторов соединены также с первыми входами шестого суммирующего блока 11, а выходы пятого суммирующего блока 10 подключены ко вторым входам ш стогю суммирующего-блока. 11, аналогично по структуре второму .гуммирующему блоку 7. При этом структура четвертого и пятого суммирующих блоков 9 и 10 аналогична структуре первого суммирующего бпока 6. Управляющие входы, первого, третьего, четвертого и пятого суммирующих блоков 6, 8, 9 и 10 (соответственно вторые входы сумматоров; 22-24) соединены с вторым выходом блока 1 управления, дополнительные управляющие входы первого и третьего суммирующих блоков 6 И 8 (соответственно третьи.входы сумматоров 22-24) соединены с прямым выходом знакового разряда регистра 3, а дополнительные управляющие входы четвертого и пятого суммирующих блоков 9 и 10 - с инверсным вы ходом знакового разряда регистра 3. ёторой выход лока 1 управления и выходы всех суммирующих блоков 6-11 представляют собой информационные выходы 36. Вычислитель фаз для антенной решетки работает следующим образом. По сигналу Пуск с блока 1 управления прямое или инверсное значение К набега фазы на расстоянии между излучателями (в зависимости от знака К ) с информационных выходов формирователя 2 прямого и инверсного кодов поступает на информационные входы регистра 3, а с ёгю информационных выходов - на входы первого и второго множительных блоков 4 и 5, в которых выполняется соответственно умножение на числа 1,2,...7 и 8, 16, 24, 32, 40, 48, 56 (для М-127). Произведения входной величины ka эти числа вырабатываются на выходах l, 2 , ... первого множительного 5.10 блока 4 и выходах 1, 2,... р второго множительного блока 5. Во всем устройстве принята нумерация разрядов со старших, причем 1-й разряд соответствует набегу фазы 1 , 2-й разряз - 1)/2, Е -и разряд - и т.д. С выходов 1, 2, ... г первого множительного блока 4 чвсла поступают на первые входы сумматоров 22-24 первого суммируюшего блока 6. На вторые и третьи входы сумматоров 22-24 этого суммирующего бпока поступают соответствен с блока 1 управления в (6+1 )-й разряд логическая единица для округления, а с прямого выхода знакового разряда регист ра 3 при в (В +2) разряд - логическая единица цпя формирования обратного кода. Таким образом, сумматоры 22-24 первого сумм1фу1рщего бпока 6 выполняю ДЕе функции: округление с точностью до попо2И й.: дискрета фазовращателя, что повышает точность установки луча, и обе печивают получение дополнительных кодов из обратных. С выходов 1, 2 , ... г первого множительного бпока 4 числа поступают также на первые входы сумматоров 2533 второго суммирующего блока 7. С выходов второго множительного блока 5 числа 8К , 16К , 24К , 32Х , 40К , 48К , 56К поступают на первые входы cyi nviaTopoB третьего суммирующего блока 8. Третий суммирующий блок 8 анало гичен блоку 6, и в нем, как и в блоке 6 выполняются две функции: округления и добавления единицы в разряд, соответствующий младшему разряду выходного кода вычислителя фаз для антенной реше ки. Выходы третьего суммирующего бпока 8 соедииены с вторыми входами сумг мирующего блока 8 с вторыми входами сумматоров 25-33 второго суммирук щего блока 7 обеспечивает выполнение операции округления и добавления- единицы в разряд, соответствующий младшему разряду выходного кода устройства, для большей части рядов фазовращателей. Посжольку разрядность чисел, тюступакхщих с блоков 4 и 8 на входы сумматоров 25-33 блока 7, различная, при операциях с отрицательными числами недостающие младщие разряды должны за I полняться единицами, для чего соответ79ствующие входы сумматоров в подключаются к прямому выходу знакового разряда регистра 3. Числа с выходов Г , 2, ... р и 1 „ 2,...р первого и второго множительных блоков 4 и 5 соответственно поступают на входы инверторов 19-21 первого и второго блоков 12 и 13 инверторов. Числа с выходов инверторов 1921 первого блока 12 инверторов поступают на первые входы сумматоров 2533 шестого суммирующего блока 11. На вторые входы сумматоров ;25-33 шестого суммирующего блока, 11 посту пают числа с выходов сумматоров пятого суммирующего блока 1О. На вторые и третьи входы сумматоров, расположенных в блоках 9 и 1О, поступают соответственно в (6 +1 )-й разряд с блока 1 управления логическая единица для округления, а в ( С +2)-й разряд - с инверсHoro выхода знакового разряда регистра 3 при К О логическая единица для форн мирования дополнительного кода. Поскольку разрядность чисел, поступающих с блоков 12 и 10 на входы сумматоров шестого суммирующего блока 11, различная, при операциях с отрицательнь}ми числами недостающие младшие разряды должны заполняться.единицами, для.чего соо ветствующие входы сумматоров 2224 четвертого и пятого суммирующих блоков 9 и 10 и подключаются к инверсному выходу знакового разряда регистра 3. Предложенное устройство обеспечивает изменение знака направления луча относительно нормали к решетке заменой . входного кода на обратный. Оно содержит меньшее количество оборудования, чем известное (например, 14 инверторов против 63 в прототипе). Кроме того, устройство обладает более высоким быстродействием, так как в нем выходные блоки 6 работают одновременно (в известном последовательно), а операция суммирова ния единицы в младшем разряде для получения дополнительного кода при k О выполняется один раз (в известием дважды: при вычислении управляющих кодов фазовращателей половины решетки и при получении дополнительных кодов длясимметрично расположенных фазовращатепей)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления координат антенной решетки | 1980 |

|

SU999059A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Функциональный генератор | 1979 |

|

SU781839A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

ВЫЧИСЛИТЕЛЬ ФАЗ ДЛЯ АНТЕННОЙ РЕШЕТКИ, содержащий формирователь прямого и икверс-ного кодов, информационные входы которого представляют собой информационные входы устройства, первый управляющий вход представляет собой управляющий вход устройства и соединен с входом знакового разряда регистра,, второй управляющий вход соединен с первым выходом блока управления, а информационные выходы с информационными входами регистра, информационные выходы которого соед нены с входами первого и второго множнтепьных блоков соответственно, при этом выходы первого и второго множительных блоков соединены соответственно с объединенными первыми входами первого и второго суммирующих блоков и . первыми входами третьего суммируклцего блока, причем управляющие входы первого и третьего суммирующих блоков соединены с вторым выходом блока упра& ления и представляют собой первый и формационный выход устройства, первый и второй блоки инверторов, выходы которых соединены соответственно с входами четвертого и пятого суммирующих блоков, управляющие входы которых соединены с вторым выходом блока управления, и шестой суммирующий блок, при этом выходы всех суммирующих блоков представляют собой последующие информационные выходы устройства, отличающийся тем, что, с цепью упроi щения и повыщения быстродействия устройства, выходы третьего суммирую О) щего блока соединены соответственно с вторыми входами второго суммирующего блока, выходы первого и второго множительных блоков соединены соответстве но с входами первого и второго блоков инверторов, выходы первого блока инверторов и пятого суммирующего блока - соединены соответственно с первыми и вторыми ькоаами шестого суммирующего 4 блока, причем дополнительные управляк 00 щне входы четвертого и пятого суммиру Nfiih ющих блоков подключены к инверсному vl выходу знаковогоразряда регистра, мой вь1 ход знакового разряда которого соединен с дополнитегаьными управляющими входами первого и третьего суммирующих блоков.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

Авторы

Даты

1983-10-15—Публикация

1979-02-28—Подача