Изобретение относится к вычисли- , тельной технике и может быть использовано в качестве специализированного вычислителя, предназначенного для оценки параметров сигнала.

Цель изобретен14я - повьппение точности устройства усреднения, функционирующего в условиях априбрной неопределенности относительно статистических характеристик входных измерений.

С этой целью в устройство вводятся элементы цифровой вычислительной техники, обеспечивающие взвешенное суммирование входных измерений в соответствии с алгоритмом / .

(X()

(Х{| ,. |Х|-( а а, а IX j I Ь

-С-/Х/

Ь а, Ь(х(

L О, , ,2,,..,n где у; - цифровые сигналы, поступающие в сумматор;

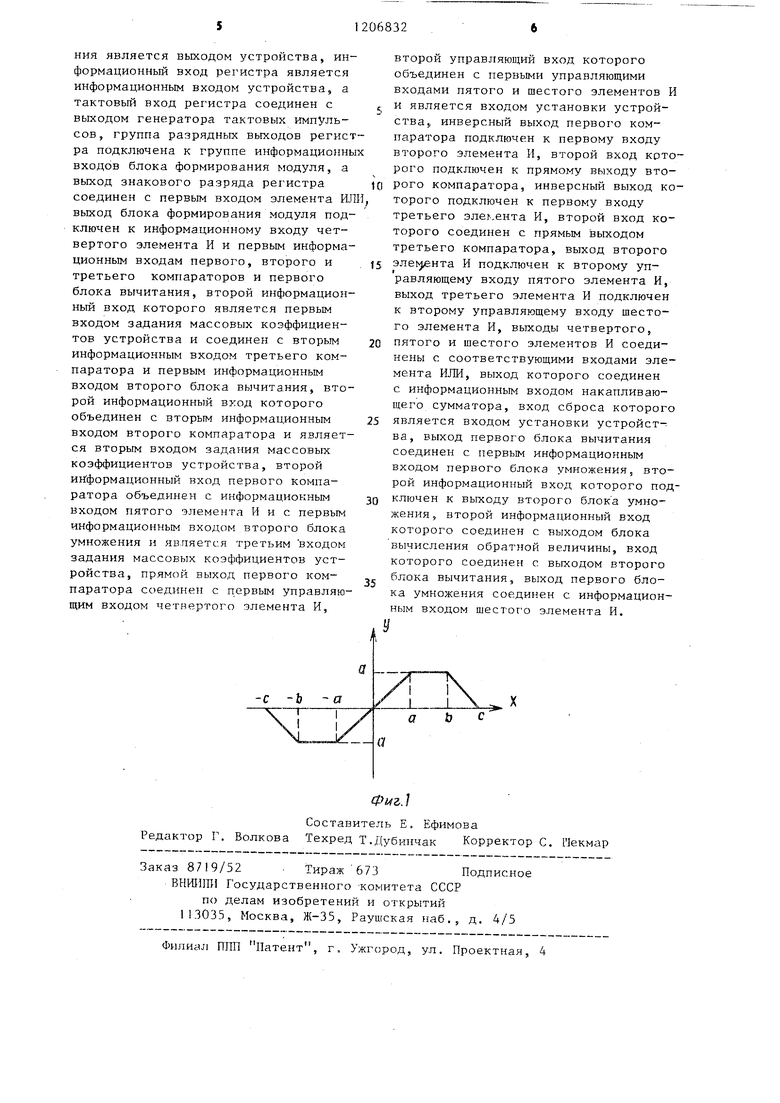

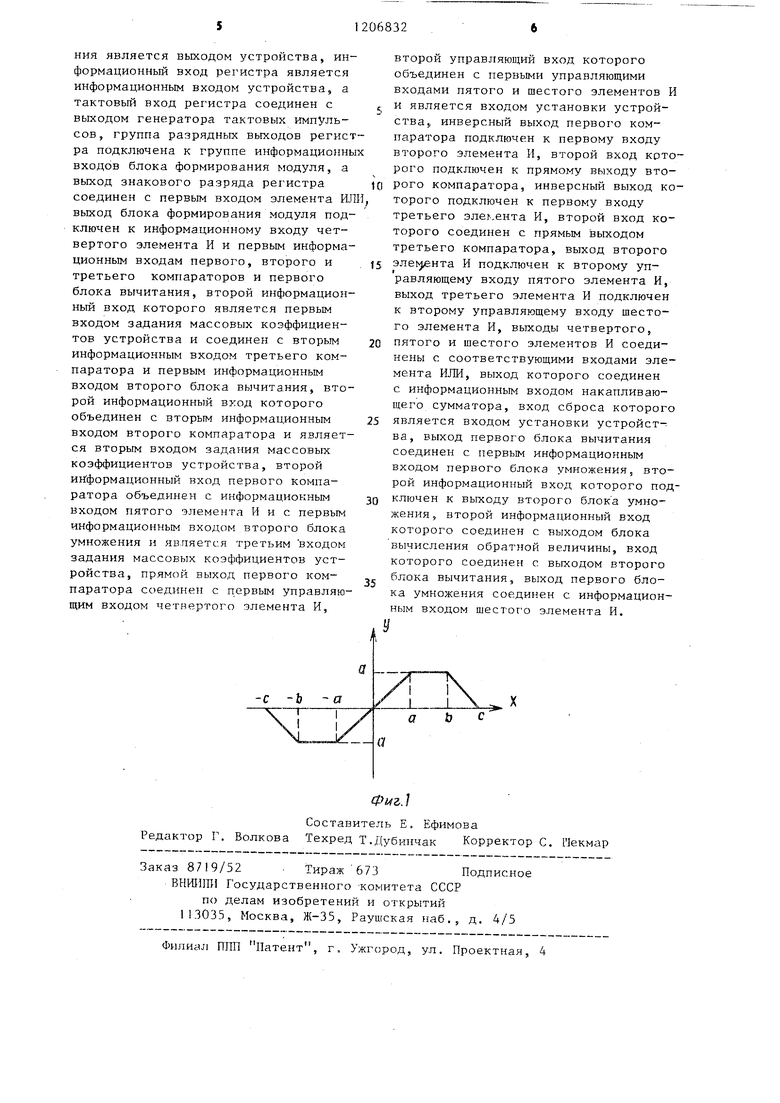

|аК|Ь| |сГ априорно заданные константы. На фиг. геометрически представлено соотношение (х); на фиг. 2 - структурная схема устройства.

Таким образом, входные измерения х; поступают на усреднение

ы

с единичным весом, когда (X||,-i. В интервале значений a(xj|.b, когда увеличивается вероятность принадлежности X., к аномальным измерениям, происходит -винзорирование, т.е. вместо Xj на суммирование (2) поступает постоянная величина

о,

далее

в интервале , используется понижающее веса и при |х|(с поступающее измерение отбраковывается, т.е. берется с нулевым весом.

Устройство усреднения содержит регистр 1, блок 2 формирования модуля, первый компаратор 3, второй компаратор 4, третий компаратор 5, второй элемент И 6, третий элемент И 7, первый элемент И 8, четвертый элемент И 9, пятый элемент И 10, шестой элемент И 11, элемент ИЛИ 12, накапливающий сумматор 13, блок 14 деления, генератор 15 тактовых импульсов, делитель 16 частоты, триггер 17, первый блок 18 вычитания, второй блок 19 вычитания, блок 20 вычисления обратной величины, первый

блок 21 умножения, второй блок 22 умножения.

Функционирование предложенного устройства основано на реализации

5 выражений (1) и (2).

Устройство работает следующим образом.

Сигнал установки исходного состояния от внешнего источника посту10 пает на установочный вход триггера 1 7 и обнуляющий вход накапливающего сумматора 13, при этом все разряды накапливающего сумматора 13 устанав ливаются в нулевое состояние, а триг15 гер 17 - в единичное состояние,

обеспечивая тем самым подачу управляющего сигнала на второй вход первого элемента И 8 и третьи входы эле- (1) ментов И 9-1 I .

20 Сигналы с генератора 15 тактовых импульсов поступают на тактирующий вход регистра 1, обеспечивая последовательное поступление входных сигналов X i Ci 1 , . . . ,п) в двоичном коде

25 и через первый вход первого элемен-. та И 8 - на делитель 16 частоты. Делитель 16 частоты обеспечивает деление частоты на п и его выходной сигнал поступает на счетный вход триггера 17, устанавливая его в нулевое состояние; тем самым формируется нулевой сигнал, запрещающий прохождение измерений в сумматор 13 через элементы И 9-11 и тактовых импульсов через элемент И 8. Таким образом, делитель 16 частоты определяет интервал усреднения посредством задания количества измерений п, поступающих в накапливающий сумматор 13.

Входные сигналы в цифровой форме через регистр 1 поступают на блок 2 формирования модуля, представляющий собой обычный регистр, все разряды которого, кроме знакового, соединены с соответствующими разрядами регистра 1; в знаковом разряде блока 2 постоянно, вне зависимости от входной информации, содержится потенциал, соответствующий

(2)

30

35

40

45

положительному числу. Таким образом, на выходе блока 2 формируются сигналы, соответствующие модулю значения входной величины, которые поступают на первые входы компараторов 55 3-5, первый вход элемента И 9 и второй вход блока i 8 вычитания. На вторые входы компараторов 3-5 с входов задания весовых коэффициентов устройВходные сигналы в цифровой форме через регистр 1 поступают на блок 2 формирования модуля, представляющий собой обычный регистр, все разряды которого, кроме знакового, соединены с соответствующими разрядами регистра 1; в знаковом разряде блока 2 постоянно, вне зависимости от входной информации, содержится потенциал, соответствующий

положительному числу. Таким образом, на выходе блока 2 формируются сигналы, соответствующие модулю значения входной величины, которые поступают на первые входы компараторов 5 3-5, первый вход элемента И 9 и второй вход блока i 8 вычитания. На вторые входы компараторов 3-5 с входов задания весовых коэффициентов устрой3

CTi поступают, соответственно, цифровые сигналы, равные СХ, b и с . Одновременно, .сигнал СХ поступа ет на первый вход элемента И 1.0 и второй вход второго блока 22 умножения, сигнал Ь - на второй вход второго блока 19 вычитания, сигнал с - на первые входы блоков 18.и 19 вычитания. Выбор конкретных значений О , Ь и с зависит от качества исходной измерительной информации; увличение уровня аномальных измерений приводит к необходимости увеличения этих величин.

Компараторы 3-5 совместно с вторми и третьими элементами И 6 и 7 реализуют процедуру принятия решения в соответствии с неравенствами в выражении (П .

Первый компаратор 3 обеспечивает проверку условия ), второй компаратор 4 - I хКЬ и третий компаратор 5 - |хКс. Инверсный выход первого компаратора 3 и прямой выход второго компаратора 4 поступают на первый и второй входы второго элемента И 6, а инверсный выход второго компаратора 4 и прямой выход третьего компаратора 5 - на первый и второй входы тре тьего элементами 7. Таким образом, на выходах второго и третьего элементов И 6 и 7 формируются логические функции, соответственно, |х-||5 аЛ|х-,| Ь и I х,( 3:ЬЛ|х|( Разрешающие сигналы с прямого выхода первого компаратора 3, второго элемента И 6 и третьего элемента И поступают на входы, соответственно, элементов И 9-11. На информационные входы второго и третьего элементов И 9 и 10 поступают сигналы |х ; | и а, соответственно, а на информационный вход элемента И 11 - сигнал, равный

,

с-сх,)

Формирование сигнала Zf осуществляется с помощью первого 18 и вТоро- го 19 блоков вычитания, инвертора 20, первого 21 и второго 22 блоков умножения. С выходов блоков 18 и 19 вычитания снимаются сигналы, равные разности сигналов, поступивших на их первые и вторые входы: с выхода первого блока 18 вычитания - сигнал с-(х|, поступающий на первый вход первого блока 21 умножения, а с выхода второго блока 19 вычитания- сигнал с-Ь, поступающий через блок

06832

20 на первый вход второго блока 22 умножения. Блок 20 формирует на вьгхо де сигнал 1/(с-Ь). С выхода второго блока 22- умножения сигнал а/(с-Ь)

5 поступает на второй вход первого блока 21 умножения, выходным сигна-. пом которого является Z j, поступающий на соответствующий вход элемента ИЛИ. .

10 Таким образом, в зависимости от разрешающего сигнала, обусловленного системой неравенств в выражении (О, на вход элемента ИЛИ 12 поступает соответствующий сигнал у .

15 При этом знаковый разряд элемента ИЛИ 12 непосредственно связан со знаковым разрядом регистра 1, за счет чего вьшолняется соответствие sign(y;)sign(x j).

20 С выхода элемента ИЛИ 12 сигналы

У| поступают в накапливающий (1

.

тор 13, где формируется сумма /

1

25 Соответствующий этой сумме сигнал

поступает на первый вход блока 14 деления, на второй его вход подается сигнал задания числа измерения, равный п. Выходной сигнал бЯока 14 деления равный , является выходом устройства.

Формула изобретения

Устройство усреднения, содержа 5 щее первый, второй и третий компараторы, делитель частоты, блок деления, блок вычисления обратной величины, первый, второй, третий, четвертый, пятый и шестой элементы И,

0 триггер и генератор тактовых импуль- ,сов, выходу которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера, вход установки которого яв ляется входом установки устройства, отличающееся тем, что, с целью повьш1ения точности усреднения в условиях априорной неопределенности, в него дополнительно введе ны

регистр, блок формирования модуля, первый и второй блоки вычитания, первый и второй блоки умножения, элемент ИЛИ и накапливающий сумматор, выход которого соединен с первьм

5 информационным входом блока деления, второй информационный вход которого является входом задания числа измерений устройства, а выход блока деления является выходом устройства, информационный вход регистра является информационным входом устройства, а тактовый вход регистра соединен с выходом генератора тактовых импульсов, группа разрядных выходов регистра подключена к группе информационны входов блока формирования модуля, а выход знакового разряда регистра соединен с первым входом элемента ИЛ выход блока формирования модуля подключен к информационному входу четвертого элемента И и первым информационным входам первого, второго и третьего компараторов и первого блока вычитания, второй информационный вход которого является первым входом задания массовых коэффициентов устройства и соединен с вторым информационным входом третьего компаратора и первым информационным входом второго блока вычитания, второй информационный вход которого объединен с вторым информационным входом второго компаратора и является вторым входом задания массовых коэффициентов устройства, второй информационный вход первого компаратора объединен с информационным входом пятого элемента И и с первым информационным входом второго блока умножения и является третьим входом задания массовых коэффициентов устройства, прямой выход первого компаратора соединен с первым управляющим входом четвертого элемента И,

второй управляющий вход которого объединен с первыми управляющими входами пятого и шестого элементов И и является входом установки устройства, инверсный выход первого компаратора подключен к первому входу второго элемента И, второй вход которого подключен к прямому выходу рого компаратора, инверсный выход которого подключен к первому входу третьего эле,ента И, второй вход которого соединен с прямым выходом третьего компаратора, выход второго

5 И подключен к второму управляющему входу пятого элемента И, выход третьего элемента И подключен к второму управляющему входу шестого элемента И, выходы четвертого,

0 пятого и шестого элементов И соединены с соответствующими входами элемента ИЛИ, выход которого соединен с информационным входом накапливающего сумматора, вход сброса которого

5 является входом установки устройства, выход первого блока вычитания соединен с первым информационным входом первого блока умножения, второй информационный вход которого под0 ключен к выходу второго блок а умножения, второй информационный вход которого соединен с выходом блока вычисления обратной величины, вход которого соединен с выходом второго блока вычитания, выход первого блока умножения соединен с информационным входом шестого элемента И,

У

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный преобразователь информации | 1985 |

|

SU1330642A1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Вероятностный интегратор | 1989 |

|

SU1667064A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве специализированного вычислителя, предназначенного для оценки параметров сигнала. Цель изобретения состоит в повышении точности усреднения в условиях априорной неопределенности относительно статистических характеристик исходной измерительной информации. Это достигается введением регистра 1, блока 2 формирования модуля, блоков 18 и 19 вычитания, блоков 21 и 22 умножения, элемента ИЛИ 12 и накапливающего сумматора 13, обеспечивающих взвешенное суммирование входных измерений, зависящее от их абсолютных значений. 2 ил. с s (Л -- rS fi ю о о: 00 со ю

-С -Ъ -т

а

.- а

.1

Составитель Е. Ефимова Редактор Г. Волкова Техред Т.Дубинчак Корректор С. Шекмар

Заказ 8719/52 Тираж 673 Подписное В 1ИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ПИП Патент, г, Ужгород, ул. Проектная, 4

| Мирский Г.Я | |||

| Аппаратурное определение характеристик случайных процессов | |||

| М.: Энергия, 1972, с | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Многоканальное усредняющее устройство | 1978 |

|

SU744609A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-08-18—Подача