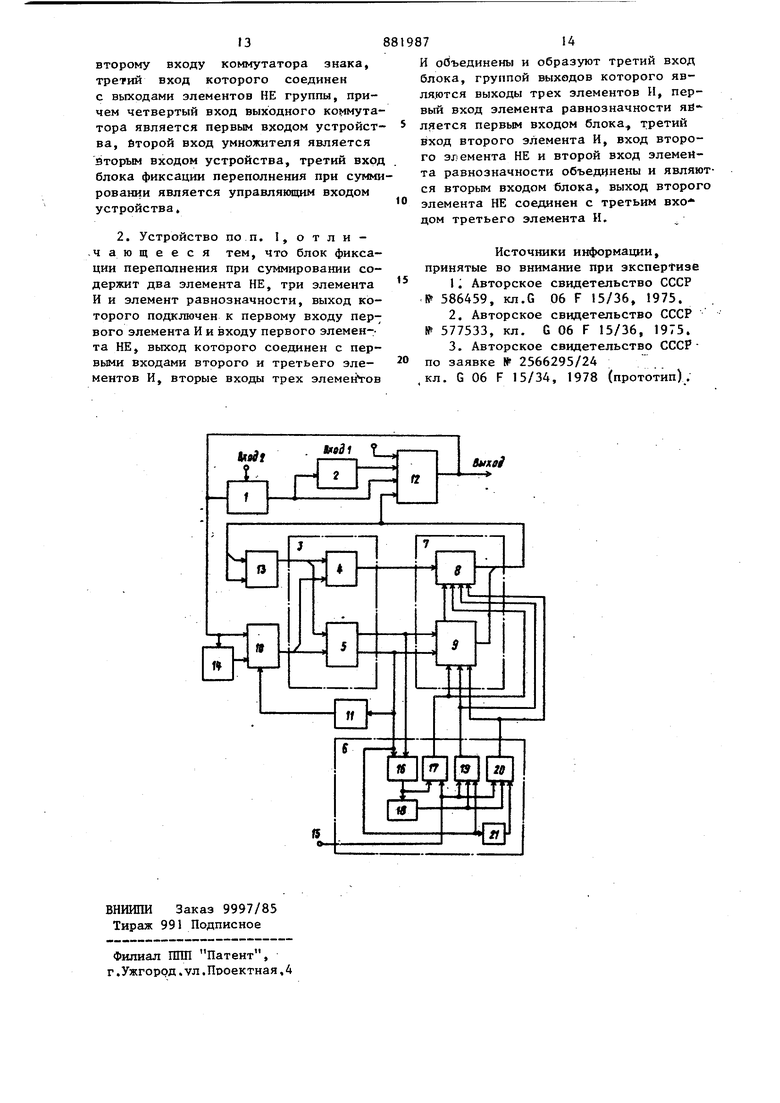

задавать весовые коэффициенты а; и bf одного порядка и тем самым ограничить разрядность умножителя, а возникающие при этом отклонения от единицы общего коэффициента передачи фильтра компенсировать за счет сдвига произведений. Однако известное арифметическое устройство обладает излишней сложностью вследствие использования сдвигающего коммутатора, представляющего собой громоздкую комбинационную схему. Кроме того, к недостаткам известного арифметического устройства относятся малое быстродействие, обуслов ленное последовательным соединением всех блоков, а следовательно и последовательной их работой; отсутствие возможности регулировать коэффициент передачи фильтра в зависимости от мощности входного сигнала. Известное арифметическое устройст во, которое содержит последовательно включенные умножитель с двумя входами и накапливающий сумматор, а так же блок сравнения, подключенный к выходу умножителя и интегрирующий фильтр 2 . Наличие интегрирующего фильтра и блока сравнения, на второй вход которого подан пороговый уровень сигнала, позволяет регулировать коэффициент передачи фильтра в зависимости от мощности входного сигнала, и, тем самым, стабилизировать уровень выход него сигнала. При этом блок сравнения и интегри рующий фильтр формируют корректирующий множитель С,, а умножитель и накапливающий сумматор вычисляют вспомогательный выходной сигнал п по формуле (1) и затем выходной сигнал ZD по формуле Z, СП-УП (2) При этом значении входного сигнала Хп и вспомогательного выходного сигнала поступают на первый вход умножителя, а коэффициенты а; , Ь-, , с на второй вход умножителя. Недостатком известного арифметиче кого устройства является высокая его сложность, обусловленная большой раз рядностью его блоков. Объясняется это тем, что уменьшение динамическог диапазона выходного сигнала за счет его автоматической регулировки позволяет лишь снизить разрядность других устройств, подключаемых к выходу фильтра и обрабатывающих его выходной сигнал, а арифметическое устройство работает с динамическим диапазоном входного сигнала. Устройство обладает также малым быстродействием вследствие последовательного соединения умножителя и накапливающего сумматора и тем самым их последовательной работы. Кроме того, примененная в известном устройстве схема формирования корректирующего множителя, состоящая из блока сравнения и интегрирующего фильтра, не всегда обеспечивает высокую стабильность частотных характеристик фильтрации вследствие влияния мощности входного сигнала на частотные свойства схемы за счет использования интегрирующего фильтра с постоянными параметрами и замыкания обратной связи с выхода фильтра через схему формирования корректирующего множителя на вход фильтра. Наиболее близким к предлагаемому по технической сущности и достигаемо У результату является устройство, которое содержит последовательно . включенные умножитель с двумя входами и первый накапливающий сумматор, Выход умножителя подключен к блоку сравнения, на второй вход которого подключен датчик порогового уровня. Выход блока сравнения связан с управляющим входом второго накапливающего сумматора, выход которого через схему сдвига связан с собственным информационным входом З , На первый вход умножителя поступают значения входного Х,,-, и выходного Yn-i сигналов. На второй вход умножителя поступают значения весовых коэффициентов a-i и Ь, и корректирующего множителя Сп, Умножитель и первый накапливающий сумматор производят вычисления по формулам (1) и (2) и вырабатывают выходной сигнал Iff, поступающий на блок сравнения. Блок сравнения совместно со вторым накапливающим сумматором вычисляют очередное значение корректирующего множителя С по формуле: С Сг,н+2- С„.,.п(,| ), (З) где А -.сигнал порогового уровня;S ign (А-/Zn-i/)-знаковая функция разности сигнала А порогового уровня и абсолютного значения выходного сигнала Zn-i . Знаковая функция равна +1 при1А - lZn-ii) О и -1 при (A-|Zn-iU 0. В известном устройстве обеспечена высокая стабильность частотных харак теристик фильтрации вследствие применения второго накапливающего сумматора вместо интегрирующего фильтра для формирования корректирующего мно жителя по формуле 3 . Недостатками известного устройства являются высокая сложность, обусловленная большой разрядностью блоков; малое быстродействие вследст- вие последовательного соединения умножителя и накапливающего сумматора, а тем самым их последовательной работы, Вырокая разрядность обусловлена двумя основными причинами: боль шим динамическим диапазоном входного сигнала и расширением динамического диапазона промежуточных значений сиг нала по сравнению с входным сигналом V-. - -, за счет разницы в порядке коэффициен тов а; и Ь( в формуле (1) . Известным методом сужения динами,ческого диапазона входного сигнала является его автоматическое регулирование, которое может быть выполнено в известном устройстве путем вычисления по формуле Хп ХздСп С4) где входной сигнал, и последующих вычислений по формулам (1) - (3). Однако при этом характерно следующее явление. Поскольку величина Xgjf и С связаны системой автоматического регулирования усиления по формулам (2) -(4) , то входному сигналу Xg малой мощ ности соответствует большое значение коэффициента С и нафборот, При этом использование умножителя с фиксированной запятой и представление чисел в масштабе, обеспечивающем X 1, С приводит к тому, что произведение (4) всегда существенно меньше максимально возможного - единицы, вследствие чего старшие разряды произведения ока зываются нулевыми и в разрядной сетке блоков устройства теряются понапрасну. С другой стороны простое от- брасывание этих старших разрядов недопустимо, так как среди значений входного сигнала Хц при низком среднем уровне мощности могут быть большие по величине отсчеты в отдельные моменты времени, В этом случае отбра76сывание старших разрядов привело оы к переполнению разрядной сетки и искажению результатов обработки сигнала. Поэтому -В известном устройстве большой динамический диапазон входного сигнала вызывает необходимость увеличения разрядности блоков устройства., Один из способов борьбы с другой причиной большой разрядности блоков расширением динамического диапазона промежуточных значений сигнала по сравнению с входным сигналом за счет разницы порядка коэффициентов aj и b-j в формуле (1) - известен. Он состои г в том, что после умножения входных сигналов Xfi-iHa коэффициенты а-, по формуле (1) перед сложением в накапливающем сумматоре произведения сдвигают на определенное количество разрядов в сторону младших по сравнению с произведениями выходных сигналов УП- на коэффициенты Ь , При этом обеспечивается близость к 1 результирующего коэффициента передачи фильтра, несмотря на большие значения коэффи- циентов а-,, порядок которых при этом может быть выбран таким же, как у коэффициентов Ь- , Уравнение (1) при этом принимает вил ч, -Р W ) 0 1S-1 Однако такой способ уменьшения разрядности требует больших затрат времени на вычисления, что связано с необходимостью выполнять большое количество умножений и сдвигов: М умножений Yf,., Ь; ; N+1 умножений Хп-1 а-, и р,сдвигов. Поэтому примен ние его в чистом виде нецелесообразно и в известном устройстве не реализовано, что приводит к увеличению разрядности блоков известного устройства, С другой стороны известно, что при реализации рекурсивных фильтров коэффициенты а-, обычно пропорциональны простым числам А-,, 3, Q-A-, , (6) где Q - коэффициент пропорциональности. Так, например, при реализации чебышевских фильтров второго порядка коэффициенты а,а„ и а пропорциональны числам соответственно и Г. С учетом равенства (6) уравнение (5)может быть преобразовано к следующему виду: Y (1-2-4 brYn.i.(7) i 0ial При реализации цифровых фильтров с автоматической регулировкой усиления коэффициентом Q в уравнении (} можно пренебречь вследствие того, что автоматическая регулировка усиления стабилизации мощности выходного сигнал непрерывно изменяет коэффициент передачи фильтра с помощью коэффициента С в формулах (2) и (4). Поэтому для реализации цифровых фильт ров с автоматической регулировкой усиления достаточно реализовать в арифметическом устройстве вычисления . по формулам (2) -(4) и по формуле Yn 2-Pi, AiXn.,b,Yn-i . (8) Цель изобретения - упрощение устройства и повышение его быстродействия. Поставленная цель Достигается тем что арифметическое устройство для ци ровой фильтрации с автоматической ре гулировкой усиления, содержащее умно житель и сумматор, оно содержит выходной коммутатор, коммутатор сдвига коммутатор знака, группу элементов Н триггер знака, сдвиговый регистр, блок фиксации переполнения при умножении, и блок фиксации переполнения при суммировании, группа выходов которого подключена к соответствующим входам информационных и знаковых разрядов сдвигового регистра, выходы информационных и знаковых разрядов которого соединены с первым входом выходного коммутатора и с группой входов коммутатора сдвига, выход которого соединен со входом информацио ной части сумматора, выход информаци онной части которого подключен к вхо ду информационных разрядов сдвиговог регистра, вход знаковых разрядов которого объединен с первым входом бло ка переполнения при суммировании и соединен с первым выходом знаковой части сумматора, второй выход знаковой части которого подключен ко второму входу блока фиксации переполнения при суммировании и входу триггера знака, выход которого подключен к первому входу коммутатора знака, выход которого подключен ко входу знаковой части сумматора, выход умножителя соединен со вторым входом выход ного коммутатора и входом блока фиксации, переполнения при умножении, вы ход которого подключен к третьему вх ду выходного коммутатора,выход которого является выходом устройства и подключен к первому входу умножителя входам элементов НЕ группы и второму входу коммутатора знака, третий вход которого соединен с выходами элементов НЕ группы, причем четвертый вход выходного коммутатора является первым входом устройства, второй вход умножителя является вторым входом устройства, третий вход блока фиксации переполнения при суммировании является управляющим входом устройства. А так же тем, что блок фиксации переполнения при суммировании содержит два элемента НЕ, три элемента И и элемент равнозначности, выход котЬрого подключен к первому входу первого элемента И и входу первого элемента НЕ,-выход которого соединен с . первыми входами второго и третьего . элементов И, втдрые входы трех элементов И объединены и образуют третий вход блока, группой выходов которого являются выходы трех элементов И, первый вход элемента равнозначности является первым входом блока,третий вход второго элемента НЕ и второй вход элемента равнозначности объединены и являются вторым входом блока, выход второго элемента НЕ соединен с третьим входом третьего элемента И. На чертелсе представлена структурная схема устройства. Устройство содержит матричный умножитель 1 с двумя входами, блок 2 фиксации переполнения нри умножении, комбинационный сумматор 3, со|Стоящий из цифровой части 4 и знаковой 5, блок 6 фиксации переполнения при суммировании, сдвиговый регистр 7, накопления суммы, состоящий из цифровой 8 и знаковой 9 частей, коммутатор 10 (сложения-вычитания)к управляющему входу которого подключен триггер 11 знака, выходной коммутатор 12, коммутатор 13 сдвига (суммы), труппа-14 элементов НЕ, причем выходы ЦИФРОВОЙ 4 и знаковой 5 частей сумма гopa 3 подключены к цифровой 8 и знаковой 9 частям регистра 7 накопления суммы соответственно, выходы двух знаковых разрядов части 5 сумматора 3 подключены также к блоку 6, управляющий .вход которого подключен к входу 15 управление, первый выход - к входу записи цифровой 8 и знаковой 9 частей регистра 7, второй выход - к управляющим входам записи О в цифровую 8 и записи 1 в знаковую 9 части регистра 7, а третий выход - к управляющим входам записи 1 в цифровую В и записи О в знаковую 9 части регистра 7. Блок фиксации переполнения содержит элемент 16 равнозначности, элемент 17И, элемент 18 НЕ, элементы 19 и 20И, элемент 21 НЕ. Принцип работы арифметического уст ройства для цифровой фильтрации с автоматической регулировкой усиления заключается в следующем. Устройство производит вычисления последовательно по формулам (3),(4), (8) и (2) . При вычислении по формуле (3)сначала определяется модуль сигнала Z)i«| . Для этого сигнала Zn-| по дается на первый вход устройства, откуда через коммутаторы 12 и 10 поступает на первый вход сумматора 3, на второй вход которого подается нулевой сигнал с регистра 7 через коммутатор 13. Знак сигнала запоминается в триггере 11 знака, после чего сигнал Zn-i еще раз подается на вхо устройства и через коммутатор 12 поступает на коммутатор 10, но при этом включается управление коммутатора 10 от трУиггера 11 знака. В зависимости ОТ знака сигна;|а , записанного в триггер 11 знака на вход сумматора проходит прямое или инверсное значение сигнала Zn-i , которое записывается в регистр 7 накапливания сум мы таким образом, что в регистре 7 оказы вается отрицательное значение модуля сигнала . Далее на первый вход устройства по дается пороговое значение сигнала А, которое через коммутаторы 12 и 1О поступает на.первый вход сумматора 3, на второй вход которого поступает записанное ранее число из регистра 7. Знак полученной при этом на выходе сумматора 3 разности А -IZf,.,i запоминается в триггере 11 знака и включается управление коммутатора 10 от триггера 11 знака. Далее на первый вход устройства подается корректирующий множитель Cf)-f , который передаётся через коммутатор 12 на коммутатор 10, а через последний в зависимости от знака, записанного в триггере 11 знака,, передается его прямое или инверсное зна чение в соответствии с уравнением ( Полученное значение записывается в регистр 7. Затем производится сдвиг полученного числа на К разрядов в сто рону младших. При этом сдвиг может вьтолняться двумя путями: в самом регистре 7 на один разряд за одну мик рокоманду (точный шаг) и путем перезаписи числа через второй вход коммутатора 13 и сумматор 3 со сдвигом на фиксированное число разрядов за одну микрокоманду (грубый шаг) . Сдвиг для ускорения выполняют сначала грубыми шагами, а затем точными шагами доводят его точно до К разрядов. После окончания сдвига полученное число в сумматоре складывают с С„,, , поступающим .через первый вход устройства,, коммутаторы 12 и 10, для чего коммутатор 13 устанавливают в состояние накопления. Полученное значение С поступает на выход устройства через коммутатор 12. Далее производят вычисление по уравнению (4. Для этого очередное значение входного сигнала поступает на первый вход устройства и через коммутатор 12 - на вход умножителя I; на второй вход устройства, являювшйся вторым входом умножителя 1, поступает корректирующий множитель Сп. Полученный при этом сигнал произведения с выхода умножителя 1 поступает со. сдвигом в сторону старших разрядов через блок - 2 и коммутатор 12 на выход устройства. Далее решается уравнение (8), для чего на первый вход устройства поочередно поступают значения вспомогательного входного Хц-( и вспомогательного выходного УП-| сигнала. Сигнал Хц-| поступает через первый вход коммутатора 10 сложения-вычитания на первьй вход сумматора 3. Умножение А; на производится путем последовательного сложения с накоплением сигнала Xn-i в сумматоре 3 и регистре 7 столько раз, чему равен коэффициент А. Умножение накопленной суммы про-, изведений А; .Xn-i на коэффициент 2 производится путем сдвига в сторону младших разрядов аналогично тому, как это делается в уравнении (3). Одновременно с работой сумматора 3 на включенном параллельном умножителе 1 производится умножение сигналов Y|,i , которые поступают на первый вход умножителя 1 на коэффициенты Ь|, которые поступают на второй вход устройства, являкицийся вторым входом ; умножителя 1. Полученные произведения через коммутатор 12 и 10 поступают на вход сумматора 3, в результате чего в регистре 7 накопления суммы формируется сигнал УГУ в соответствии с уравнением (8), поступающий через ко мутатор 12 на выход устройства. Далее производятся вычисле-ция по уравнению (2) аналогично вычисленным по уравнению (4) , а результирующий сигнал Zfi с выхода умножителя 1 со сдвигом в сторону старших разрядов через блок 2.и коммутатор 12 поступает на выход устройства. При вычислении сигнала У, по урав нению (8), когда производится многократное сложение в сумматоре 3 с накоплением суммы в регистре 7, возможно переполнение разрядной сетки сумматора 3. Для уменьшения возможных ошибок вычислений, возникающих при этом, включен блок 6. На блок 6 подаются два знаковых разряда с знаковой части 5 сумматора, 3 и управляющий импульс с управляющей ши ны 15, Два .знаковых разряда поступают на элемент 16 равнозначности, на выходе которой в случае совпадения знаковых разрядов между собой (что означает отсутствие переполнения) фо пающий на элемент 17 И, который пропускает управляющий импульс от шины 15 на входы записи цифровой 8 и знаковой 9 частей регистра 7. . . При несовпаде ши знаковых разрядов, что означает переполнение разрядной сетки, выходной сигнал элемен та 16 равнозначности запрещает про хождение управляющего импульса через элемент 7 И, а на выходе элемента НЕ 18 формируется сигнал, разрешающи прохождение управляющего импульса че рез элементы 19 и 20 И. При этом в зависимости от значения старшего знакового разряда, поступающего на элемент 19 И и через элемент НЕ 21 на элемент 20 И, управляющий импульс проходит через один из элементов И 1 или 20, и устанавливает знаковую часть 9 регистра 7 в состояние, соответствующее старшему знаковому раз ряду, а цифровую часть 8 регистра 7 в противоположное состояние (все нули или все единицы), соответствующее максимальному положительному или отрицательному числу. Эффективность предложенного технического решения особенно высока пр построении многоканальных систем цифровой фильтрации с жесткими ограничениями на весогабаритные характеристики, когда требуется простое, малоразрядное и в. то же время быстродействующее арифметическое устройство. Предложенное устройство за счет распараллеливания вычислительного процесса в сумматоре и умножителе, за счет ускоренных сдвигов в сторотгу младших разрядов и сдвигов в сторону старших разрядов с фиксацией и исправлением переполнения при автоматической регулировке усиления позволяет обрабатывать сигналы большого динамического диапазона по нескольким каналам одновременно. Формула изобретения .Арифметическое устройство для циф- ровой фильтрации с автоматической регулировкой усиления, содержащее умножитель и сумматор, отличающееся тем, что, с целью упрощения и повышения быстродействия, оно содержит выходной коммутатор, коммутатор сдвига, коммутатор злака, группу элементов НЕ, триггер знака, сдвиговый регистр, блок фиксации переполнения при умножении, и блок фиксации переполнения при суммировании, группа выходов Которого подключена к соответствующим входам информационных и знаковых разрядов сдвигового регистра, выходы информационных и знаковых разрядов которого соединены с первым входом выходного коммутатора и с группой входов коммутатора сдвига, выход которого соединен со входом информационной части сумматора, выход информационной части которого подключен к входу информационных разрядов сдвигового регистра, вход знаковых разрядов которого объединен с первым входом блока переполнения при с уммировании и соединен с первым выходом знаковой части сумматора, второй выход знаковой части которого подключен ко второму входу блока фиксации переполнения при суммировании и входу триггера знака, выход которого подключен к первому ВХОДУ лхоммутатора знака, выход которого подключен ко входу знаковой части сумматора, выход умножителя соединен со вторым входом выходного коммутатора и входом блока фиксации переполнения при умножении, выход которого подключен к третьему входу выходного коммутатора, выход которого является выходом устройства и подключен к первому входу умножителя, входам элементов НЕ группы и

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1988 |

|

SU1566471A1 |

| Цифровой фильтр с регулируемым коэффициентом передачи | 1979 |

|

SU783800A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для цифровой корреляционнойфильТРАции | 1978 |

|

SU799108A1 |

| Электронный измеритель мощности и энергии | 1988 |

|

SU1638653A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

Авторы

Даты

1981-11-15—Публикация

1979-11-13—Подача