10

20

25

I1208583

Изобретение относитсяг к вычислиельной технике и может быть использовано в запоминающих устройствах . аксимильной аппаратуры при органиации питания в системах сжатия нформации.

Цель изобретения - уменьшение потребляемой мощности устройства.

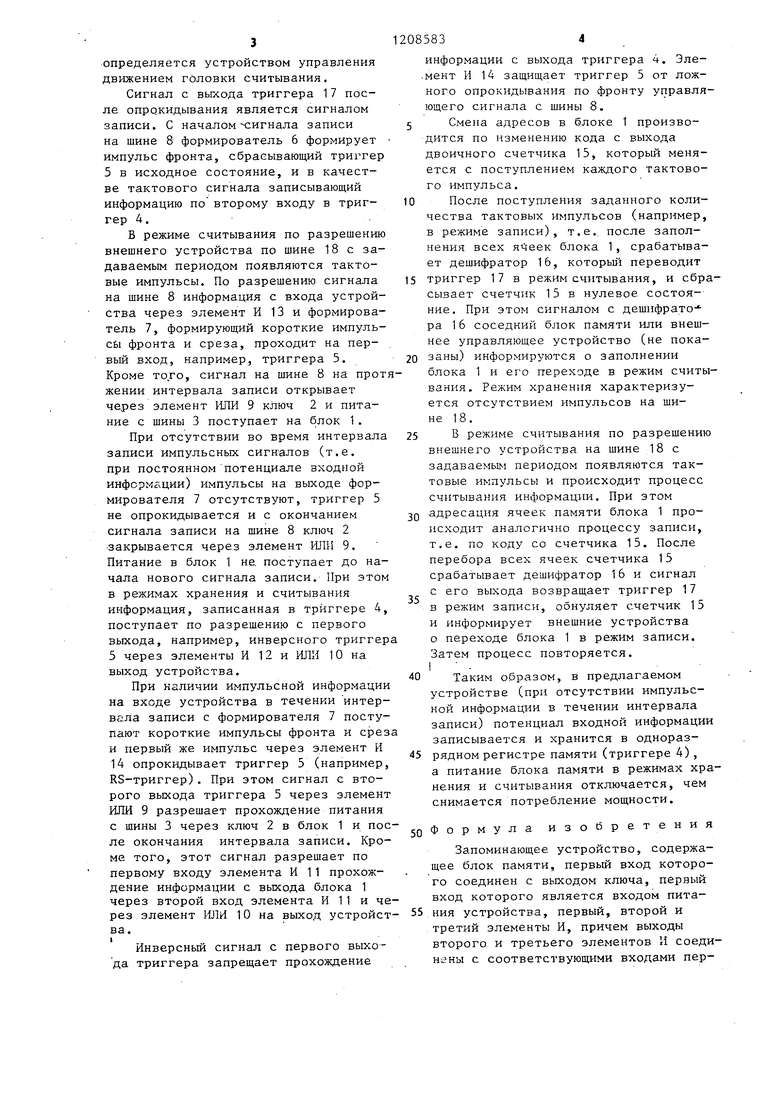

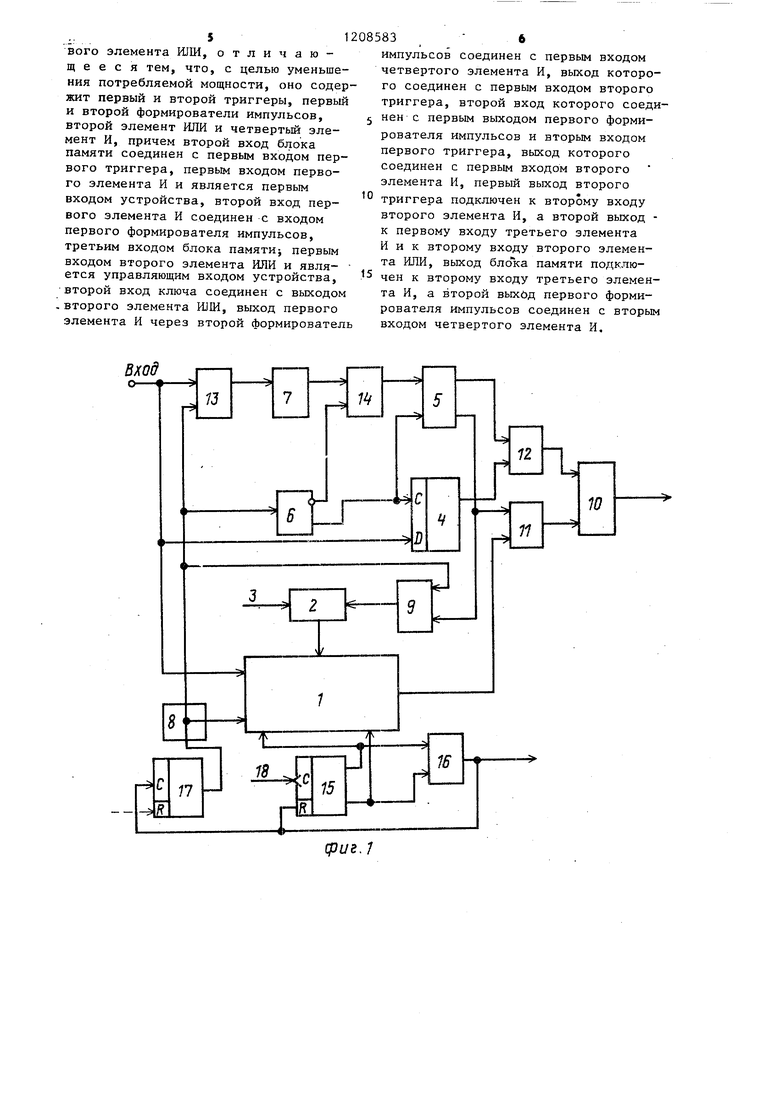

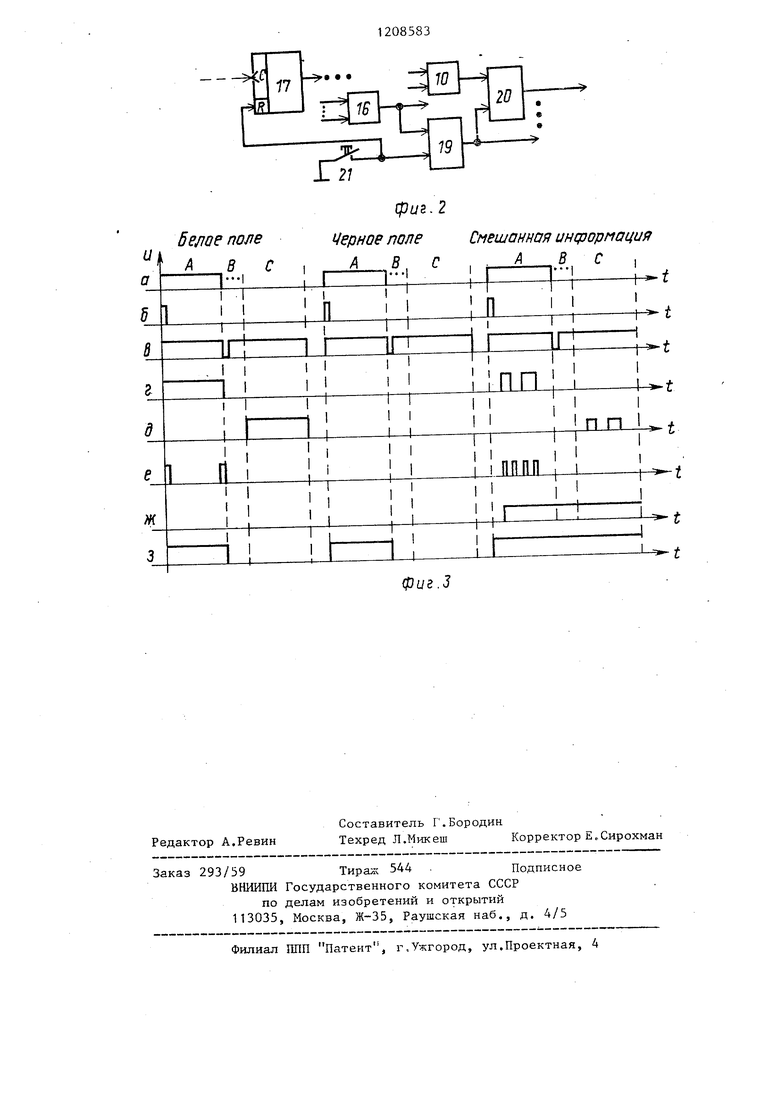

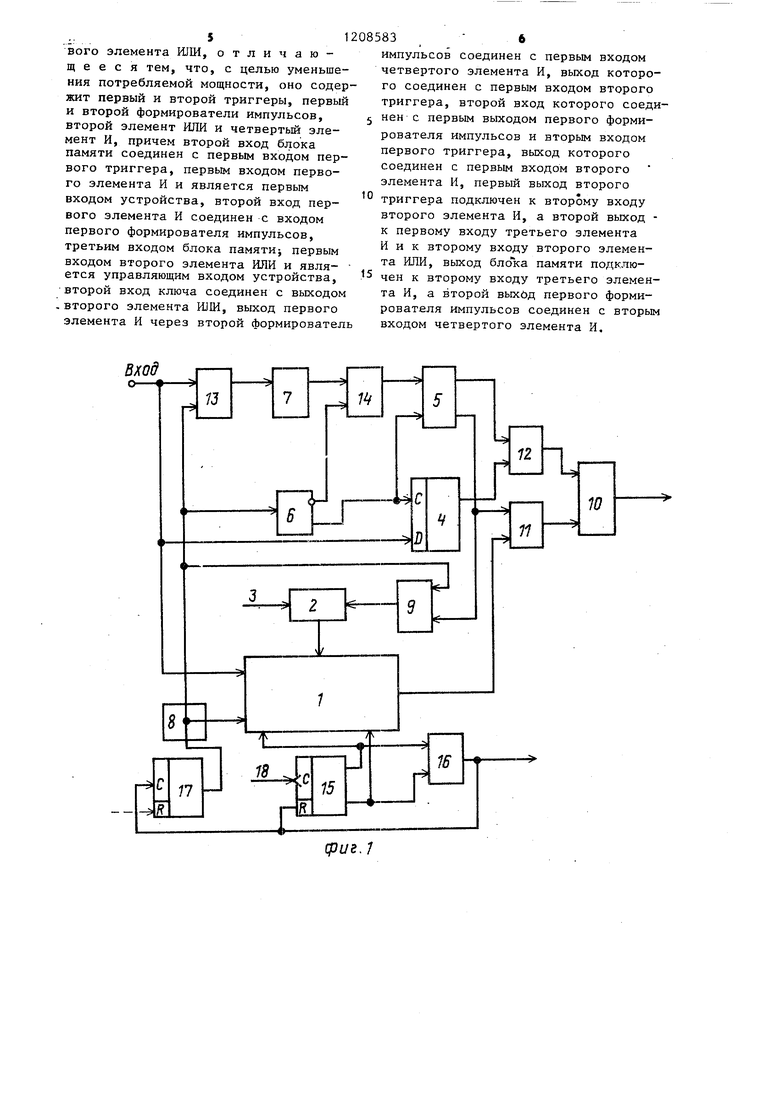

На фиг. 1 изображена функциональая схема предлагаемого устройства; а фиг. 2 - пример структурной схеы подготовки запуска запоминающего устройства; на фиг. 3 - диаграмма аботы запоминающего устройства.

Запоминающее устройство содержит блок 1 памяти, ключ 2, шину 3 питаия, два триггера 4 и 5, два формиователя 6 и 7 импульсов, шину 8 Режим, два элемента ИЛИ 9 и 10, четыре элемента И 11-14, счетчик 15 мпульсов, дешифратор 16, триггер 17 и тактовую пшну 18.

Схема подготовки запуска запоми- нающаго устройства содержит триггер 19, элемент И 20 и кнопку 21 Пуск,

Запоминающее устройство работает в трех режимах зап1|си (А), хранения (в) и считывания (С) при поступлении сигналов информации от белого, чер- ного и смешанного полей (фиг. За, - сигнал на шине 8, фиг.. ЗВ - сигнал с первого выхода формирователя б, ф1лг. 3fe- сигнал второго выхода формирователя 6, фиг. Зе - сигнал на входе устройства, фиг. 3 - сигнал на выходе устройства, фиг. Зе- сигнал на выходе формирователя 7, фиг, Зж- сигнал на втором выходе триггера 5, фиг. 3 - . сигнал на выходе ключа 2).

Шина 3 через ключ 2 подключена к первому, входу блока 1. Вход устройства подключен к второму входу блока 1. Шина 8 подключена к второму входу элемента И 13, входу формирователя 6, третьему входу блока 1 и первому входу элемента ИЛИ 9, выход которого соединен с вторым входом ключа 2. Выход элемента И 13 через формирователь 7 и первый вход элемента И 14 подключен к первому входу триггера 5, к второму входу которого подключен первый выход формирователя 6 и второй вход триггера 4, выход которого соединен с первым входом элемента И 12, Первый выход триггера 5 подключен к его третьему входу и к второму входу элемента И 12, а второй выход - к первому вкоду элемента И 11 и второму входу

эл кл бл эл 11 та вы ми вх че к ко да вы

15 му вх

че тр ге по Вы ме вт на ст

30 сл

ки на

35 эт ся вы ме по Пр па но ли ср ва по ся |Не ин ра пр ни те Пр го

55 ющ дв яч ва

-30

45

50

0

5

элемента ИЛИ 9, выход которого подключен к второму входу ключа 2. Выход блока 1 подключен к второму входу элемента И 11, а выходы элементов И 11 и 12 подключены к входам элемента ИЛИ 10, выход которого является выходом устройства, второй выход формирователя 6 подключен к второму входу элемента И 14. Шина 8 подключена к выходу триггера 17, шина 18 - к первому входу счетчика 15, выходы которого подключены к адресным входам блока 1 и входам дешифратора 16, выход которого подключен к сбросово5 му входу счетчика 15 и счетному входу триггера 17.

В схему подготовки запуска (фиг. Зг) кнопка 21 Пуск подключена к второму (сбросовому) входу триггера 17 и первому входу триггера 19, к второму входу которого подключен выход дешифратора 16. Выход триггера 17 подключен к элементу И 20, к выходу которого через второй вход подключен выход запоминающего устройства. Выход триггера 19 является внешним выходом устройства подготовки запуска.

Запоминающее устройство работает

0 следующим образом.

При кратковременном кнопки 21 Пуск триггеры 17 и 19 устанавливаются в состояние О. При

5 этом сигналом с триггера 19 блокируется элемент И 20 и соответственно выход запоминающего устройства. Кроме того, с выхода триггера 19 сигнал поступает на выход схемы запуска. При этом на тактов то шину 18 поступают импульсы, например, с повышенной частотой и счетчик 15 устанавливается в состояние, при котором срабатывает дешифратор 16, опрокидывающий триггеры 17 и 19. Выход запоминающего устройства деблокируется, а сигнал логической 1 на внеш- |Нем выходе схемы подготовки запуска информирует внешнее устройство управления о возможности работы. Например, о возможности начала движения считывающей головки вдоль строки текста в факсимильном передатчике. При этом информация со считывающей головки поступает на вход запомина5 ющего устройства и в каждом такте движения заносится в соответствующую ячейку памяти блока 1. Период следования тактовых импульсов на шине 18

0

5

0

определяется устройством управления движением головки считывания.

Сигнал с выхода триггера 17 после опрокидывания является сигналом записи. С началом х:игнала записи на шине 8 формирователь 6 формирует импульс фронта, сбрасывающий триггер 5 в исходное состояние, и в качестве тактового сигнала записывающий информацию по второму входу в триггер 4.

В режиме считывания по разрешению внешнего устройства по шине 18 с задаваемым периодом появляются тактовые импульсы. По разрешению сигнала на шине 8 информация с входа устройства через элемент И 13 и формирователь 7, формирующий короткие импуль- сб1 фронта и среза, проходит на первый вход, например, триггера 5. Кроме то.го, сигнал на шине 8 на протжении интервала записи открывает через элемент ИЛИ 9 ключ 2 и питание с шины 3 поступает на блок 1.

При отсутствии во время интервала записи импульсных сигналов (т.е. при постоянном потенциале входной информации) импульсы на выходе формирователя 7 отсутствуют, триггер 5 не опрокидывается и с окончанием сигнала записи на шине 8 ключ 2 -закрывается через элемент ИЛИ 9. Питание в блок 1 не. поступает до начала нового сигнала записи. При этом в режимах хранения и считывания информация, записанная в триггере 4, поступает по разрешению с первого выхода, например, инверсного триггер 5 через элементы И 12 и ИЛИ 10 на выход устройства.

При наличии импульсной информации на входе устройства в течении интервала записи с формирователя 7 поступают короткие импульсы фронта и срез и первый же импульс через элемент И 14 опрокидывает триггер 5 (например, RS-триггер). При этом сигнал с второго выхода триггера 5 через элемент ЖМ 9 разрешает прохождение питания с шины 3 через ключ 2 в блок 1 и после окончания интервала записи. Кроме того, этот сигнал разрешает по первому входу элемента И 11 прохождение информации с выхода блока 1 через второй вход элемента И 11 и через элемент ИЛИ 10 на выход устройства.

Инверсный сигнал с первого выхода триггера запрещает прохождение

информации с выхода триггера 4. Эле- мент И 14 защищает триггер 5 от ложного опрокидывания по фронту управляющего сигнала с шины 8.

Смена адресов в блоке 1 производится по изменению кода с выхода двоичного счетчика 15, который меняется с поступлением каждого тактового импульса.

После поступления заданного количества тактовых импульсов (например, в режиме записи), т.е.. после заполнения всех ячеек блока 1, срабатывает дешифратор 16, который переводит

триггер 17 в режим считывания, и сбрасывает Счетчик 15 в нулевое состояние. При этом сигналом с дешифрато- ра 16 соседний блок памяти или внешнее управляющее устройство (не показавы) информируются о заполнении

блока 1 и его переходе в режим считывания. Режим хранения характеризуется отсутствием импульсов на шине 18.

В режиме считывания по разрешению внешнего устройства на шине 18с задаваемым периодом появляются тактовые импульсы и происходит процесс считывания информации. При этом

адресация ячеек памяти блока 1 происходит аналогично процессу записи, т.е. по коду со счетчика 15. После перебора всех ячеек счетчика 15 срабатывает дешифратор 16 и сигнал с его выхода возвращает триггер 17 в режим записи, обнуляет счетчик 15 и информирует внешние устройства

0переходе блока 1 в режим записи. Затем процесс повторяется.

1 .

Таким образом, в предлагаемом

устройстве (при отсутствии импульсной информации в течении интервала записи) потенциал входной информации записывается и хранится в однораз- рядном регистре памяти (триггере 4), а питание блока памяти в режимах хранения и считывания отключается, чем снимается потребление мощности.

Формула изобретения

Запоминающее устройство, содержащее блок памяти, первый вход которого соединен с выходом ключа, первый вход которого является входом пита- ния устройства, первый, второй и третий элементы И, причем выходы второго и третьего элементов И соединены с соответствующими входами пер

5

вого элемента ИЛИ, отличающееся тем, что, с целью уменьшения потребляемой мощности, оно содержит первый и второй триггеры, первый и второй формирователи импульсов, второй элемент ИЛИ и четвертьй элемент И, причем второй вход блока памяти соединен с первым входом первого триггера, первым входом первого элемента И и является первьпу входом устройства, второй вход первого элемента И соединен с входом первого формирователя импульсов, третьим входом блока памятиj первым входом второго элемента ИЛИ и явля- ется управляющим входом устройства,

второй вход ключа соединен с выходом .второго элемента ИЛИ, выход первого элемента И через второй формирователь

1208583 6

импульсов соединен с первым входом четвертого элемента И, выход которого соединен с первым входом второго триггера, второй вход которого соединен с первым выходом первого формирователя импульсов и вторым входом первого триггера, выход которого соединен с первым входом второго элемента И, первый выход второго триггера подключен к второму входу второго элемента И, а второй выход - к первому входу третьего элемента И и к второму входу второго элемента ИЛИ, выход бло ка памяти подключен к второму входу третьего элемента И, а второй выход первого формирователя импульсов соединен с вторым входом четвертого элемента И.

10

15

cpusj

белое поле

Редактор А.Ревин

Составитель Г.Бородин

Техред Л.Микеш Корректор Е.Сирохман

Заказ 293/59Тираже 544 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г,Ужгород, ул.Проектная, 4

фиг. 2

фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Электронные часы с фиксацией и документированием времени | 1988 |

|

SU1552147A1 |

| Устройство отображения формы электрического сигнала | 1983 |

|

SU1151820A1 |

| Функциональный генератор | 1987 |

|

SU1501100A1 |

| Устройство для управления блокомпАМяТи | 1978 |

|

SU809345A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах факсимильной аппаратуры. Изобретение позволяет уменьшить потребляемую запоминающим устройством мощность. Снижение потребляемой мощности достигается отключением питания от запоминающего, устройства в том случае, когда в нем отсутствует информация. Уст- ройство содержит блок памяти, ключ, шину питания, триггеры, формирователи импульсов, шину Режим, элементы ИЛИ, элементы И, счетчик импульсов, дешифратор, тактовую шину. 3 ил. с

| Патент США № 3703710, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Запоминающее устройство | 1974 |

|

SU522523A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-01-30—Публикация

1984-08-08—Подача