1

Изобретение относится к вычислиельной технике и может быть использовано в автоматизированных измериельных системах (ДИС), получающих и обрабатывающих с помощью ЭВМ инфорацию о нескольких исследуемых процессах.

Известно устройство, содержащее регистр числа, усилители считывания и формирователи записи, регистр ад- . реса, выходы которого подключены к дешифратору адреса, адресные ключи, входы которых соединены с дешифратором адреса, а выходы - с соответствующими входами блоков памяти, блок местного управления и шину нулевого потенциала 1.

Однако функциональные возможности такого устройства недостаточны для работы в составе АИС, предназначенной для регистрации и обработки информации о нескольких исследуемых процессах.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для управления оперативным накопителем, содержащее регистр числа, дешифратор гщреса, первые входы которых соединены с первым выходом формирователя импульсов,

регистр адреса, выходы которого подключены к соответствующим вторым входам дешифратора адреса, а входы - к соответствующим первым выходам первого счетчика адреса, первый и второй входы которого соответственно соединены со втopы и третьим выходами формирователя импульсов, и блок задания режима работы 2 .

0

Запись, и считывание информации осуществляются лишь последовательно, в порядке поступления чисел на вход ЗУ. Однако при обработке результатов измерений нескольких процессов, заре5гистрированных в одном блоке памяти, такой порядок считывания приводит к усложнению программы обработки информации на ЭВМ и не позволяет выводить данные на монитор для предварительной

0 оценки- результатов эксперимента.

Цель изобретения - расширение области применения устройства за счет изменения порядка считываемой информации .

5

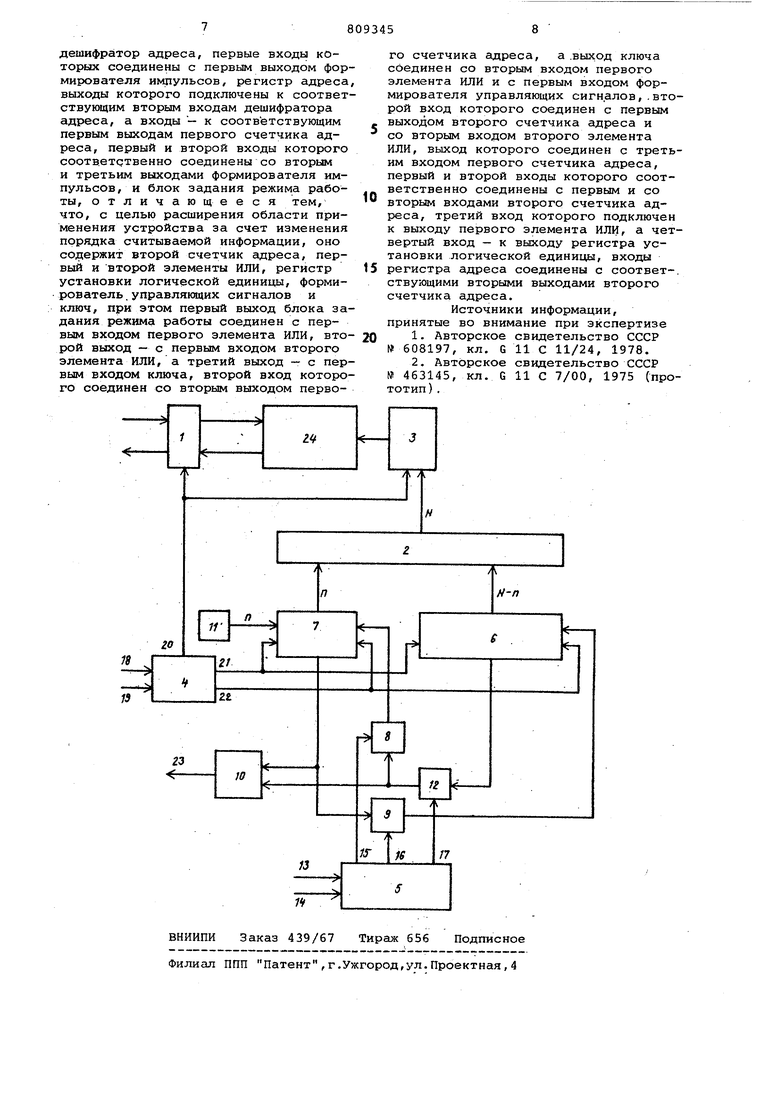

Указанная цель достигается тем, что устройство содержит второй счетчик адреса, первый и второй элементы ИЛИ, регистр установки логической единицы, формирователь управляющих сигналов и ключ, при этом первый Ei:i0ход блока задания режима работы соед нен с первым входом первого элемента ИЛИ, второй выход - с первым входом второго элемента ИЛИ, а третий выход - с первым входом ключа, второй вход которого соединен со вторым выходом первого счетчика адреса, а выход ключа соединен со вторым входо первого элемента ИЛИ и с первым входом формирователя управляющих сигналов, второй вход которого соединен с первым выходом второго счетчика адре са и со вторым входом второго элемен та ИЛИ, выход которого соединен с третьим входом первого счетчика адре са, первый и второй входы которого соответственно соединены с первым и со вторым входами второго счетчика адреса, третий вход которого подключен к выходу первого элемента ИЛИ, а четвертый вход - к выходу регистра установки логической единицы, входы регистра адреса соединены с соответствующими вторыми выходамивторого счетчика адреса. На чертеже изображена блок-схема устройства. Устройство содержит регистр числа 1, регистр адреса 2, дешифратор адреса 3, формирователь импульсов 4, блок 5 задания режима работы, первый счетчик адреса б, второй счетчик адреса 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, формирователь 10 управляющих сигналов, регистр 11 установки логической единицы, ключ 12, управляющие шины 13-23 и блок памяти 24.. Устройство обеспечивает работу в режимах Запись, Считывание и Контроль информации. . Р е ж и м 3 а п и с ь. Из контроллера АИС (на чертеже не показан) по шине 13 на вход блока 5 задания режима работы поЬтупает сигнал, соответствукадий режиму Запись. При этом на первом 15 и треть ем 17 ВЫХОДС1Х 15 и 17 блока 5 задания режима работы появлюотся управляющие потенциалы, которые поступают на ключ 12 и через первый элемент или 8 - на третий управлякнций вход второго счетчика адреса 7, подготавливая их к работе. На шине 16 (второй/ выход блока 5 задания режима работй) управляющий потенцигш отсутствует. Одновременно по шине 18 на вход формирователя импульсов 4 поступает сигнал Начало работы, по которому формирователь импульсов 4 формирует импульс сброса.Этот импуль по шине 21 (второй вУход формировате ля импульсов 4) поступает на первые входы всех разрядов первого 6 и второго 7 счегчиков адреса и устанавли.вает их в нулевое положение. В регистр адреса 2 поступает начальный код адреса. с приходом на шину 19 первого синхроимпульса формирователь импульсов 4 формирует импульс запроса, который по шине 20 (первый выход формирователя импульсов 4) поступает на регистр числа 1 и на первый вход дешифратора адреса 3. Осуществляется запись числа первого слова первого измеряемого процесса в первую ячейку блока памяти 24. Далее тактовый импульс с задержкой относительно импульса Запрос на время, необходимое для записи числа в блок памяти 24, по шине 22 (третий выход формирователя импульсов 4) поступает на вторые (счетные) входы обоих счетчиков адреса 6 и 7. Однако, поскольку управляющий потенциал на. первый счетчик 6 не подан, то прибавление единицы происходит лишь во втором счетчике 7. С приходом на шину 19 второго синхроимпульса происходит запись первого слова второго измеряемого процесса и так далее до тех пор, пока на выходе второго счетчика адреса 7 не установится код числа равного числу измеряемых процессов. При этом на втором выходе счетчика адреса 7 образуется сигнал, который через второй элемент ИЛИ 9 поступает на тре- тий (управляющий) вход первого счетчика адреса 6, подготавливая его к работе. Следующий тактовый импульс изменяет состояние обоих счетчиков. В младшем разряде первого счетчика адреса 6 устанавливается 1, а второй счетчик адреса 7 переходит в нулевое положение, после чего управляющий потенциал с третьего входа первого счетчика адреса б снимается. С приходом импульса запроса в блок памяти 24 записывается второе слово первого процесса, в следующем такте - второе слово второго процесса и т.д . В предлагаемом режиме работа устройства будет.продолжаться до тех пор, пока на всех первых выходах первого счетчика адреса б не установится 1. Тогда на втором выходе этого счетчика образуется сигнал переполнения, который чер.ез открытый ключ 12 поступит на первый вход формирователя 10 управлякнцих сигналов, с приходом на который сигнала переполнения со второго выхода второго счетчика адреса 7 формируется управляющий сигнал, который по шине 23 поступит в контроллер АИС и прекратит работу устройства в режиме запись. Режим Считывание. Управляющий сигнал, соответствующий данному режиму работы, по шине 13 поступает на вход блока 5 задания режима работы. При этом на втором 16 и третьем 17 выходах появляются потенциаипы, поступающие на ключ 12 и через второй элемент ИЛИ 9 - на третий управляющий вход первого счетчика адреса 6. По сигналу Начало работы все разряды обоих счетчиков устанавливаются в нулевое положение.

С приходом первого синхроимпульса формирователь импульсов 4 формирует импульс запроса, и на выходе регистра числа 1 появляется код числа первого слова первого измеренного процесса. Тактовый импульс проходит с третьего выхода формирователя импульсов 4 по шине 22 на вторые счетные входы счетчиков адреса 6 и 7 и в мпадшемразряде первого счетчика адреса б устанавливается 1.

С приходом второго синхроимпульса на выходе регистра числа 1 появляется код числа второго слова первого процесса, а первый счетчик адреса 6 переходит в следующее положение. И так до тех пор, пока все числа, соответствующие первому измеренному процессу не будут считаны. Затем со второго выхода первого счетчика адреса 6 на третий управляющий вход второго счетчика адреса 7 через ключ 12 и первый элемент ИЛИ 8 подается управляющий сигнал. Следующий тактовый импульс перебросит первый разряд второго счетчика адреса 7 в положение 1, а все разряды первого счетчика адреса 6 установятся в нулевое положение, что соответствует коду адреса первого слова второго процесса.

Аналогичным образом будет осуществляться считывание последующих слов второго процесса и т.д. После того, как закончится считывание чисел последнего из измеренных процессов, на оба входа формирователя 10 управляющих сигналов со вторых выходов счетчиков адреса б и 7 через ключ 12 поступают управляющие сигналы, и формирователь 10 управляющих сигналов формирует сигнал переполнения, после чего работа устройства в режиме считывания прекращается.

Режим Контроль информации.

Управляющий сигнал, соответствующий режиму считывания, поступает на шину 13, а на шину 14 - сигнал, соответствующий режиму Контроль информации . При этом управляющий потенциал устанавливается лишь на втором выходе 16 блока 5 задания режима работы. Ключ 12 переходит в закрытое состояние.

На выходе счетчика 7 с помощью регистра 11 установки логической единицы устанавливается код, соответствукядий номеру контролируемого процесса.

С приходом синхроимпульсов формирователь импульсов 4 формирует импульс запроса и тактовые импульсы, поступающие на счетные входы счетчиков адреса б и 7. Однако поскольку сигналы переполнения, появляющиеся

на втором выходе первого счетчика адреса 6 через ключ 12, на третий управляющий вход второго счетчика адреса 7 не проходят, то его состояние не меняется и сигналы переполнения на выходе формирователя управляющих сигнсшов 10 не формируются. Первый счетчик адреса 6 работает в циклическом режиме, поэтому происходит переодическое считывание чисел одного контролируемого процесса.

o

Предлагаемое устройство может быть реализовано на интегральных микроiсхемах типа ТТЛ например, серии К155. Счетчики адреса б и 7 собраны по параллельно-последовательной схеме на

5 триггерах типа э-К и логических элементах типа И-НЕ. Формирователь импульсов 4 -содержит элементы И-НЕ и линии задержки. Регистр 11 установки логической единицы представляет со0бой кнопочный переключатель, контакты которого подключены к элементам И-НЕ. На элементах И-НЕ выполнены блок 5 задания режима работы, формирователь 10 управляющих сигналов и ключ 12. Управляемый блок памяти

5 24, регистр числа 1 с усилителями считывания и формирователями записи, регистр адреса 2 с усилителями, дешифратор адреса 3 с ключевыми схемами конструктивно объединены в еди0ный блок-модуль оперативной памяти, выпускаемый промышленностью. Информационная емкость модуля 2048 18-разрядных слов. Соответственно число разрядов (N) в регистре адреса рав5но 11.

В режиме Запись информация от датчиков на вход регистра числа 1 поступает через коммутатор каналов и АЦП. При считывании информация с

0 выхода регистра числа 1 поступает в память ЭВМ, а в режиме Контроль информации - через цифроаналоговый преобразователь на монитор, в качестве которого может быть использован осциллограф. Синхронная работа

5 устройства для управления блоком памяти и внешних устройств обеспечивается с помощью контроллера АИС.

При использовании предлагаемого устройства достигается существенное

0 упрощение схемы запоминающего устройртва, обеспечивается работа буферного ЗУ в режимах Запись, Считывание и Контроль информации, режим Контроль информации, позволяет осу5ществлять предварительную оценку полученных данных, в режиме Считывание обеспечивается такой порядок вывода информации, при котором существенно упрощается алгоритм обработки

0 результатов измерений на ЭВМ и со ращаются затратымаижнного времени.

Формула изобретения Устройство для управления блоком

5 памяти, содержащее регистр числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

Авторы

Даты

1981-02-28—Публикация

1978-10-19—Подача