л

Изобретение относится к радиотехнике и может, использоваться в прецизионных генераторах сигналов с частотной модуляцией в радиолокационных и связных системах, а в акусто электронных фурье-процессорах.

Целью изобретения является повышение быстродействия.

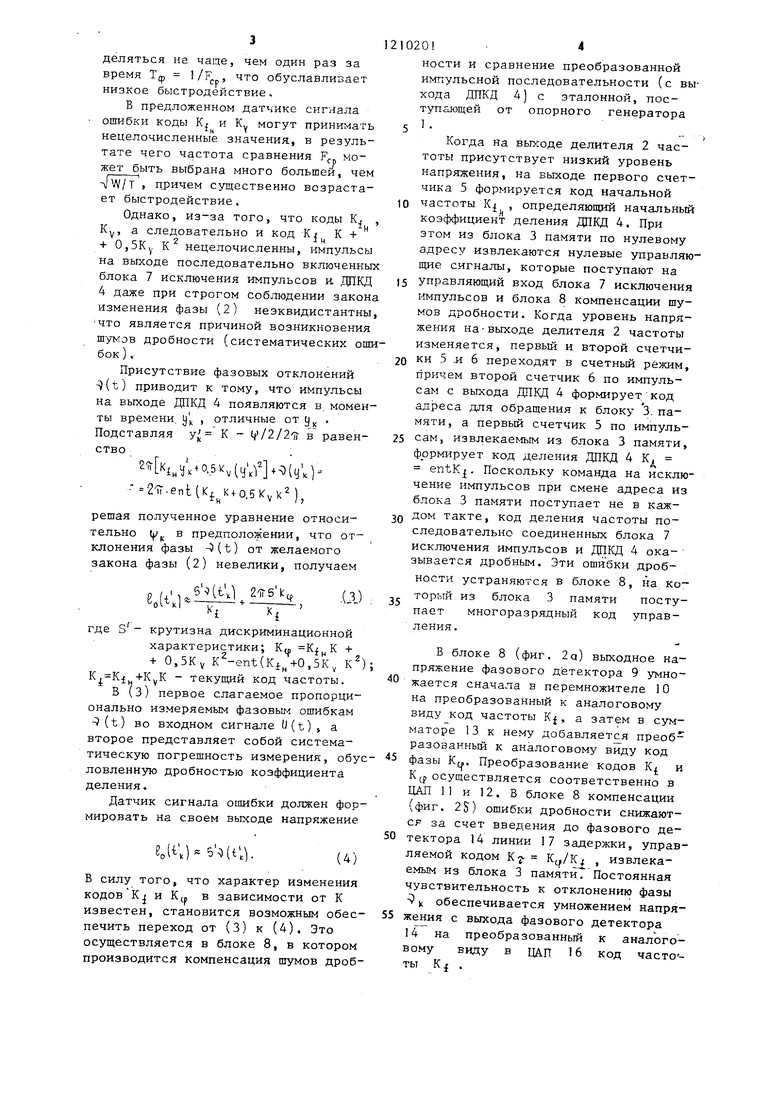

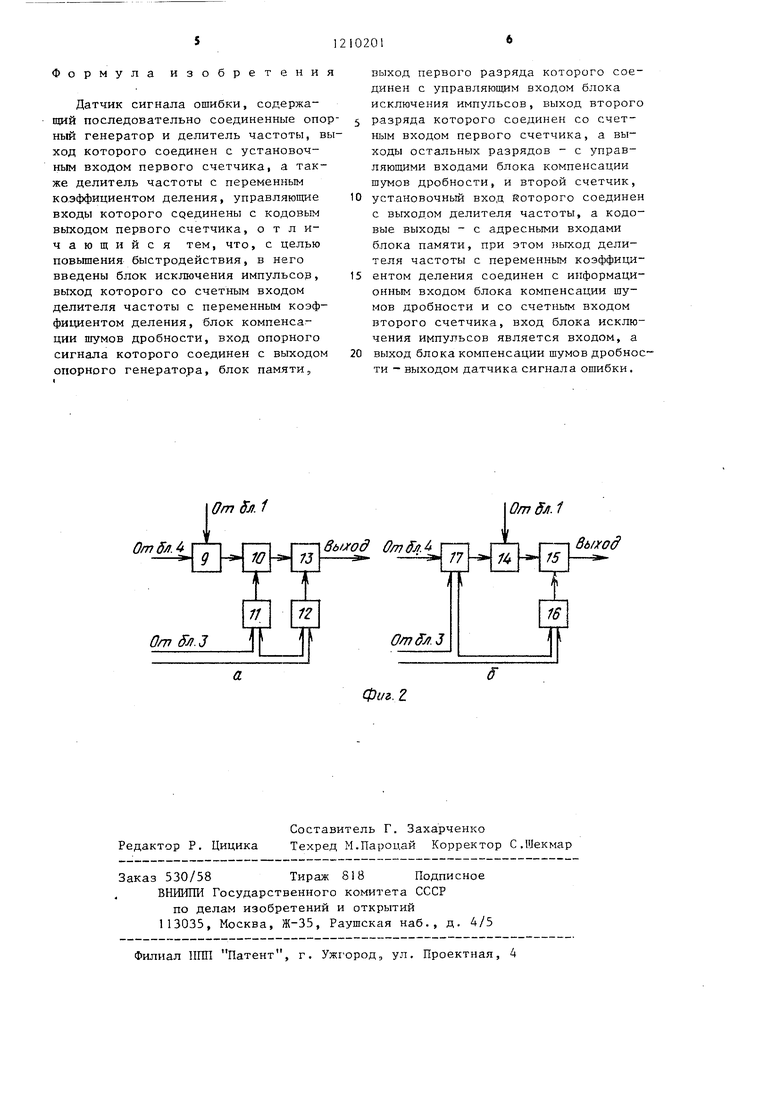

На фиг. 1 представлена структурна схема предложенного датчика сигнала ошибки; на фиг . 2а и 2 -примеры выполнения блока компенсации шумов дробности.

Датчик сигнала ошибки содержит .опорный генератор 1, делитель 2 частоты, блок 3 памяти, делитель частоты с переменным коэффициентом деления (ДПКД) 4, первый счетчик 5, второй счетчик 6, блок 7 исключения импульсов , блок 8 компенсации шумов дробности.

, Блок 8 компенсации шумов дробности согласно фиг 2 а содержит, фазовый детектор 9, перемножитель 10, цифро- аналоговые преобразователи. (ЦАП) 11 и 12 и сумматор 13 и согласно фиг. 2 - фазовый детектор 1А, перемножитель 15, ЦАП I6 и линию 17 задержки.

Датчик сигнала ошибки ра.ботает следующим образом.

На вход измерителя сигнала ошибки поступает сигнал вида

U(t)Ll6in 0(ih(t (1)

где (t) - отклонение фазы от требуемого закона ее изменения О (t), которое необходимо на выходе датчика сигнала ошибки. В частном случаев когда закон изменения частоты входного сигнала линейный, т.е.

.wit) 2 niH + Ui),

где f., - начальная частота ЛЧМ сиг-

п

нала; v v/T - скорость изменения частоты; w - девиация частоты; Т - длительность линейно-частотно-модулированного (ЛЧМ) сигнала, требуемая фаза имеет вид

9(y) 2 «(%ijio,,y ), (2) 1„ / i,p

к J 1 J I t

- начальный коэффициент деления ДПКД 4;

K.W/CTF ) - код скорости частотной модуляции ЧМ;

210201

р

- нормированное

время; - частота сравнения , на которой

происходит преобразование ЛЧМ сигнала (на частоте FJ, работает входящий в

блок 8 компенсации шумов дробности фазовый детектор 9 (14). Текущий коэффициент деления К., вычисляемьм в соответствии с выражением

(y..9ei/- 0,5K,K - (к-0 )-о,5 Ку (км) ,

где К 0,1, 2,..,, опредео1яет моменты Y|, появления импульсов на выходе последовательно включенных блока 7 исключения импульсов и ДПКД 4. Значения У в соответствии с формулой (2) находятся из уравнения

)€j LjK + o,5Kyij,--en-L(fc +0,5 Kyk).

Здесь и далее ent(.) означает выделение целой части числа. Фаза (2) входного сигнала U (t) в моменты времени кратна 2 и связана с 0 , J неравенством

e60(K)-0i;t. 21Г,

Знак равенства соответствует случаю, когда э& К1-0,5Ку1 целое, число для любых значений К., При этом импульсы на выходе последовательно включенных блока 7 исключения импульсов и ДПКД 4. следуют через промежутки времени, равные периоду Т 1/Р.,, следования импульсов в выхода опорного генератора 1.

Именно этот случай при К.0 соответствует режиму вьщеления сигнала ошибки, при котором преобразование входного ЛЧМ сигнала на частоту F

Cf

осуществляется посредством деления частоты ЛЧМ сигнала на целочисленный коэффициент деления К,, который от выборки к выборке меняется на целое число единиц (обычно шаг коэф- фициента деления равен единице). При режиме с целочисленным коэффициентом деления частота сравнения РГГ, 6 W/T и сигнал ошибки может выделиться не чаще, чем один раз за время Тф 1 /FJ, , что обуславливает низкое быстродействие.

В предложенном датчике сигнала ошибки коды Кг и К., могут принимать

И

нецелочисленные значения, в результате чего частота сравнения F,-. может быть выбрана много большей, чем fw/Vj причем существенно возрастает быстродействие.

Однако, из-за того, что коды К,

у, а следовательно и код K,f К +

К

+ 0,5Ку К нецелочисленны, импульсы на выходе последовательно включенны блока 7 исключения импульсов и. ДПКД 4 даже при строгом соблюдении закон изменения фазы (2) неэквидистантны ЧТО является причиной возникновения шумов дробности (систематических ошбок ).

Присутствие фазовых отклонений (t) приводит к тому, что импульсы на выходе ДПКД 4 появляются в моменты времени, , отличные от д, . Подставляя К - (/2/2 /г в равенство (У Л(У 0

SlT.entlK K+o.), решая полученное уравнение относительно у в предположении, что отклонения фазы -5(t) от желаемого закона фазы (2) невелики, получаем

где S

Ч i крутизна дискриминационной

характеристики; Kg, К К +

. -. 7 ./..

.2ч

+ 0,5Kv К -ent(,5K К) К ,Kf i -t-КуК - текушдй код частоты.

В (З) первое слагаемое пропорционально измеряемым фазовьм ошибкам -(t) во входном сигнале (J(t), а второе представляет собой систематическую погрешность измерения, обусловленную дробностью коэффициента деления.

Датчик сигнала оЕПибки должен формировать на своем выходе напряжение

е,к;)« 6(t;). (4)

в силу того, что характер изменения кодов К.{ и K(j, в зависимости от К известен, становится возможным обеспечить переход от (3) к (4). Это осуществляется в блоке 8, в котором производится компенсация шумов дроб1020

ности и сравнение преобразованной импульсной последовательности (с выхода ДГГКД 4) с эталонной, пос- тупаюш;ей от опорного генератора

5 1.

Когда На выходе делителя 2 частоты присутствует низкий уровень напряжения, на выходе первого счетчика 5 формируется код начальной

10 частоты K , определяющий начальный коэффициент деления ДПКД 4. При этом из блока 3 памяти по нулевому адресу извлекаются нулевые управляющие сигналы, которые поступают на

15 управляющий вход блока 7 исключения импульсов и блока 8 компенсации шумов дробности. Когда уровень напряжения на-выходе делителя 2 частоты изменяется, первый и второй счетчи20 ки 5 .и 6 переходят в счетный режим, причем второй счетчик 6 по импульсам с выхода ДПКД 4 формирует код адреса для обращения к блоку 3, памяти, а первый счетчик 5 по импуль25 сам, извлекаемым из блока 3 памяти, формирует код деления ДПКД 4 Кд entK. Поскольку команда на исключение импульсов при смене адреса из блока 3 памяти поступает не в каж3Q дом такте, код деления частоты последовательно соединенных блока 7 исключения импульсов и ДПКД 4 ока- зывается дробньм. Эти ошибки дробности устраняются в блоке 8, на который из блока 3 памяти поступает многоразрядный код управления.

35

В блоке 8 (фиг. 2q) выходное напряжение фазового детектора 9 умно40 жается сначала в перемножителе 10 на преобразованный к аналоговому виду код частоты К, а затем в сумматоре 13 к нему добавляется преобразованный к аналоговому виду код

45 фазы- К(. Преобразование кодов К и К ц, осуществляется соответственно в ЦАП 11 и 12. В блоке 8 компенсации (фиг. 25) ошибки дробности снижаются за счет введения до фазового де50 тектора 14 линии 17 задержки, управляемой кодом KT- , извлекаемым из блока 3 памятиТ Постоянная чувствительность к отклонению фазы к обеспечивается умножением напря55 жения с выхода фазового детектора 14 на преобразованный к аналоговому виду в ЦАП 16 код часто - ты К.{ .

Формула изобретения

Датчик сигнала ошибки, содержащий последовательно соединенные опорный генератор и делитель частоты, выход которого соединен с установочным входом первого счетчика, а также делитель частоты с переменным коэффициентом деления, управляющие входы которого срединены с кодовым выходом первого счетчика, отличающийся тем, что, с целью повышения быстродействия, в него введены блок исключения импульсов, выход которого со счетным входом делителя частоты с переменным коэф- фи1Ц1ентом деления, блок компенсации шумов дробности, вход опорного сигнала которого соединен с выходом опорного генератора, блок памяти.

выход первого разряда которого соединен с управляющим входом блока исключения импульсов, выход второго разряда которого соединен со счетным входом первого счетчика, а выходы остальных разрядов - с управляющими входами блока компенсации шумов дробности, и второй счетчик,

установочный вход которого соединен с выходом делителя частоты, а кодовые выходы - с адресными входами блока памяти, при этом })ьгх:од делителя частоты с переменным коэффициентом деления соединен с информационным входом блока компенсации шумов дробности и со счетным входом второго счетчика, вход блока исключения импульсов является входом, а

выход блока компенсации шумов дробности - выходом датчика сигнала ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Синтезатор частот | 1986 |

|

SU1376242A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

Изобретение м.б. использовано в прецизионных генераторах сигналов с частотной модуляцией в радиолокационных и связных системах, в акус- тоэлектронных фурье-продессорах. Цель изобретения - повышение быстродействия. Устройство содержит опор- ный генератор 1, делитель частоты 2, блок пaмяtи (БП) 3, делитель частоты с переменным коэффициентом деления (ДПКД) 4, два счетчика 5, 6, блок исключения импульсов 7 и блок кo meнcaции шумов добротности (БКПЩ) 8. Когда уровень напряжения на выходе делителя частоты 2 изменяется, счетчики 5, 6 переходят в счетный режим, счетчик 6 по импульсам с выхода ДПКД 4 формирует код адреса для обращения в БП 3, а счетчик 5 по импульсам, извлекаемым из БП 3, формирует код деления ДПКД 4 K.ent К. Поскольку команда на исключение импульсов при смене адреса из БП 3 поступает не в каждом такте, код деления частоты последовательно соединенных блока исключения импульсов 7 и ДПКД 4 оказывается дробным. Эти ошибки дробности устраняются в БКШД 8, на который из БП 3 поступает многоразрядный код управления. Приведены два примера вьтолнения БКИЩ 8. ,2 ил. о (Л С о to фиг.1

0in 5л.1

ОтблЛ

8b/jfod

вб/)од

.З

Редактор Р. Цицика

Составитель Г. Захарченко

Техред М.Пароцай Корректор С.Шекмар

Заказ 530/58 Тираж 818 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,

фиг. Z

| Устройство для снятия характеристик электронной настройки широкополосных генераторов | 1957 |

|

SU113346A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Генератор с линейной частотной модуляцией | 1976 |

|

SU641628A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-07—Публикация

1984-06-19—Подача