йены соответственно с третьим информационным входом первого коммутатора и вторым информационным входом первого коммутатора, третьим информационным входом второго коммутатора р -и строки матрицы, где р 1,.., n/Z, выходы первых..м -коммутаторов последней строки которой соединены с информационным входом блока подсчета количества единиц и нулей и с первым информационным входом выходного мультиплексора, второй информационный вход которого соединен с выходами (ti + 1)-ro и (пн-2)-го коммутаторов строк матрицы, входы дешифраторов которых соединены с выходом управляющего мультиплексора, третий и четвер гьш информационные входы выходного мультиплексора соединены соответственно с первым информацион- ньм входом выходного мультиплексора и выходом блока подсчета количества единиц и нулей, (2р-1)-й и 2р-й разряды второго информационного входа устройства соединены соответственно с первыми информационными входами (п + 1)-го и ()-го коммутаторов р -и строки матрицы, причем в матрице первьм информационный вход и -го коммутат ора каждой строки соединен с третьим информационным входом (J+2)-ro коммутатора той же строки. i 1-(n-l), гдй i 1,...,п-1, первый информационный вход h го коммутатора соединен с вторым информационным входом (()-го коммутатора, первый выход дешифратора каждой строки соединен с первыми управляющими входами коммутаторов с первого по п-й той же строки, второй выход де- 1ифратора каяодой строки соединен с вторыми управляющими входами первого и (h + O-ro коммутаторов той же строки, третий выход дешифратора каждой строки соединен с третьими управляющими входами коммутаторов кроме первого И (и+2)-го той же строки, чет- вертый выход дешифратора каждой стро -ки соединен с первым управляюнщм

Изобретение относится к автоматике и вычислительной технике и может быть использовходом (li + 1)-ro коммутатора той же строки, пятый выход дешифратора каждой строки соединен с первым управляющим входом п+2)-го коммутатора той же строки, шестой выход дешифратора каждой строки соединен с вторыми управляющими входами коммутаторов с второго по h -и той же строки, седьмой выход дешифратора каждой строки соединен с третьим управляющим входом первого коммутатора и вторым управляющим входом (п+2)-го коммутатора той же строки.

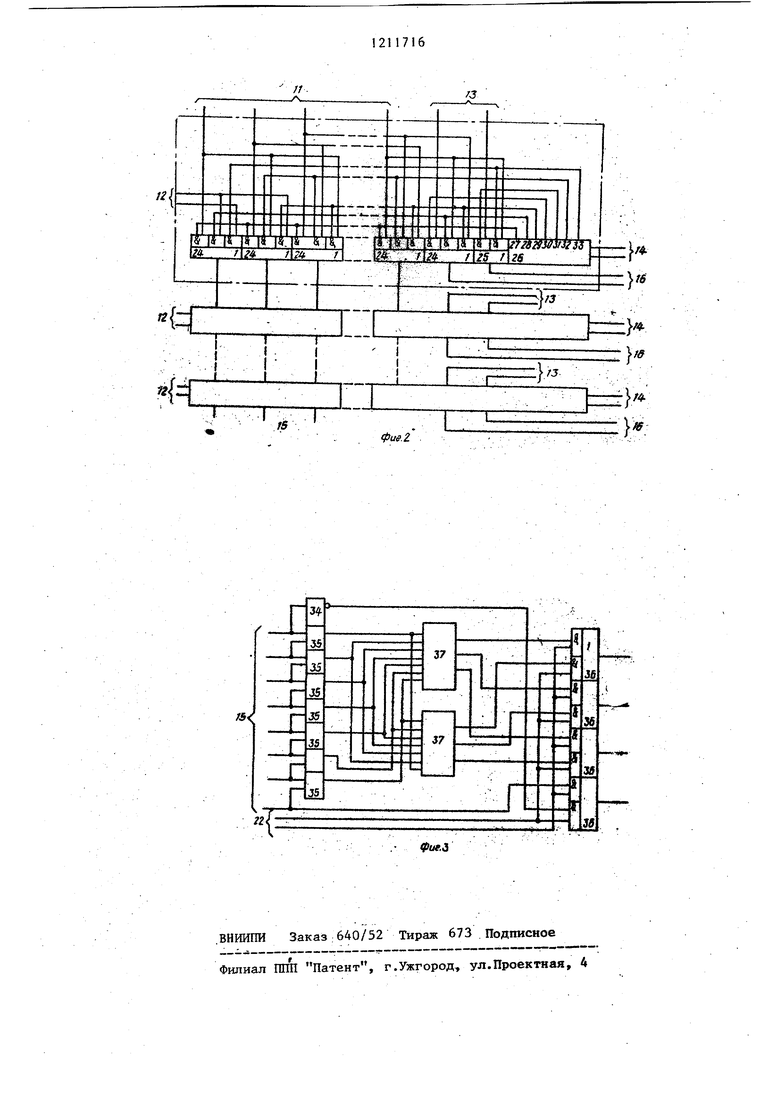

2. Устройство поп,1, отличающееся тем, что блок подсчета количества единиц и нулей содержит группу элементов ИСКЛЮЧАЮЩЕЕ ШШ, группу коммутаторов, элемент НЕ и два шифратора, причем j -и разряд информационного входа блока подсчёта количества единиц и нулей соединен с первым входом j -го и вторым входом (j-l)-ro элемента ИСКШОЧАЮЩЕЕ ШШ группы, где 1,. ..,п-1, выход j -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединен с j -м входом первого и (n-j)-M входом второго шифраторов, выходы которых соединены соответственно с первыми и вторыми информационными входами коммутаторов, кроме последнего коммутатора группы, управляющие входы коммутаторов группы соединены с соответствзпощими .разрядами управляющего входа блока подсчета количества единиц и нулей, выход которого соединен с выходами коммутаторов группы, первый информационный вход последнего коммутатора группы соединен с вторым входом последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы и с П -м разрядом информационного входа блока подсчета количества единиц и пулей, второй информационный вход последнего коммутато- -ра группы соединен через элемент НЕ с первым разрядом информационного входа блока подсчета количества единиц и нулей.

вано при создании вычислительных средств высокой производительности.

Целью изобретения является расширение функциональных возможностей за счет выполнения операций восстановления и подсчета количества единиц и нулей.

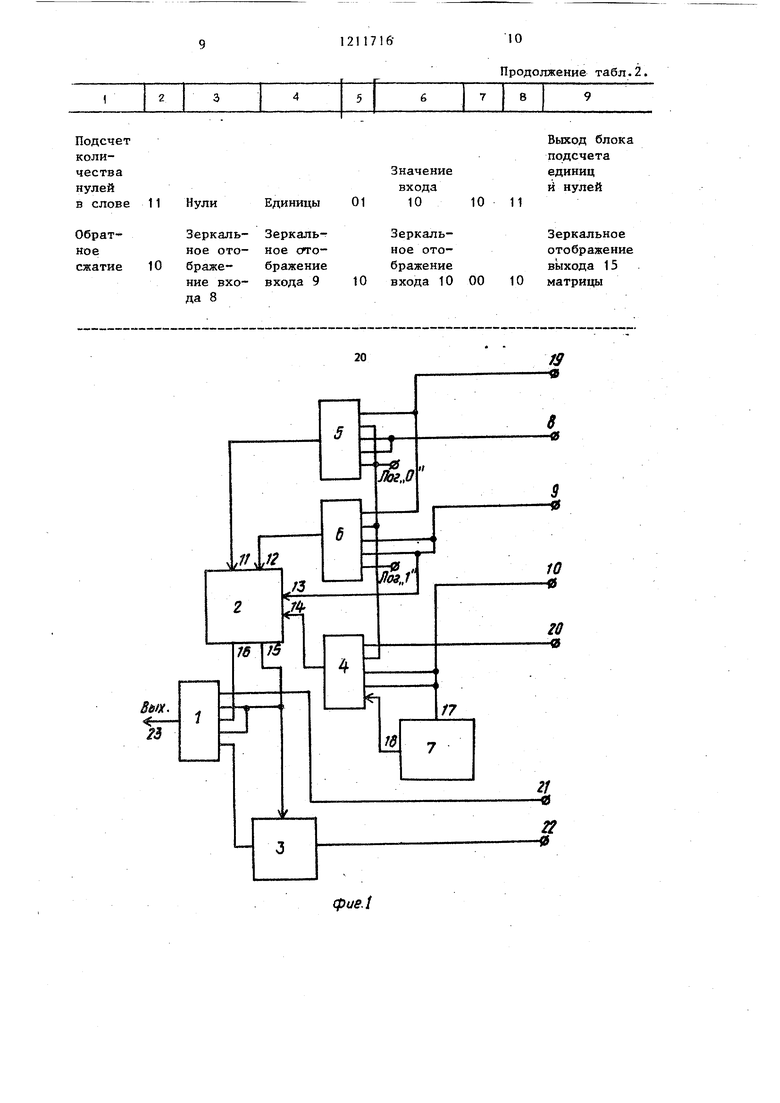

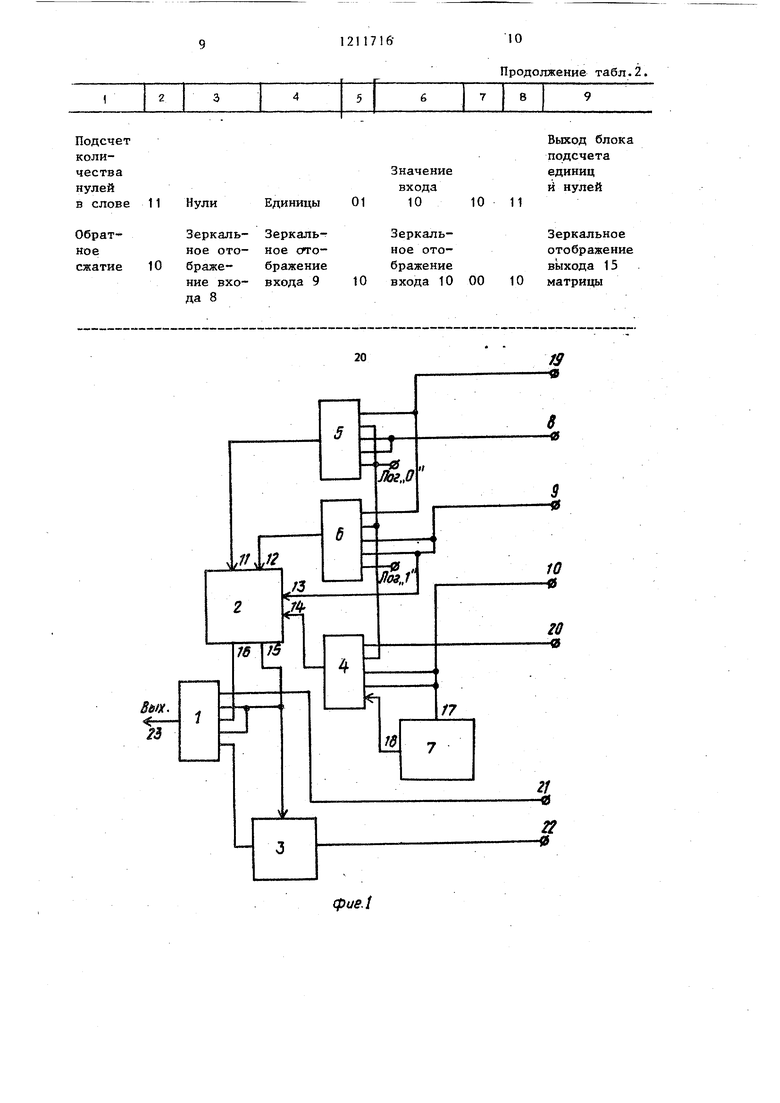

На фиг.1 представлена блок-схема устройства для уплотнения информации; на фиг.2 - функциональная схема матрицы преобразований; на фиг.З - схема блока подсчета количества единиц и нулей.

Устройство для уплотнения информации содержит выходной мультиплексор 1 , матрицу 2j блок 3 подсчета количества единиц и нулей, мультиплексоры 4, 5, 6, преобразователь 7 двоичного кода, информационные входы 8,9 устройства, вход 10 маски устройства, информационные входы 11, 12, 13 матрицы, управляющий вход 14 матрицы, выходы 15, 16 матрицы, вход 17 и выход 18 преобразователя двоичного кода, входы 19-22 задания режима устройства, выход 23 устройства.

Матрица 2 (фиг.2) содержит коммутаторы 24 и 25, дешифраторы 26, выходы 27-33 дешифратора 26.

Блок 3 подсчета количества единиц и нулей содержит элемент НЕ 34, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 35, группу коммутаторов 36, шифраторы 37.

Преобразователь 7 двоичного кода в унитарньА код преобразует двоичный код числа сдвигов, поступающее на вход 17, в число единиц, соответствующее этому коду и поступающее на выход 18.

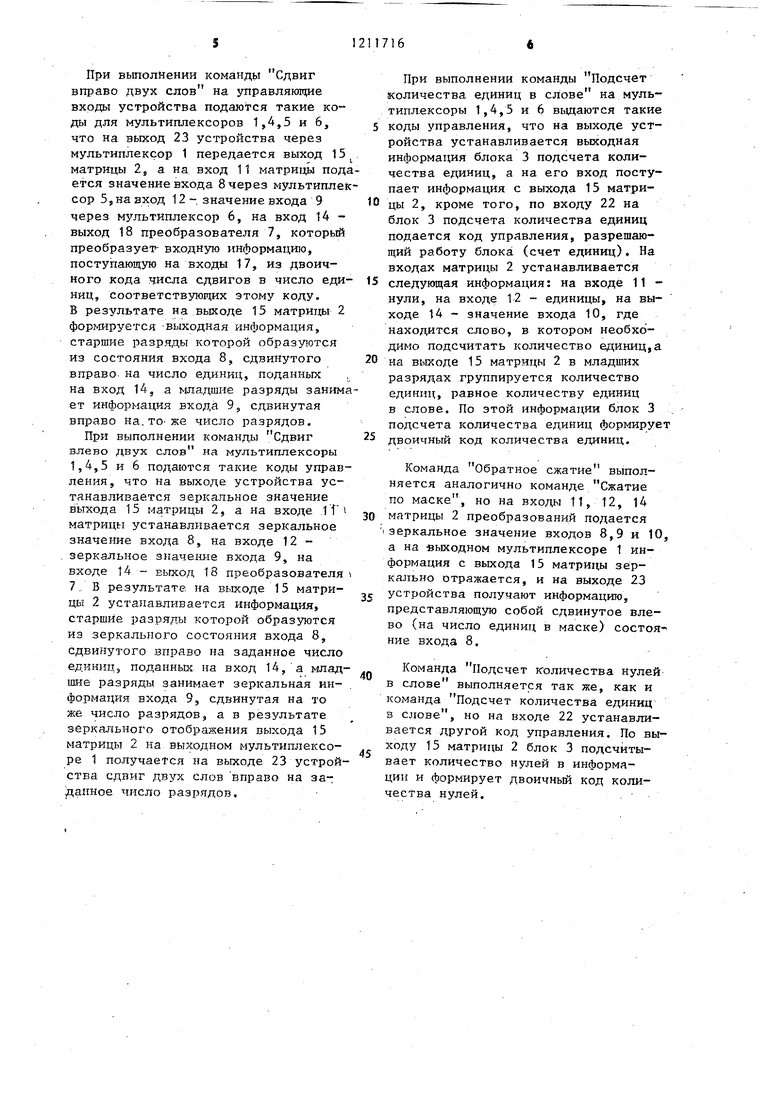

Дешифратор 26 работает .в соответствии с табл.1.

Устройство для уплотнения информации работает следующим образом.

В исходном состоянии на входы 19- 21 устройства подаются логические нули, которые поступают на управляющие входы мультиплексоров 1,4,5 и 6. При подаче нулей на управляющие входы мультиплексоров 4,5 и 6 на входы матрицы 2 подаются нули и на выходах матрицы 2 устанавливаются состояния логических нулей, которые передаются на мультиплексор 1, на выходах которого также устанавливаются состояния логических нулей.

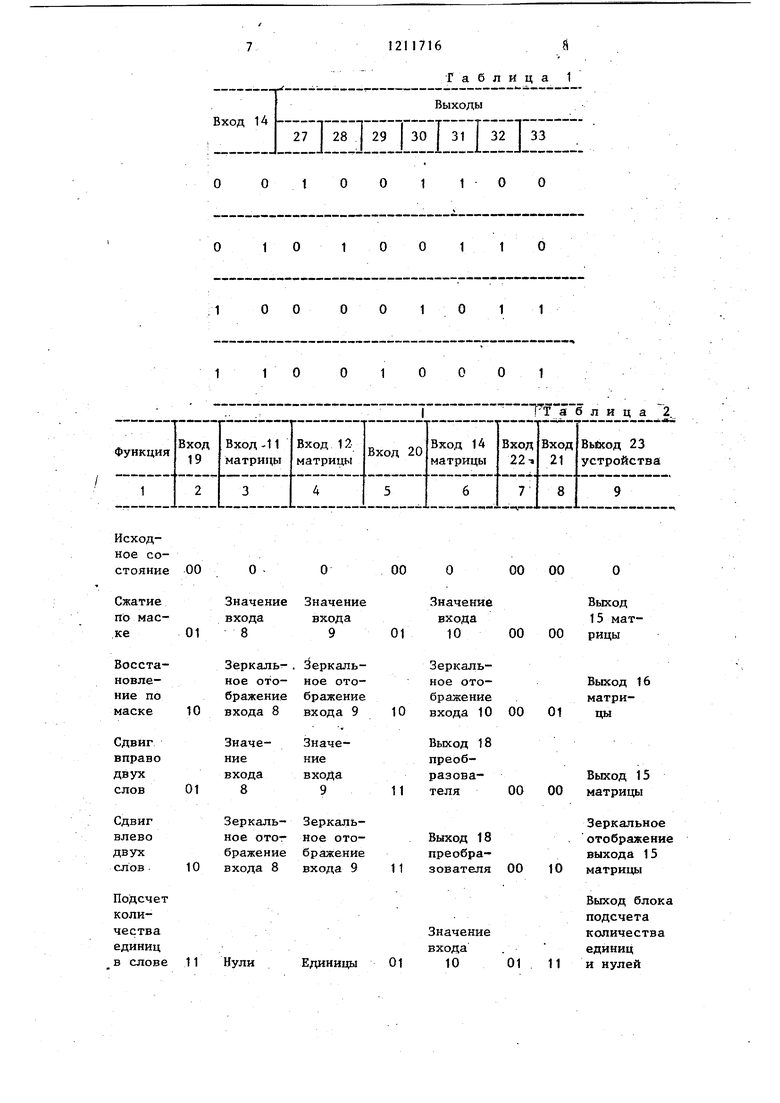

Перечень операций, выполняемых устройством, и соответствующие значения входов 19-22 задания режима приведены в табл.2.

2117164

При выполнении команды Сжатие по маске на управляющие входы устройства для мультиплексоров 1,4,5 и 6 (см. табл.2) подаются такие коды,

с что на вход 11 матрицы 2 выдается содержимое входа 8, на вход 12 матрицы вьщается содержимое входа 9, а на вкод 14 - содержимое входа Ю (на вход 13 матрицы 2 при выполнении

10 любой команды вьщается содержимое входа 9). На выходной мультиплексор 1 подается код, обеспечивающий подключение выхода 15 матрицы 2 к выходу 23 устройства. На выходе 15

)5 матрицы 2 в младших разрядах формируются состояния разрядов входа 12, соответствукщие маске, поданной на вход 14. Формирование производится справа налево следуюршм образом: в

20 нулевой разряд помещается состояние разряда входа 12, соответствующего второй единице в маске (вход l4) и так далее до последней единицы в маске входа 14, в остальные разря25 ды (старшие) выхода 15 помещается сдвинутая влево (на число единиц, содержащихся в маске) информация, поступившая на вход 11 матрицы 2. Такш- образом, в результате выполнения операции Сжатие по маске на выходе устройства появляется информация, представляющая собой- сдвинутое вправо (на число единиц в маске) состояние входа 8, и информация входа 9, выбранная по маске

35 входа 10.

При выполнении команды Восстановление по маске на управляющие входы устройства подаются коды для мультиплексоров 1,4,5 и 6 (см. табл.2)

так, что на вькоде 29 устройства появляется состояние выхода 16 матрицы 2, на вход 11 которой подается зеркальное значение входа 8, на вход 12 - зеркальное значение вхо да 9, а на вход 14 - зеркальное

значение входа 10. В резух ьтате преобразований на выходе 16 матрицы формируется следующая информация, состояние нулевого разряда входа 8

50 располагается по номеру младшей единицы маски (вход 14), состояние первого разряда входа 8 располагает-. ся по номеру следующей единицы маски и так далее, а остальные разря55 ды, не присутствующие в маске, заполняются соответствз ющими разрядами информации входа 9, поступающей на вход 13 матрицы.

При выполнении команды Сдвиг вправо двух слов на управляющие входы устройства подаются такие коды для мультиплексоров 1,,5 и 6, что на выход 23 устройства через мультиплексор 1 передается выход 15 матрицы 2, а на вход 11 матрИ1ды подается значение входа 8 через мультиплексор 5 5 на вход 12 - значение входа 9 через мультиплексор 6, на вход 14 - выход 18 преобразователя 7, который преобразует- вход ную информацию, поступающую на входы 17, из двоичного кода числа сдвигов в число единиц, соответствующих этому коду, В результате на выходе 15 матрицы 2 фop IИpyeтcя -выходная информация, старшие разряды которой образу отся из состояния входа 8, сдвинутого вправо, на число единиц, поданных , на вход 14, а maдшиe разряды занимает информация входа 9,, сдвинутая вправо на.то-же число разрядов.

При выполнении команды Сдвиг влево двух слов на мультиплексоры 1,4,5 и 6 подаются такие коды управления, что на выходе устройства устанавливается зеркальное значение выхода 15 матрицы 2, а на входе .1Т матрицы устанавливается зеркальное значение входа 8, на входе 12 - зеркальное значешш входа 9, на входе {4 - 18 преобразователя 7. В результате на вв 1ходе 15 матрицы 2 устанавлр вается информация, старшие разряды которой образуются из зеркального состояния входа 8, сдвинутого вправо на заданное число единиц, поданных на вход 14, а младшие разряды занимает зеркальная ин- . формация входа 9, сдвинутая на то же число разрядов, а в результате зеркального отображения выхода 15 матрицы 2 на выходном мультиплексоре 1 получается на выходе 23 устройства сдвиг двух слов вправо на за- цапное число разрядов.

При выполнении команды Подсчет количества единиц в слове на муль типл.ексоры 1,4,5 и 6 выдаются такие 5 коды управления, что на выходе устройства устанавливается выходная информация блока 3 подсчета количества единиц, а на его вход поступает информация с выхода 15 матри0 цы 2, кроме того, по входу 22 на блок 3 подсчета количества единиц подается код управления, разрешающий работу блока (счет единиц). На входах матрицы 2 устанавливается

5 следующая информация: на входе 11 - нули, на входе 12 - единицы, на выходе 14 - значение входа 10, где находится слово, в котором необхЬ- димо подсчитать количество единиц,а

0 на выходе 15 матрицы 2 в младших разрядах группируется количество единиц, равное количеству единиц в слове. По этой информации блок 3 , подсчета количества единиц формирует

двоичный код количества единиц.

Команда Обратное сжатие выполняется аналогично команде Сжатие по маске, но на входы 11, 12, 14

0 матрицы 2 преобразований подается 1 зеркальное значение входов 8,9 и 10, а на выходном мультиплексоре 1 информация с выхода 15 матрицы зеркально отражается, и на выходе 23

устройства получают информацию,

представляющую собой сдвинутое влево (на число единиц в маске) состоя- ние входа 8.

Команда Подсчет количества нулей в слове выполняется так же, как и команда Подсчет количества единиц в слове, но на входе 22 устанавливается другой код управления. По вы- - ходу 15 матрицы 2 блок 3 подсчитывает количество нулей в информации и формирует двоичный код количества нулей.

О01001100

О1010 О 11 О

100О О 10 11

00

О

О

01

10

01

10

ЗначениеЗначение входа входа 8 9

Зеркаль- .Зеркальное ото-ное отображениебражениевхода 8входа 9

Значениевхода 8

Значениевхода 9

Зеркаль-Зеркальное отогное отображениебражениевхода 8входа 9

11

Нули

Единицы

1211716а

г а б л и ц а 1

лица 2.

0

1

0

1

О

00 00

Значение входа 10 00

Зеркальное отображениевхода 10 00

Выход 18 преобразователя 00

Выход 18

преобра1 зователя 00

1

Значение входа

10 01

00

01

О

Выход 15 матрицы

Выход 16 матрицы

Выход 15 00 матрицы

Зеркальное . отображение выхода 15

10матрицы

Выход блока подсчета количества единиц

11и нулей

11

10

Нули

Зеркальное отображение входа 8

Единицы 01

Зеркаль ное отображениевхода 9 10

,/л

,//

лз

f6 1/5

Втх.

Продолжение табл.2,

10 11

Выход блока подсчета единиц и нулей

00

Зеркальное отображение выхода 15 10 матрицы

20

/ -«

1.1

3

-0

т.г

10 -0

го

-0

17

22 0

И /

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига | 1984 |

|

SU1187160A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Пульт учащегося для устройства обучения языкам | 1985 |

|

SU1354235A1 |

| Устройство для уплотнения информации | 1982 |

|

SU1032450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига информации | 1975 |

|

SU643864A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-12—Подача