Изобретение относится к вычислительной технике, в частности к устройствам управления вычислительными комплексами.

Целью изобретения является повышение быстродействия.

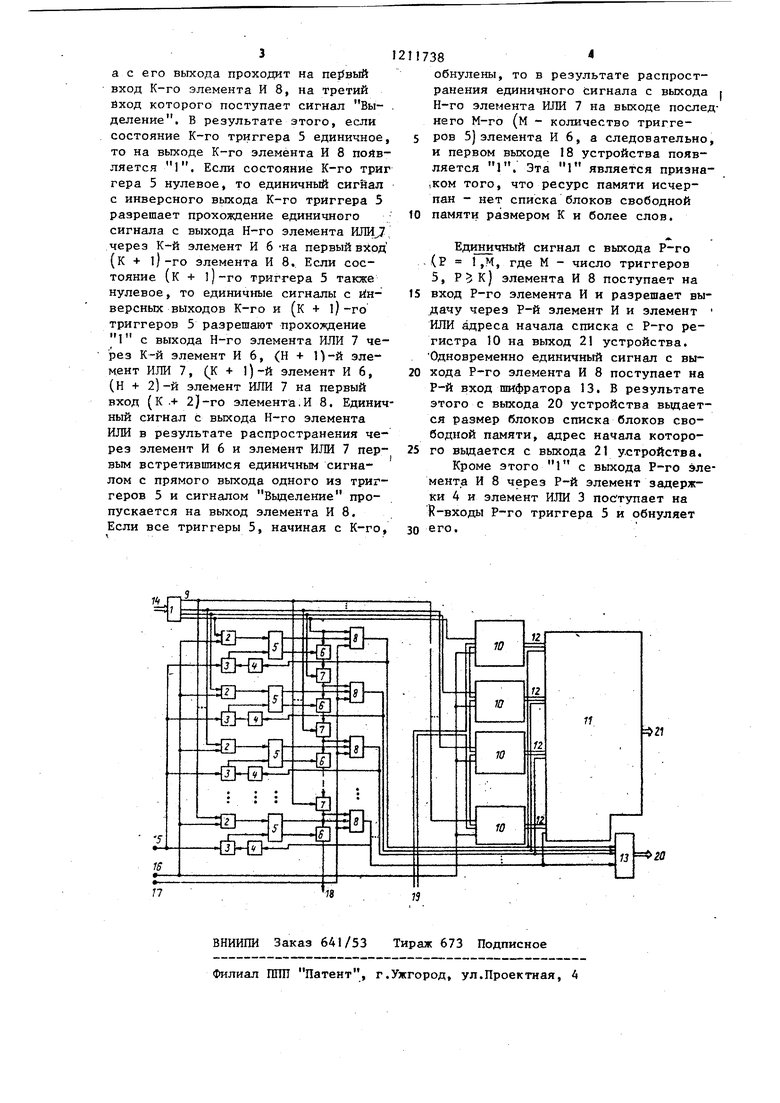

На чертеже изображена функциональная схема устройства.

Устройство содержит дешифратор 1, группу элементов И 2, группу элементов ИЛИ 3, группу элементов 4 задержки- группу триггеров 5 готовности, группу элементов И 6, группу элементов ИЛИ 7, группу элементов И 8, выходы 9 дешифратора группу регистров 10, .коммутатор 11, информационные входы 12 коммутатора, шифратор 13, входы размера элементов массива 14, сброса 15, признака режима записи адреса 16, признака режима чтения адреса устройства 17, выход признака от сутствия требуемого массива 18 устройства, вход начального адреса массива 19 устройства, выходы размера элементов массива 20 устройства, начального адреса массива 21 устройства.

Устройство работает следующим образом. ,

Предполагается, что распределяемая память организована в виде массивов (списков), элементы которых имеют размер, равный К слов (к 1,2,...). Группа регистров 10 предназначена для хранения начальных адресов списков блоков свободной памяти. Первый регистр 10 хранит a- чальный адрес списка свободных блоков из одного слова, второй - из двух, третий - из трех, К-й - из К слов (К 1,М, где М - число регистров 10). Все блоки, размеры которых больше М, записаны в список, начальный адрес которого хранится в М-ом регистре 10.

Группа триггеров 5 готовности служит для определения готовности К-го списка к работе. Если содержимое К-го триггера 6 единичное, это означает, что К-й регистр 10 содержит адрес начала списка свободных блоков памяти размеров К слов каждый Нулевое состояние К-го триггера 5 означает, что в К-ом регистре 10 отсутствует информация - он свободен. Количество триггеров 5 готовности равно количеству регистров 10. Элемент 4 задержки служит для задержки

117382

прохождения сигнала с выхода К-го элемента И 8 через К-й элемент ИЛИ 3 на К-вход К-го триггера 5 на время, необходимое для считывания адреса

5 списка из К-го регистра 10 и выдачи его содержимого из устройства через выход 21 устройства.

Устройство работает в режимах выделения чтения и возврата записи

10 адреса списка свободных блоков памяти. Рассмотрим работу устройства в каждом из режимов.

Перед началом работы на вход 15 устройства подается единичный сиг15 нал, который поступает через элементы ИЛИ 3 на R-входы триггеров 5 и обнуляет их.

В режиме возврата адреса списка свободных блоков памяти на вход 16

20 устройства подается сигнал Возврат и одновременно с ним на вход 14 устройства поступает размер блока (элементов) -списка, а на вход 19 - адрес начала списка. После поступления на

25 дешифратор 1 размера, равного

К (К 1,N, где М - количество триггеров 5), на его выходе на К-й шине появляется единичный сигнал, который поступает на первый вход К-го элемен30 та И 2. Прохождение этого сигнала . на 5-вход К-го триггера 5 разрешается сигналом Возврат, поступающим на вторые входы элементов И 2, в ре-, зультате чего К-й триггер 5 взводится в единичное состояние. Единичный сигнал с К-го выхода дешифратора поступает также на первый вход К-го элемента И 9. В результате этот сигнал вместе с поступающим на элемен.. ты И 9 сигналом Возврат разрешает

чи

Прохождение начального адреса списка свободных блоков памяти с входа 19 устройства и разрешает запись в К-й регистр 10-.

45 В режиме вьщеления адреса списка свободных блоков памяти на вход I7 устройства подается сигнал Выделение и одновременно с ним на вход 14 устройства поступает требуемый

50 размер блоков (элементов) списка блоков свободной памяти. При поступлении на дешифратор 1 размера, равного К, на его выходе на К-й шине появляется единичный сигнал, посту55 пающий на второй вход Н-го (Н K-I) элемента ИЛИ 7 Сигнал с первого выхода дешифратора 1 поступает на первые входы первых элементов И 8 и 6,

35

а с его выхода проходит на первый вход К-го элемента И 8, на третий Вход которого поступает сигнал Выделение. В результате этого, если состояние К-го триггера 5 единичное, то на вькоде К-го элемента И 8 пойв- ляется 1. Если состояние К-го триг гера 5 нулевое, то единичный сигнал с инверсного выхода К-го триггера 5 разрешает прохождение единичного сигнала с выхода Н-го элемента HJlHJf через К-й элемент И 6 -на первый вход {к l)-го элемента И 8. Если состояние (к + l)-ro триггера 5 также нулевое, то единичные сигналы с инверсных выходов К-го и (к + l)-го триггеров 5 разрешают npoxojfweHHe 1 с выхода Н-го элемента ИЛИ 7 через К-й элемент И 6, (Н + П-й элемент ИЛИ 7, (К + 1)-й элемент И 6, (Н + 2)-и элемент ИЛИ 7 на первый вход (К .+ 2)-го элемента.И 8, Единичный сигнал с выхода Н-го элемента ИЛИ в результате распространения через элемент И 6 и элемент ИЛИ 7 первым встретившимся единичным сигналом с прямого выхода одного из триггеров 5 и сигналом Выделение пропускается на выход элемента И 8. Если все триггеры 5, начиная с К-го,

211738

обнулены, то в результате распространения единичного сигнала с выхода | Н-го элемента ИЛИ 7 на выходе последнего М-го (М - количество тригге- 5 ров 5)элемента И 6, а следовательно, и первом выходе 18 устройства появляется 1. Эта 1 является приэна- ,ком того, что ресурс памяти исчерпан - нет списка блоков свободной 10 памяти размером К и более слов.

Единичный сигнал с выхода Р-го (Р 1,М, где М - число триггеров 5, Р5К) элемента И 8 поступает на

15 вход Р-го элемента И и разрешает выдачу через Р-й элемент И и элемент ИЛИ адреса начала списка с Р-го регистра 10 на выход 21 устройства. Одновременно единичный сигнал с вы20 хода Р-го элемента И 8 поступает на Р-й вход шифратора 13. В результате этого с выхода 20 устройства выдается размер блоков списка блоков свободной памяти, адрес начала которо25 го вьщается с выхода 21 устройства.

Кроме этого 1 с выхода Р-го элемента И 8 через Р-й элемент задержки 4 и элемент ИЛИ 3 поступает на R-входы Р-го триггера 5 и обнуляет

30 его.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации оперативной памяти | 1986 |

|

SU1361566A1 |

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| Устройство для управления распределенной вычислительной системой | 1981 |

|

SU972509A1 |

| Устройство для адресации памяти | 1986 |

|

SU1328820A1 |

| Устройство для определения максимальных путей в графах | 1984 |

|

SU1280380A2 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для ввода информации | 1984 |

|

SU1259241A1 |

га

ВНИИПИ Заказ 641/53 Тираж 673 Подписное Филиал ШШ Патент, г.Ужгород, ул.Проектная, 4

| Устройство обмена | 1970 |

|

SU474006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-11—Подача