товым входом распределителя импульсов и первым входом элемента И, выход которого соединен с тактойым входом кольцевого регистра, выход первого разряда которого соединен с первым входом третьего элемента ИЛИ выход которого соединен с входами стробирования первого и второго блоков умножения и управляющим входом шестого коммутатора, вход которого соединен с выходом шестого блока памяти, адресный вход которого соединен с входом задания коэффициентов устройства, вход задания значений элементов единичной матрицы которого соединен с первым информационным входом второго блока умножения, вторые информационные входы первого и второго блоков умножения соединены соответственно с первым и вторым выходом шестого коммутатора, выходы певого и второго блоков умножения соединены со входами записи соответственно седьмого и восьмого блоков памяти, выходы которых соединены с первым и вторым информационными входами второго сумматора стробирующий вход и выход которого соединены соответственнд с выходом четвертого элемента ИЛИ и входом записи четвертого блока памяти, выход второго разряда кольцевого регистра соединен с первым четвертого элемента ИЛИ, выход третьего разряда Кольцевого регистра соединен с первы входом первого элемента ИЛИ и счетны входом счетчика, выход которого соеИзобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и однородных вычислительных структурах.

Целью изобретения является расширение класса решаемых задач за счет обеспечения нахождения обратной матрицы для матрицы со свойством

, ReA /А + (1) при увеличении быстродействия.

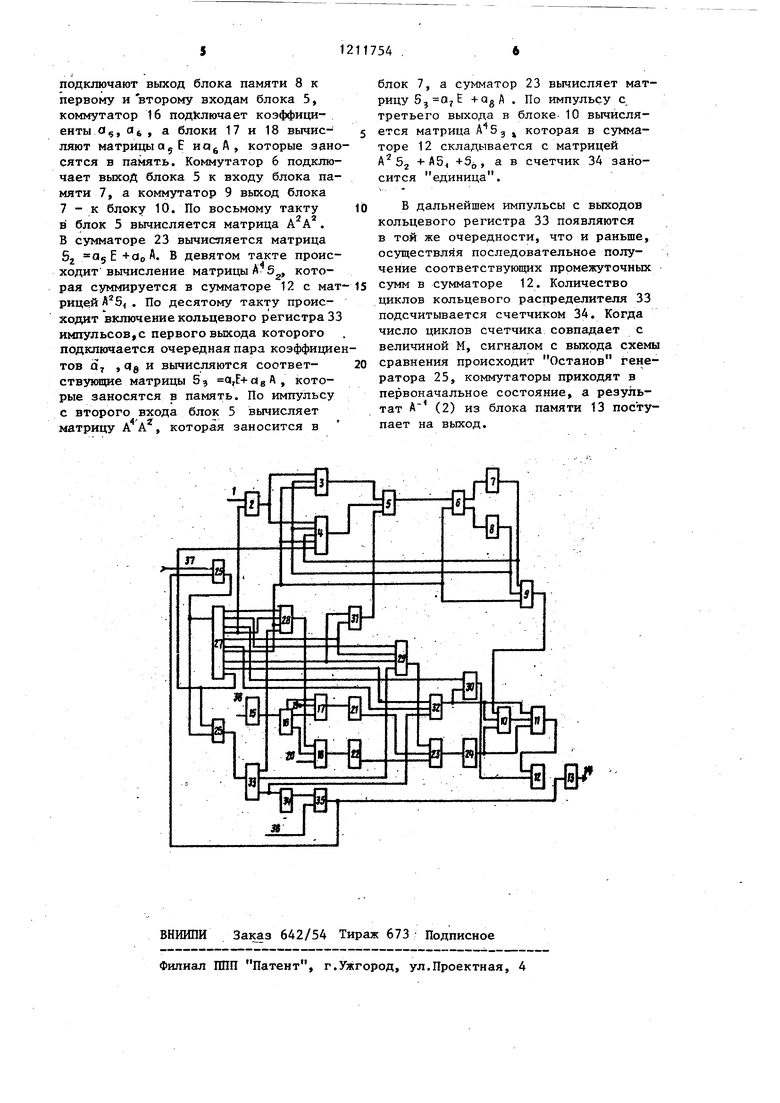

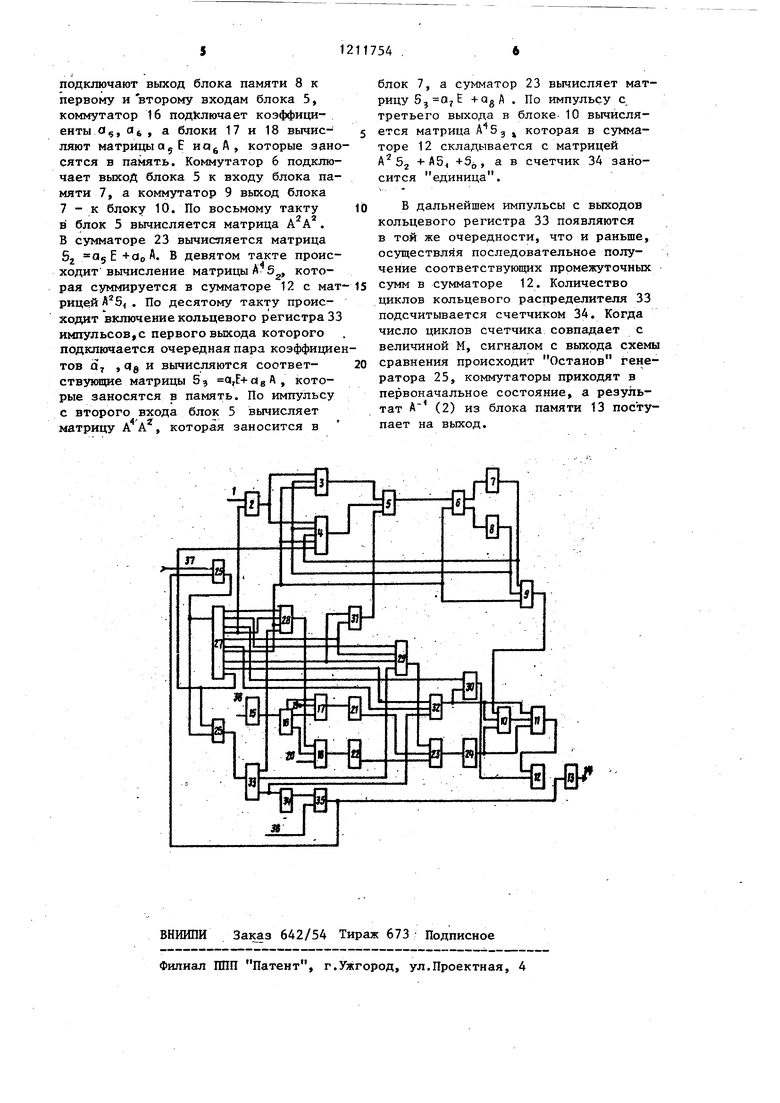

На чертеже представлена блок-схема устройства.

динен с первьпч входом схемы сравнения, второй вход которой соединен с входом задания числа циклов устройства, первьй, второй и третий выходы распределителя импульсов соединены со вторыми входами соответственно третьего, четвертого и второго элементов ИЛИ, четвертый выход распределителя импульсов соединен с входом разрешения записи первого блока памяти и третьим входом третьего элемента ИЛИ, пятьй выход распределителя импульсов соединен с первым входом пятого элемента -ИЛИ и с третьим входом четвертого элемента ИЛИ, шестой выход распределителя импульсов соединен со вторым входом второго элемента ИЛИ, седьмой выход распределителя импульсов соединен с четвертым входом третьего элемента ИЛИ, управляющими входами первого, третьего и четвертого коммутаторов и первым управляющим входом второго коммутатора, восьмой выход распределителя импульсов соединен с четвертым входом четвертого элемента ИЛИ и вторым входом пятого элемента ИЛИ, выход которого соединен со входом стробирования первого блока вычисления скалярного произведения, девятый выход распределителя импульсов соединен с третьим входом первого элемента ИЛИ, второй вход элемента И соединен с вторым управляющим входом второго коммутатора и с десятым выходом распределителя импульсов, выход пятого блока памяти соединен с выходом устройства.

Устройство содержит вход матрицы А 1, блок памяти 2, коммутаторы 3 и 4, блок 5 вычисления скалярного произведения 5, коммутатор 6, блоки памяти 7 и 8, коммутатор 9, блок 10 вычисления скалярного произведения, коммутатор 11, сумматор 12, блок памяти 13, вых од 14, блок памяти 15, коммутатор 16, блоки умножения 17

и 18, входы задания единичной 19 и исходной 20 матриц, блоки памяти 21 и 22, сум1-1атор 23, блок памяти 24, генератор импульсов 25, элемент И

26, ра спределитель импульсов 27, элементы ИЛИ 28-32, кольцевой регистр 33, счетчик 34, схему сравнения 35, вход задания числа циклов 36,. вход запуска 37, вход задания адреса коэффициентов 38.

В основу предлагаемого вычислительного устройства положен алгоритм вычисления обратной матрицы

А- Ме- Д

(2)

где матрица А удовлетворяет условию (1) .

Численный аналог (2) имеет вид

A- Je- Ji-j E-Ata -f- HrA f ,..clt:

«1 ., . fN К4.1

-2:HV | ZH)V, (3)

(КИ) 0

где Е - единичная матрица того же

размера, что и заданная матрица А , Л° Е ;

т- нечетное число. Дп.ина интервала интегрирования М и число членов ряда m при заданной точности вьгчисления б для проектируемого вычислительного устройства предварительно могут быть определены из соотношений

(IIAIIN

пи-1 „т + 1

(т + 2)

т-2

беПАИ;

(т + О (т + 2-11А11м) m + 2-||AllN 0,.

(4)

где под 11-11 понимается любая из общепринятых норм матриц.,

Найденные а (4) m и N вводятся в устройство.

Преобразуем (3) к виду, удобному для реализации в устройстве

и к к . г m А Ат---г7 а,,А+а,М...а„А

If eQ .т ) «

где a,(KHl (,1,2 ,... ,m).

54

Устройство работает следующим образом.

В исходном состоянии генератор импульсов 25 не вырабатывает импульсов, коммутатор 3 подключает выход блока памяти 2 к первому входу блока 5, коммутатор 4 подключает выход блока памяти 2 к второму входу блока 5, коммутатор 6 соединяет выход блока 5 с блоком памяти 8, коммутатор 16 отключает блок памяти 15 от входов блоков умножения 17 и 18, коммутатор 9 соединяет выход блока памяти 3 с входом блока 10, а коммутатор 11 соединяет выход блока памяти 24 и вход сумматора 12.

На входы 1 и 20 поступает данная матрица А, на вход 30 - число М ,

причем М

m +

- 30, где АЛ - коли:

20

чество циклов, гп - число членов ряда (3), а на вход 19 поступает единичная матрица Е. В блоке памяти 15 записаны значения коэффициентов а,,

25 l - 2 m

По команде Пуск, поступающей на вход 37, происходит запуск генератора 25 импульсов, которым осуществляется продвижение единицы на выходах распределителя 27. По первому такту осуществляется подключение к первым входам блоков умножения 17 и 18 коэффициентов , из блока памяти 15. Производится вычисление матриц QQ Е и а, А , которые заносятся в

35 блоки памяти 21 и 22 соответственно. По второму такту в сумматоре 23 вычисляется матрица 5, аоЕ + а,А. которая заносится в блок памяти 24. По третьему такту осуществляется занесение мат рицы Sg В сумматор 12. По четвертому такту заносится в блок памяти 2 матрица А, коммутатор 16 подключает к входам блоков умножения 17 и 18 коэффициенты а ,а. Осу)чествляется

вычисление матриц а и а А , которые заносятся соответственно в блоки памяти 21 и 22. По пятому такту в блоке 5 осуществляется умножение мат2

риц АА и результат умножения А за- 50 носится в блок памяти 8, также вычисляется в сумматоре 23 значение S, ajE+qjfl и заносится в память f5noKa 24. По шестому такту коммутатор 11 подключает выход блока 10 к входу 55 сумматора 12, в блоке 1 осуществляется умножение матриц А 5,, резулъ.- тат суммируется в сумматоре 12. По седьмому такту коммутаторы 3 и 4

подключают выход блока памяти 8 к первому и второму входам блока 5, коммутатор 16 подключает коэффициенты о 6 6 а блоки 17 и 18 вычис- ляют матрицыОуЕ , которые заносятся в память. Коммутатор 6 подключает выход блока 5 к входу блока памяти 7, а коммутатор 9 выход блока

7- к блоку 10. По восьмому такту в блок 5 вычисляется матрица .

8сумматоре 23 вычисляется матрица 5г а Б +ао А. В девятом такте происходит вычисление матрицы А 5, которая суммируется в сумматоре 12 с мат- рицей . По десятому такту происходит включение кольцевого регистра 33 импульсов,с первого выхода которого подключается очередная пара коэффициентов Q J Чв вычисляются соответ- ствующие матрицы 5э a,F+agA, которые заносятся в память. По импульсу

с второго входа блок 5 вычисляет матрицу , которая заносится в

блок 7, а сумматор 23 вьиисляет матрицу 5, + agA . По импульсу с третьего выхода в блоке-10 вычисляется матрица которая в сумма- торе 12 складывается с матрицей +5ц, а в счетчик 34 заносится единица.

В дальнейшем импульсы с выходов кольцевого регистра 33 появляются в той же очередности, что и раньше, осуществляя последовательное получение соответствующих промежуточных сумм в сумматоре 12. Количество циклов кольцевого распределителя 33 подсчитывается счетчиком 34. Когда число циклов счетчика совпадает с величиной М, сигналом с выхода схемы сравнения происходит Останов генератора 25, коммутаторы приходят в первоначальное состояние, а результат А (2) из блока памяти 13 поступает на выход.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство для решения задач планирования экспериментов | 1984 |

|

SU1317450A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для обращения матриц | 1988 |

|

SU1647591A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1119009A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Многофункциональный цифровой коррелометр | 1979 |

|

SU826361A1 |

| УСТРОЙСТВО для РАСКРЫТИЯ и ВЫЧИСЛЕНИЯ ОПРЕДЕЛИТЕЛЕЙ МАТРИЦ | 0 |

|

SU404090A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения матриц | 1975 |

|

SU595726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-09—Подача