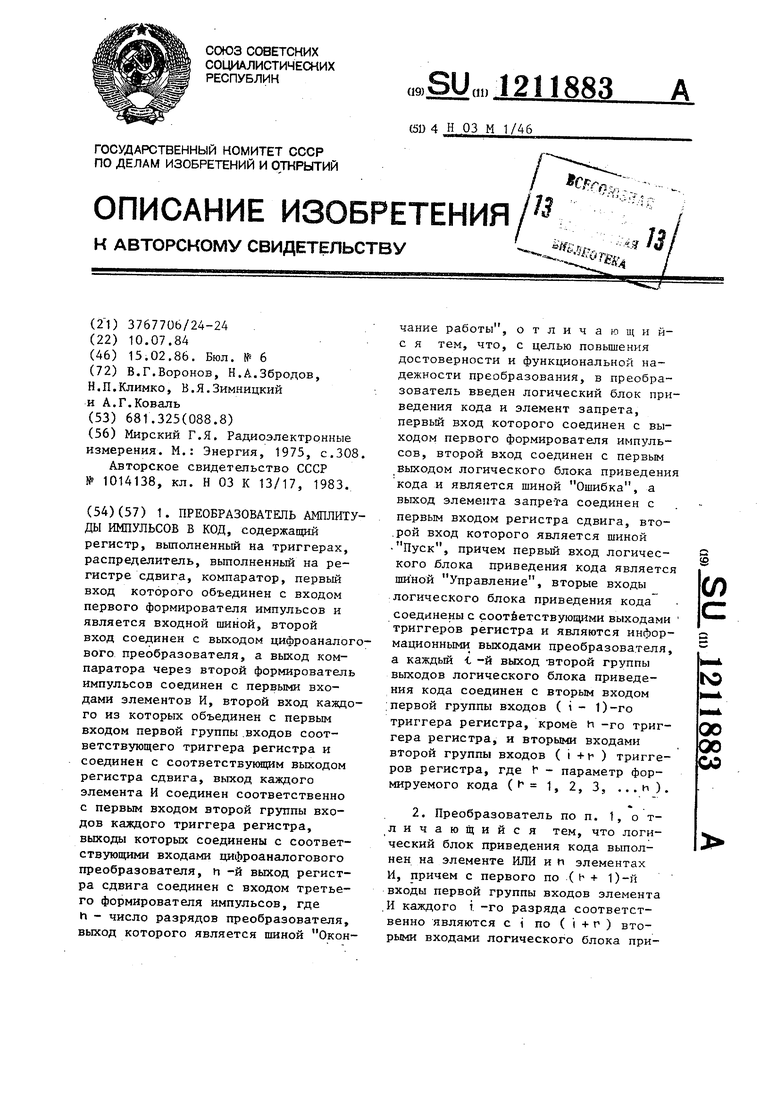

ведения кода, вторые входы всех элементов И объединены и являются первым входом логического блока приведения кода, выходы элементов И соединены с соответствующими входами

Изобретение относится к электроизмерительной технике и может быть использовано в устройствах автоматики, электроизмерительной техники и цифровой вычислительной техники при организации помехоустойчивой обработки информации.

Цель изобретения -, повышение достоверности и функциональной надежности преобразования.

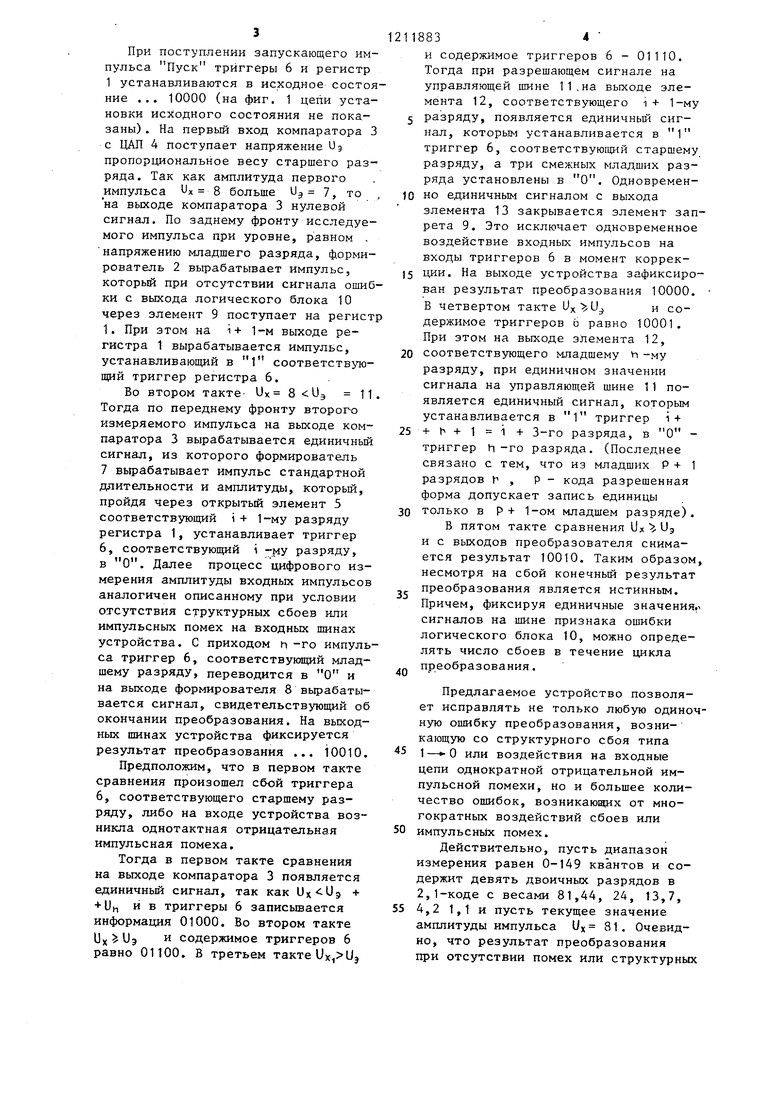

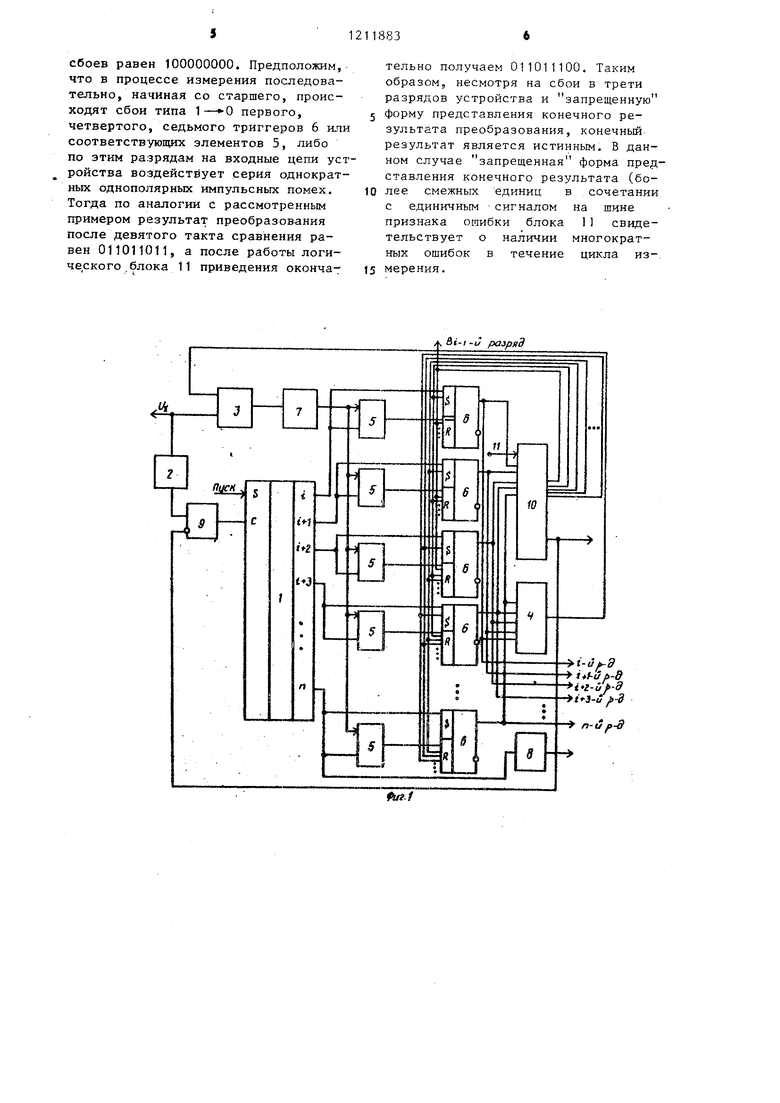

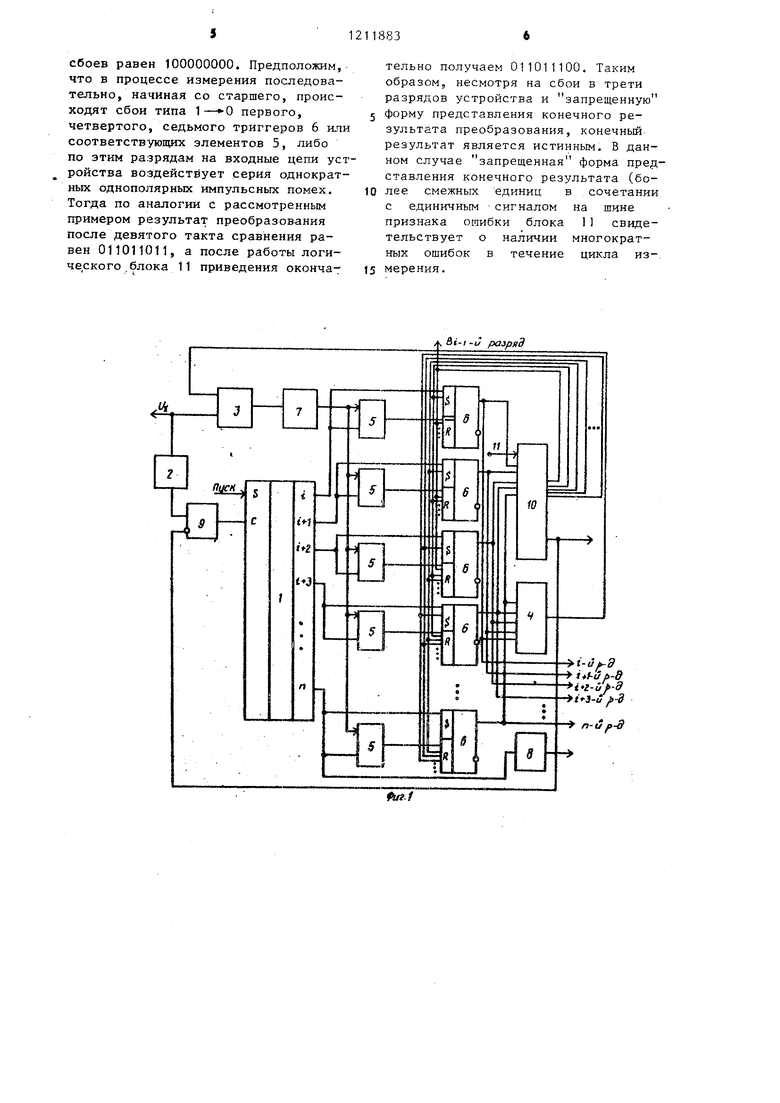

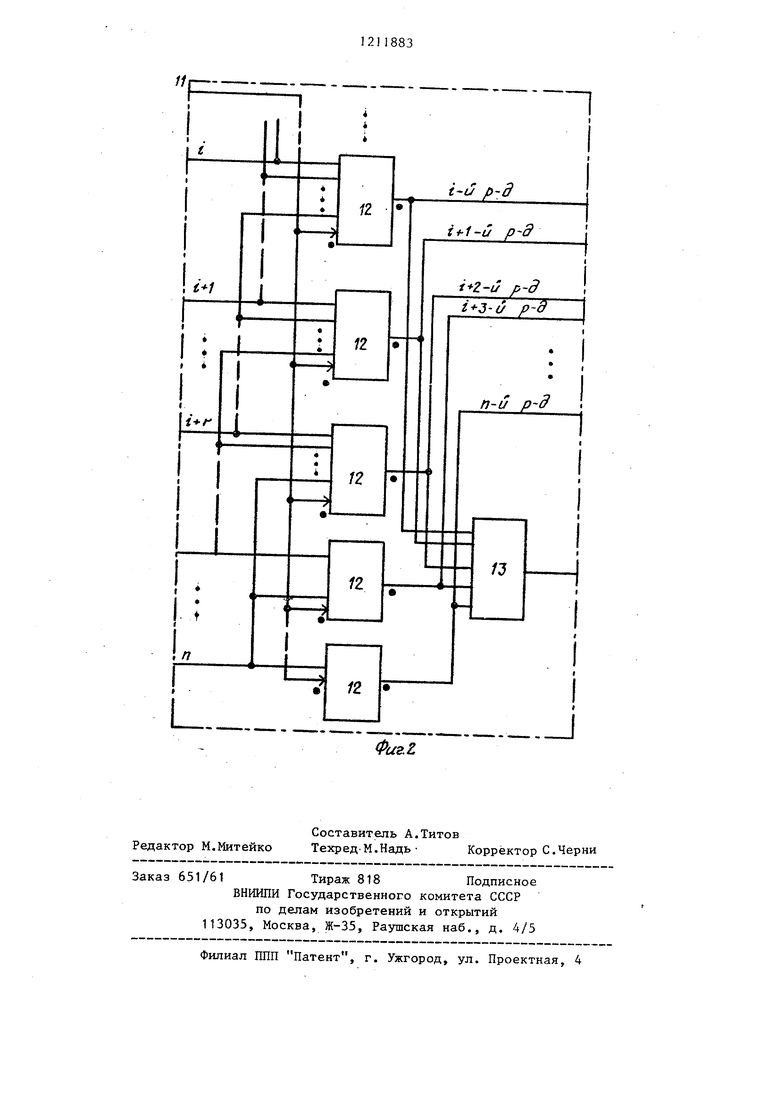

На фиг, 1 приведена функциональная схема преобразователя амплитуды импульсов в код; на фиг. 2 - функциональная схема логи11еского блока приведения.

Преобразователь содержит регистр сдвига 1, формирователь 2 импульсов компаратор 3, цифроаналоговый преобразователь 4, элементы И 5, триггер 6, формирователи 7 и 8 импульсов, элемент 9 запрета, логический блок 10 приведения кода, шину 11 Управление. Триггера 6 образуют регистр. Логический блок 10 содержит элементы И 12, элемент ИЛИ 13.

Принцип помехоустойчивого преобразования амплитуды в код основан на формировании в процессе работы устройства строго определенных комбинаций, которые являются разрешенными для конкретно заданных значений характеристических параметров и определяемые следующим рекурентны соотношением:

Bj - Bj.-( +...+ Bj-f + B(f,.p 1, ... r 1, 2, 3, ..., p 0, 1, 2

B Bj. - ... 1 2 BS , s p -H 3, p - 4, ... p + r,

где b - максимальное количество единиц, находящихся в соседних двоичных разрядах числа и

элемента ИЛИ и являются выходами второй группы выходов логического блока приведения кода, а выход элемента ИЛИ является первьм выходом логического блока приведения кода.

образуют разрешенную группу единицу

Р - параметр, который указьшает на минимальное количество нулей меж- ду разрешенными группами единиц. При f и и Р О имеем одну группу разрешенных единиц, весовые коэффициенты которых равны степени двойки и, следовательно, структура устройства для этого случая идентична структуре прототипа.

При t 1 и Р 1 получаем структуры преобразователей, работающие в 1,1-коде, которые позволяют определять структурные сбои в процессе преобразования и устранять воздействия однократных импульсных помех од ной полярности и части помех проти- воположной полярности на входные цепи прибора.

Если устройство работает в традиционном двоичном коде, то на управляющую шину 11 подается нулевой сигнал. При этом в работе участвуют компаратор 3, формирователи 2, 7 и 8, регистр 1, элементы 5, триггера 6, ЦАП 4, элемент 9. Так как на всех выходах логического блока 10 нулевые сигналы, то работа устройства аналогична работе прототипа.

Рассмотрим работу преобразователя, когда в качестве весов двоичных разрядов служат 2,1 числа.

Пусть преобразователь состоит из пяти двоичных разрядов, весовые коэффициенты которых, начиная со старшего (верхний на фиг; 1), соответственно равны 7, 4, 2, 1, 1 (ука- занное рекурентное соотношение). {иапазон измерения при этом равен 13 квантам.

Предположим, что измеряемая величина УХ равна 8 квантам и в процессе преобразования не изменяется.

При поступлении запускающего импульса Пуск триггеры 6 и регистр 1 устанавливаются в исходное состояние ... 10000 (на фиг. 1 цепи установки исходного состояния не показаны) . На первый вход компаратора 3 с ЦАП 4 поступает напряжение Ug пропорциональное весу старшего разряда. Так как амплитуда первого импульса Jx 8 больше иэ 7, то на выходе компаратора 3 нулевой сигнал. По заднему фронту исследуемого импульса при уровне, равном . напряжению младшего разряда, формирователь 2 вырабатывает импульс, который при отсутствии сигнала ошибки с выхода логического блока 10 через элемент 9 поступает на регист 1. При этом на 1+ 1-м выходе регистра 1 вырабатывается импульс, устанавливающий в 1 соответствующий триггер регистра 6.

Во втором такте- Ux 8 иэ 11 Тогда по переднему фронту второго измеряемого импульса на выходе компаратора 3 вырабатывается единичный сигнал, из которого формирователь 7 вырабатывает импульс стандартной длительности и амплитуды, который, пройдя через открытый элемент 5 соответствующий i + 1-му разряду регистра 1, устанавливает триггер 6, соответствующий -му разряду, в О. Далее процесс цифрового измерения амплитуды входных импульсов аналогичен описанному при условии отсутствия структурных сбоев или импульсных помех на входных шинах устройства. С приходом п -го импульса триггер 6, соответствующий младшему разряду, переводится в О и на выходе формирователя 8 вырабатывается сигнал, свидетельствующий об окончании преобразования. На выходных шинах устройства фиксируется результат преобразования ... 10010.

Предположим, что в первом такте сравнения произошел сбой триггера 6, соответствующего старшему разряду, либо на входе устройства возникла однотактная отрицательная импульсная помеха.

Тогда в первом такте сравнения на выходе компаратора 3 появляется единичный сигнал, так как + + UH ив триггеры 6 записьшается информация 01000. Во втором такте и содержимое триггеров 6 равно 01100. В третьем такте Ux,U3

2118834

и содержимое триггеров 6 - 01110. Тогда при разрешающем сигнале на управляющей шине 11, на выходе элемента 12, соответствующего 1+ 1-му

5 разряду, появляется единичный сигнал, которым устанавливается в 1 триггер 6, соответствующий старшему разряду, а три смежных младших разряда установлены в О. ОдновременJO но единичным сигналом с выхода

злемента 13 закрывается элемент запрета 9. Это исключает одновременное воздействие входных импульсов на входы триггеров 6 в момент коррек15 ции. На выходе устройства зафиксирован результат преобразования 10000. В четвертом такте ,j и содержимое триггеров 6 равно 10001. При этом на выходе элемента 12,

20 соответствующего младшему h-му разряду, при единичном значении сигнала на управляющей шине 11 появляется единичный сигнал, которым устанавливается в 1 триггер i+

25 + b + 1 i + 3-го разряда, в О - триггер h -го разряда. (Последнее связано с тем, что из младших Р + 1 разрядов Г , Р - кода разрешенная форма допускает запись единицы

30 только в Р+ 1-ом младшем разряде).

В пятом такте сравнения Ux Uj и с выходов преобразователя снимается результат 10010. Таким образом, несмотря на сбой конечный результат преобразования является истинным. Причем, фиксируя единичные значения. сигналов на шине признака ошибки логического блока 10, можно определять число сбоев в течение цикла

.„ преобразования. 40

Предлагаемое устройство позволяет исправлять не только любую одиночную ошибку преобразования, возникающую со структурного сбоя типа

О или воздействия на входные цепи однократной отрицательной импульсной помехи, но и большее количество ошибок, возникающих от многократных воздействий сбоев или

50 импульснь1х помех.

Действительно, пусть диапазон измерения равен 0-149 квантов и содержит девять двоичных разрядов в 2,1-коде с весами 81,44, 24, 13,7,

55 4,2 1,1 и пусть текущее значение амплитуды импульса Ux 81. Очевидно, что результат преобразования при отсутствии помех или структурных

35

сбоев равен 100000000. Предположим, что в процессе измерения последовательно, начиная со старшего, происходят сбои типа 1- О первого, четвертого, седьмого триггеров 6 или соответств;утощих элементов 5, либо по этим разрядам на входные цепи устройства воздействует серия однократных однополярных импульсных помех. Тогда по аналогии с рассмотренным примером результат преобразования после девятого такта сравнения равен 011011011, а после работы логического, блока 11 приведения окончательно получаем 011011100. Таким образом, несмотря на сбои в трети разрядов устройства и запрещенную

форму представления конечного результата преобразования, конечный, результат является истинным. В данном случае запрещенная форма представления конечного результата (более смежных единиц в сочетании с единичным сигналом на шине признака ошибки блока II свидетельствует о наличии многократных ошибок 15 мерения.

в течение цикла из

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1981 |

|

SU974572A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1990 |

|

SU1725396A1 |

| Мирский Г.Я | |||

| Радиоэлектронные измерения | |||

| М.: Энергия, 1975, с.308 | |||

| Преобразователь амплитуды импульсов в код | 1981 |

|

SU1014138A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-10—Подача