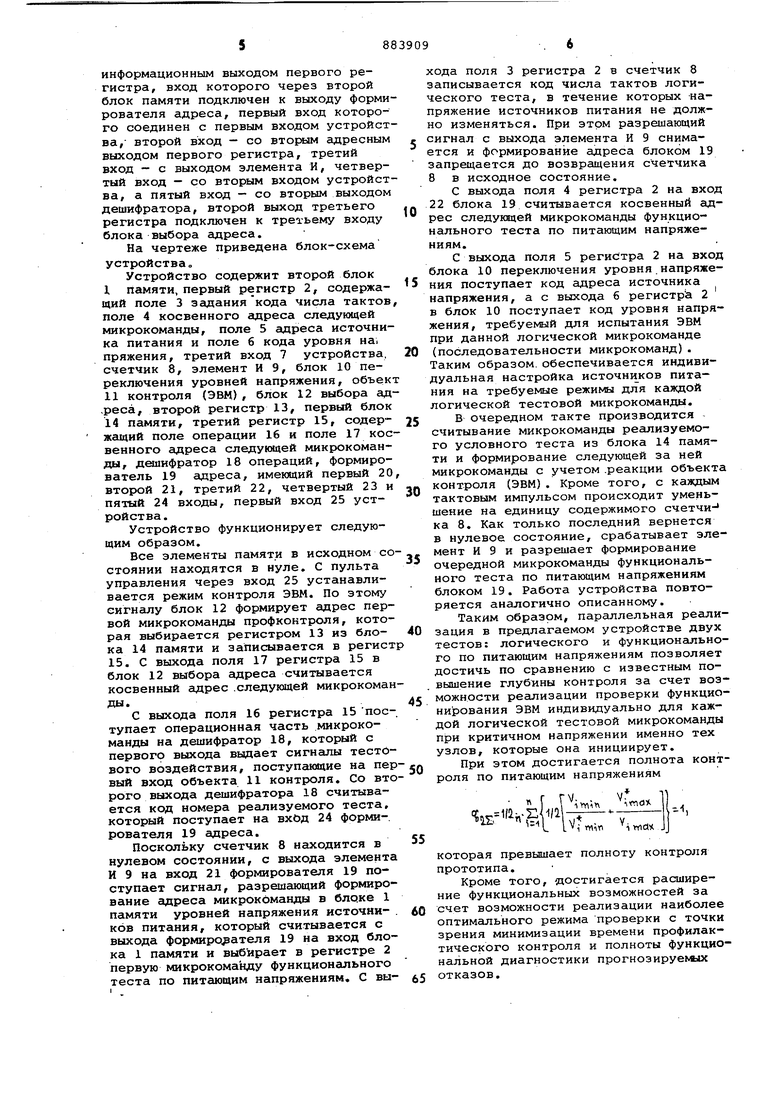

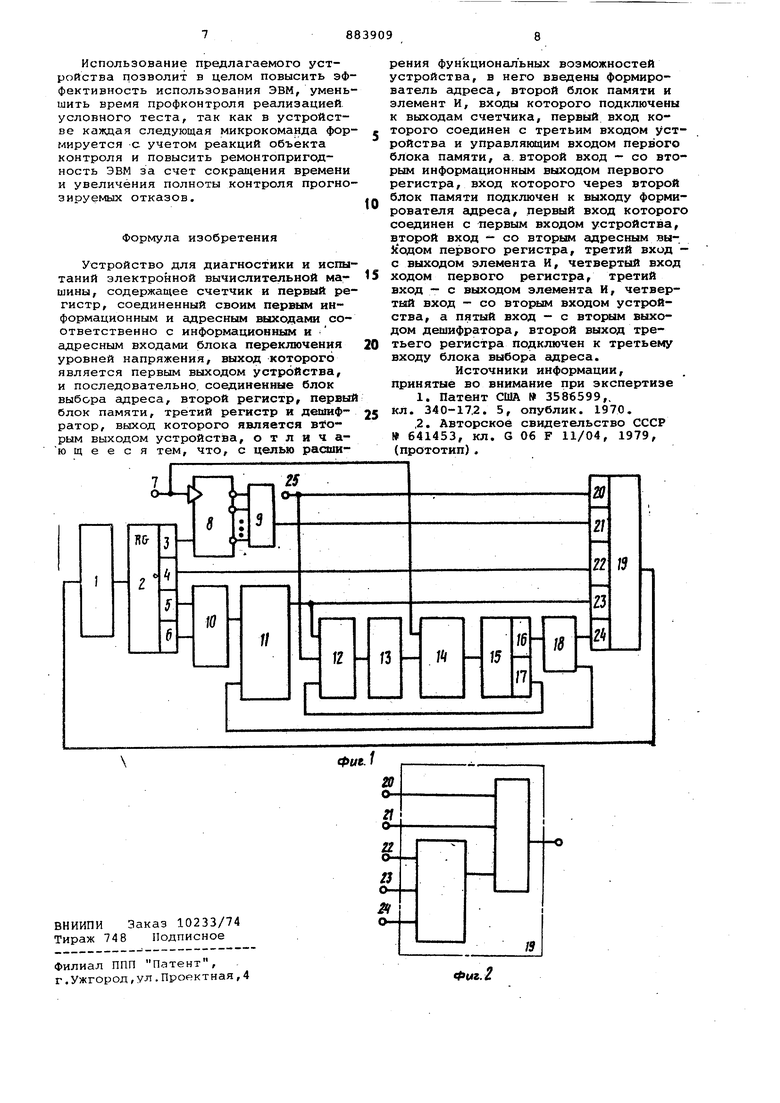

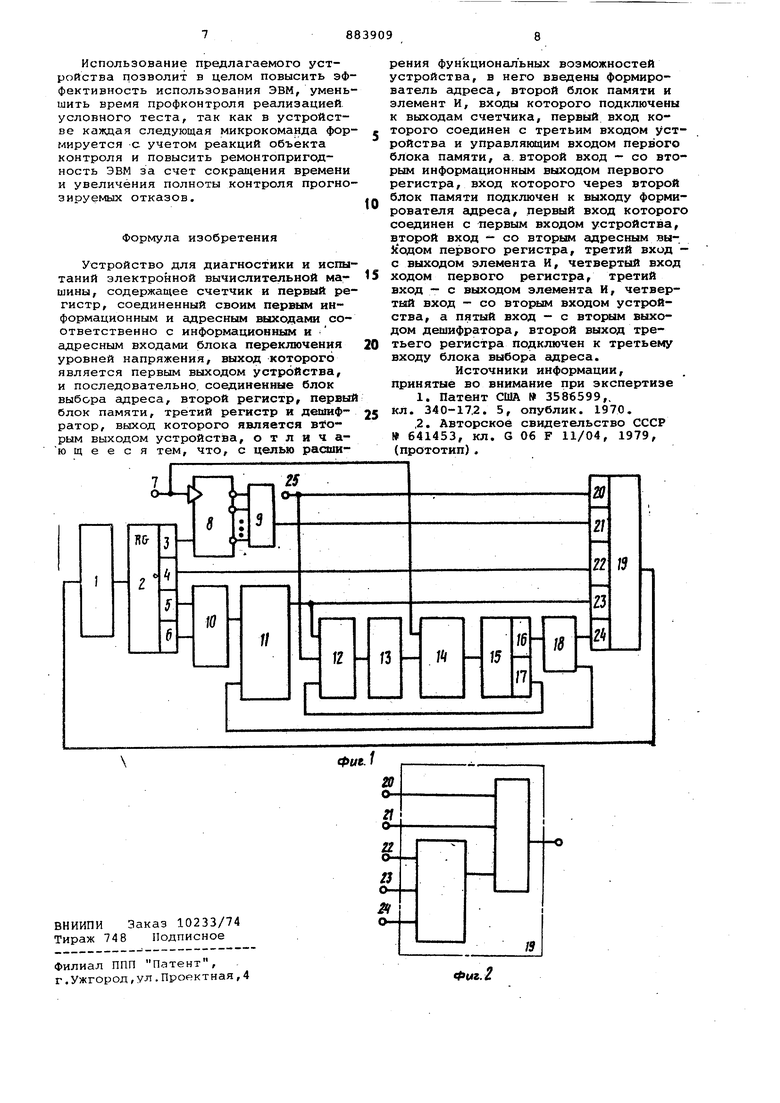

тестирование при различных уровнях питающих напряжений (физический контроль) . Это связано с тем, что различные узлы ЭВМ (объекта контроля) критичны к различным диапазонам изме нения питакяцих напряжений. Проверка узла при различных (критических) уровнях питающих напряжений позволяе обнаружить прогнозируемые отказы.Таким образом, для наиболее полного достижения целей профилактического контроля необходимо проверить работо способность каждого i-ro узла ЭВМ при трех возможных уровнях значений питающих напряжений, которые образуют полное множество проверок V узла is . 0 V.fV, V. V г 1 L imqx 1 1 min i HOMJ ) где , , соответственно максимально, минимально и номинально допустимые по условиям работоспособности напряжения питания ji-ro узла, В зависимости от условий работоспособности системы в к.аждом такте функционирования (тестирования) значения величины напряжений, .входящих во множество V , могут изменяться. Таким образом, максимальной эффек тивности выявления прогнозируемых от казов можно достичь только в случае когда работоспособность ЭВМ (объекта контроля) при реализации каждой микрокоманды проверяется при критичном напряжении именно тех узлов, которые она инициирует. Эффективность реализуемой методики контроля характеризующей функцио нальные возможности устройства контроля , можно оценить величиной суммар ной полноты контроля gg, которая определяется по формуле ,,и/.|., причем справедливо О g, $ In В известном устройстве принята стратегия профилактического контроля при которой осуществляется неоднократная реализация одного и того же диагностического теста при различных уровнях напряжений. Величины напряжений проверки выбираются из условий потенциально возможной работоспособности всех устройств, действующих в процессе диагностирования в соответствии с выражением V;., шх (V, j;, , v; r (V,);,,; n V J. HOM n где , V, , V«V - соответственно максимально, минимально допус тимо и номинальное значения напряжения при проверке устройства При этом возможен контроль только при множестве уровней напряжений V,- , которое определяется по формуле V.HOM waxi min} т.е. возможный диапазон изменения питающих напряжений ограничен вели- . чинами Из этого выражения следует, что дЛя известного устройства д 1, так как справедливо выражение V / maxiTfliri Ynin 1 i max Таким образом, возможность реализации только рассмотренной стратегии профилактического контроля существенно сужает функциональные возможности устройства за счет низкой полноты контроля прогнозируемых отказов. Кроме того, важным аспектом, характеризующим функциональные возможности и время проведения контроля, является тип реализуемого теста (условный или безусловный). Условный тест требует меньшего времени для профилактического контроля, однако условием его реализации является учет реакции объекта контроля в процессе проверки. В известном устройстве реализуется безусловный тест как по управляющим микрокомандам, так и по уровням питающих напряжений, при этом логический тест никак не связан с тестом по уровням питающих напряжений и, кроме того, ни тот, ни другой тесты не учитывают реакцию объекта на стимулирующее воздействие и на изменение уровня напряжения. Это приводит к сужению функциональных возможностей и увеличению времени профилактического контроля. Цель изобретения - расширение функциональных возможностей и повышение полноты контроля. Поставленная цепь достигается тем, что устройство для диагностики и испытаний электронной вычислительной машины, содержащее счетчик, первый регистр, срединеннь1й своим первым информационным и адресным выходами соответственно с информационным и адреснымвходами блока переключения уровней напряжения, выход которого является первым выходом устройства, и последовательно соединенные блок выбора адреса, второй регистр, первый блок памяти, третий регистр и дешифратор, выход которого является вторым выходом устройства, введены формирователь адреса, второй блок памяти и элемент И, входы которого подключены к выходам счетчика, первый вход которого соединен с третьим входом устройства и управляющим входом первого блока памяти, а второй вход- со вторым информационным выходом первого регистра, вход которого через второй блок памяти подключен к выходу форми рователя адреса, первый вход которого соединен с первым входом устройст ва,- второй вход - со вторым адресным выходом первого регистра, третий вход - с выходом элемента И, четвертый вход - со вторым входом устройст ва, а пятый вход - со вторым выходом дешифратора, второй выход третьего регистра подключен к третьему входу блока выбора адреса. На чертеже приведена блок-схема устройства„ Устройство содержит второй блок Iпамяти, первый регистр 2, содержащий поле 3 заданиякода числа тактов поле 4 косвенного адреса следующей микрокоманды, поле 5 адреса источника питания и поле 6 кода уровня на, пряжения, третий вход 7 устройства, счетчик 8, элемент И 9, блок 10 переключения уровней напряжения, объек IIконтроля (ЭВМ), блок 12 выбора ад ,реса, второй регистр 13, первый блок 14 памяти, третий регистр 15, содержсцций поле операции 16 и поле 17 кос венного адреса следующей микрокоманды, детиифратор 18 операций, формирователь 19 с1дреса, имеющий первый 20 второй 21, третий 22, четвертый 23 и пятый 24 входы, первый вход 25 устройства. Устройство функционирует следующим образом. Все элементы памяти в исходном со стоянии находятся в нуле. С пульта управления через вход 25 устанавливается режим контроля ЭВМ. По этому сигналу блок 12 формирует адрес первой микрокоманды профконтроля, которая выбирается регистром 13 из блока 14 памяти и записывается в регист 15. С выхода поля 17 регистра 15 в блок 12 выбора адреса считывается косвенный адрес .следующей микрокоман ды. С выхода поля 16 регистра 15 поступает операционная часть микрокоманды на дешифратор 18, который с первого выхода вьщает сигналы тестового воздействия, поступающие на пер вый вход объекта 11 контроля. Со вто рого выхода дешифратора 18 считывается код номера реализуемого теста, который поступает на вход 24 форми-. рователя 19 адреса. Поскольку счетчик 8 находится в нулевом состоянии, с выхода элемента И 9 иа вход 21 формирователя 19 поступает сигнал, разрешающий формирование адреса микрокоманды в блоке 1 памяти уровней напряжения источни- . ков питания, который считывается с выхода формирователя 19 на вход блока 1 памяти и выбирает в регистре 2 первую микрокоманду функционального теста по питающим напряжениям. С выхода поля 3 регистра 2 в счетчик 8 записывается код числа тактов логического теста, в течение которых -напряжение источников питания не должно изменяться. При этом разрешающий сигнал с выхода элемента И 9 снимается и формирование адреса блоком 19 запрещается до возвращения счетчика 8 в исходное состояние. С выхода поля 4 регистра 2 на вход 22 блока 19 считывается косвенный адрес следукяцей микрокоманды функционального теста по питающим напряжениям. С выхода поля 5 регистра 2 на вход блока 10 переключения уровня.напряжения поступает код адреса источника напряжения, а с выхода 6 регистра 2 в блок 10 поступает код уровня напряжения, требуемый для испытания ЭВМ при данной логической микрокоманде (последовательности микрокоманд). Таким образом, обеспечивается индивидуальная настройка источников питания на требуемые режимы для каждой логической тестовой микрокоманды. В очередном такте производится считывание микрокоманды регшизуемого условного теста из блока 14 памяти и формирование следующей за ней микрокоманды с учетом .реакции объекта контроля (ЭВМ). Кроме того, с каждым тактовым импульсом происходит уменьшение на единицу содержимого счетчи- ка 8. Как только последний вернется в нулевое состояние, срабатывает элемент И 9 и разрешает формирование очередной микрокоманды функционального теста по питающим напряжениям блоком 19. Работа устройства повторяется аналогично описанному. Таким образом, параллельная реализация в предлагаемом устройстве двух тестов: логического и функционгшьного по питающим напряжениям позволяет достичь по сравнению с известным повышение глубины контроля за счет возможности реализации проверки функционирования ЭВМ индивидуально для каждой логической тестовой микрокоманды при критичном напряжении именно тех узлов, которые она инициирует. При этом достигается полнота контроля по питающим напряжениям Г VV. lyyiin Imo. которая превышает полноту контроля прототипа. Кроме того, достигается расширение функциональных возможностей за счет возможности реализации наиболее оптимального режима проверки с точки зрения минимизации времени профилактического контроля и полноты функциона.льной диагностики прогнозируемых отказов. Использование предлагаемого устройства позволит в целом повысить эф фективность использования ЭВМ, умень шить время профконтроля реализацией, условного теста, так как в устройстве каждая следующая микрокоманда фор мируется с учетом реакций объекта контроля и повысить ремонтопригодность ЭВМ за счет сокращения времени и увеличения полноты контроля прогно зируемых отказов. Формула изобретения Устройство для диагностики и испы таний электронной вычислительной машины, содержащее счетчик и первый ре гистр, соединенный своим первым информационным и адресным выходгили соответственно с информационным и адресным входами блока переключения уровней напряжения, выход которого является первым выходом устройства, и последовательно, соединенные блок выбора адреса, второй регистр, первы блок памяти, третий регистр и дешифратор, выход которого является вторым выходом устройстзва, о т л и ч аю щ е е с я тем, что, с целью расширения функциональных возможностей устройства, в него введены формирователь адреса, второй блок памяти и элемент И, входы которого подключены к выходам счетчика, первый вход которого соединен с третьим входом устройства и управляющим входом первого блока памяти, а второй вход - со вторым информационным выходом первого регистра, вход которого через второй блок памяти подключен к выходу формирователя адреса, первый вход которого соединен с яервым входом устройства, второй вход - со вторым адресным выЗсодом первого регистра, третий вход - с выходом элемента И, четвертый вход ходом первого регистра, третий вход - с выходом элемента И, четвертый вход - со вторым входом устройства, а пятый вход - с вторым выходом дешифратора, второй выход третьего регистра подключен к третьему входу блока выбора адреса. Источники информации, принятые во внимание при экспертизе 1. Патент США 3586599,. кл. 340-17,2. 5, опублик. 1970. ,2. Авторское свидетельство СССР 641453, кл. G 06 F 11/04, 1979, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики эвм | 1976 |

|

SU641453A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для контроля программ и микропрограмм | 1983 |

|

SU1176334A1 |

| Устройство для восстановления процессора после сбоя | 1979 |

|

SU857999A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

Авторы

Даты

1981-11-23—Публикация

1979-12-29—Подача