11

Изобретение относится к вычисли тельной технике, предназначено для использования в качестве аппаратного расширителя в микропроцессорных системах и может найти применение в приборостроении, управляющих и информационно-измерительных системах

Целью изобретения является упрощение устройства за счет сокращения объема блока памяти.

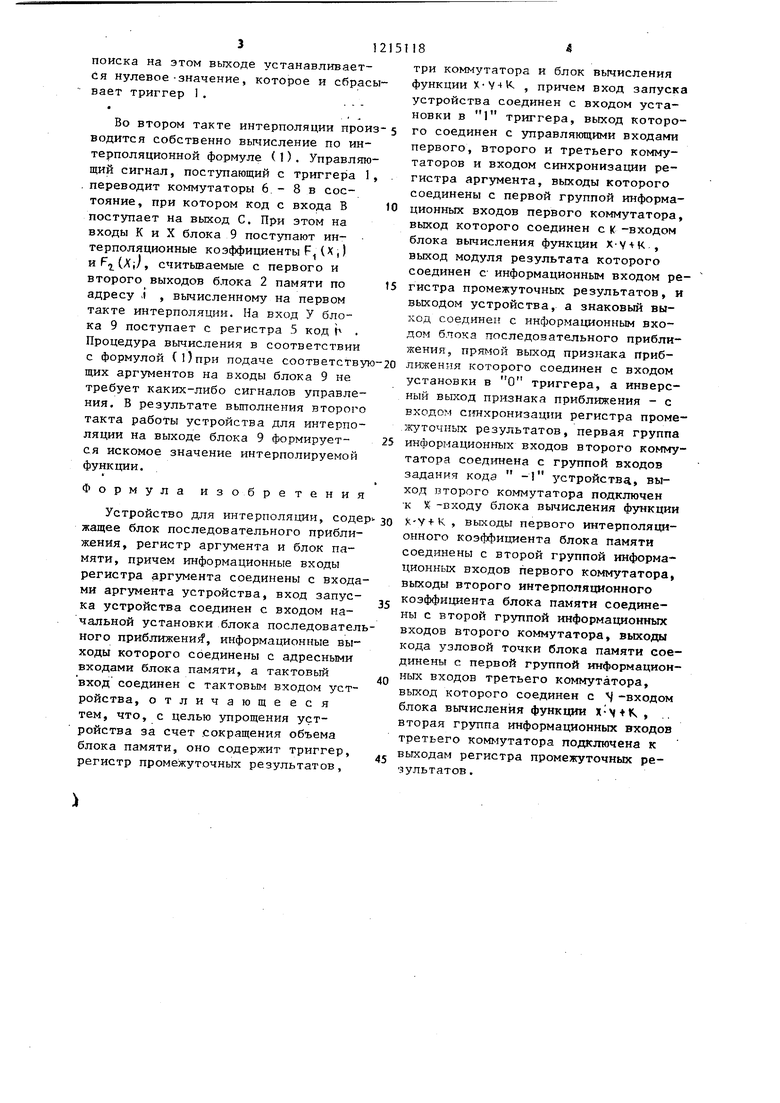

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит триггер 1, блок 2 памяти, блок 3 последовательного приближения, регистр 4 аргумен- та, регистр 5 промежуточных результатов, первый, второй и третий коммутаторы 6, 7 и 8 соответственно, блок 9 вычисления функции { ).

Устройство работает следующим образом.

Интерполяция функции (х) , заданной на конечном множестве точек Х, Х,, Хз- .. Xj,... Х двумя координатами ) , F() , производится в соответствии с выражениями следующего вида:

y(x) F,{X,) + F(XiVr, ; И)

Xi6 Х Ki,v ,(2)

где

( Х-Х.

(3)

Реализация интерполяционных выражений (1)-(З) осуществляется в устройстве .в два такта. Управляющие, сигналы, формируемые триггером 1 и блоком 3, определяют состояние гистров 4 и 5 и коммутаторов 6 8 в зависимости от такта работы устройства для интерполяции.

В первом такте производится нахождение номера М узловой точки интерполируемой функции и величины Р , вычисляемой в соответствии с формулой (З). Начинается первый такт вы- числения при поступлении на вход С1 устройства для интерполяции сигнала начального установа. Триггер 1 устанавливается при этом в единичное состояние, и на информационном вы-- ходе блока 3 формируется начальный код для процедуры поразрядного поиск Блок 3 реализован на основе ИС К155ИР17. Начальное значение кодаР будет 0111111111111111. Установле- мне триггера I в единичное состояние обеспечивает прием кода аргумента Х в регистр 4. Синхронизация регистра

18 2

4 - динамическая, по положительному фронту импульса на выходе триггера Единичный сигнал на входах управления коммутаторами 6-8 приводит к тому, что на выход С этих коммутаторов поступает сигнал с входа А. При этом на вход К блока 9 поступает выход регистра 4, в котором записан код аргумента X , на вход X блока 9 подается константа - 1, представленная в дополнительном коде, а на вход-У - значение узловой точки Xj , , считьшаемой с выхода блока 2 памяти по адресу, формируемому на информационном выходе блока 3. Процедура поразрядного поиска значения { производится в устройстве по методу деления отрезка пополам, т.е. путем Нахождения корня уравнения

X - Xj О,

(М

в котором в качестве переменной выступает значение Х; , считьшаемое из блока памяти. Процедура поразрядного поиска,значения тактиру- ется синхроимпульсами С2, поступающими на вход синхронизации блока 3. В качестве результата сравнения величин X и Х; в процессе поразрядного поиска величины используется знаковый разряд выхода блока 9. При поступлении каждого текущего синхроимпульса С2 в блоке 3 производится вычисление одного разряда кода D . В связи с этим длительность первого такта процедуры интерполяции равна количеству разрядов в коде 1) , счи- тьюаемом с информационного выхода блока 3, умноженном на период следования импульсов С2. В качестве блока 9 удобно использовать матричный умножитель, так как в матричных умножителях имеется свободный вход слагаемого К.

Завершается первый такт интерполяции после получения значения номе- . ра узловой точки i на информационном вьпсоде блока 3. При этом на выходе управления этого блока появляются прямой сигнал управления, обнуляют щий триггер 1, и инверсия этого сигнала, обеспечивающая запись кода f с выхода блока 9 в регистр 5. В качестве выхода управления при реализации блока вычисления адреса на основе ИС К155ИР17 используется выход, непосредственно следующий за информационными. В процессе поразрядного

поиска на этом выходе устанавливается нулевое-значение, которое и сбрасывает триггер 1.

Во втором такте интерполяции произ водится собственно вычисление по интерполяционной формуле (1). Управляющий сигнал, поступающий с триггера 1 переводит коммутаторы 6. - 8 в состояние, при котором код с входа В поступает на выход С. При этом на входы К и X блока 9 поступают интерполяционные коэффициенты F (X,) иР(Л(/, считьшаемые с первого и второго выходов блока 2 памяти по адресу .1 , вычисленному на первом такте интерполяции. На вход У блока 9 поступает с регистра 5 код Ь . Процедура вычисления в соответствии с формулой (1)при подаче соответствую щих аргументов на входы блока 9 не требует каких-либо сигналов управления. Б результате выполнения второго такта работы устройства для интерполяции на выходе блока 9 формирует- ся искомое значение интерполируемой функции.

Формула изобретения

Устройство для интерполяции, содер жащее блок последовательного приближения, регистр аргумента и блок памяти, причем информационные входы регистра аргумента соединены с входами аргумента устройства, вход запуска устройства соединен с входом начальной установки блока последовательного приближени}, информационные выходы которого соединены с адресными входами блока памяти, а тактовый вход соединен с тактовым входом устройства, отличающееся тем, что, с целью упрощения устройства за счет сокращения объема блока памяти, оно содержит триггер, регистр промежуточных результатов.

три коммутатора и блок вычисления функции , причем вход запуска устройства соединен с входом установки в 1 триггера, выход которого соединен с управляющими входами первого, второго и третьего коммутаторов и входом синхронизации регистра аргумента, выходы которого соединены с первой группой информационных входов первого коммутатора, выход которого соединен с к -входом блока вычисления функции X-V-vK , вькод модуля результата которого соединен с- информационным входом регистра промежуточных результатов, и выходом устройства, а знаковый выход соединен с информационным входом блока последовательного приближения, выход признака приближения которого соединен с входом установки в О триггера, а инверсный выход признака приближения - с входом С1тхронизации регистра промежуточных результатов, первая группа информационных входов второго коммутатора соединена с группой входов задания кода -1 устройству, выход второго коммутатора подключен к ) -входу блока вычисления функции

, выходы первого интерполяционного коэффициента блока памяти соединены с второй группой информационных входов первого коммутатора, выходы второго интерполяционного коэффициента блока памяти соединены с второй группой информационных входов второго коммутатора, выходы кода узловой точки блока памяти соединены с первой группой информационных входов третьего коммутатора, вькод которого соединен с S -входом блока вычисления функции х- + , вторая группа информационных входов третьего коммутатора подключена к выходам регистра промежуточных результатов.

Редактор А.Лежнина

Составитель А.Чеканов

Техред С.Мигунова Корректор О.Луговая

908/57 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал тп Патент, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

| Интерполятор третьей степени | 1988 |

|

SU1566369A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Функциональный преобразователь | 1985 |

|

SU1285465A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Интерполятор | 1986 |

|

SU1405074A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

Изобретение предназначено для вычисления значений функции в микропроцессорных системах и может применяться в приборостроении, управляющих и информационно-измерительных системах. Целью изобретения является сокращение объема памяти за счет использования узловых точек функции с произвольным взаиморасположением. Привязка к узловой точке осуществляется путем выполнения процедуры поразрядного поиска адреса. Устройство содержит регистр последовательного приближения адреса, регистр аргумента, блок памяти, триггер, регистр промежуточных значений, три коммутатора и блок умножения. 1 ил. i (Л ю С71

| Патент ФРГ № 2853560, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Патент Великобритании, № 2010545, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1986-02-28—Публикация

1984-01-20—Подача