1

Изобретение относится к автоматике и вычислительной технике и может быть использовано -для контроля блоков памяти.

Цель изобретения - повьппение достоверности контроля.

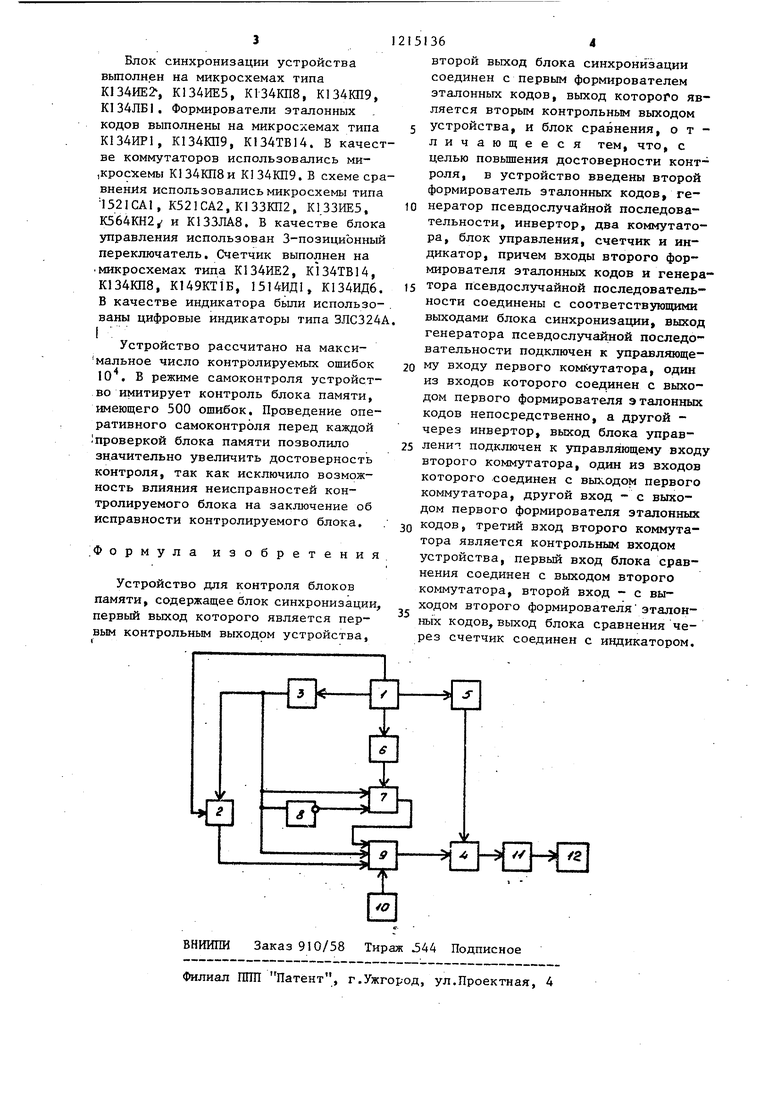

На чертеже представлена функциональная схема устройства.

Устройство содержит блок синхронизации 1, соединенньп с контролируемым блоком 2 и первым формирователем эталонных кодов 3, блок сравнения 4, один из входов которого соединен с выходом второго формирователя эталонных кодов 5, входы последнего и генератора псевдослучайной последовательности 6 соединены с выходом блока синхронизации 1, выходы генератора псевдослучайной последовательности 6 соединен с управляющим входом первого коммутатора 7, первый вход которого соединен с в ыходом формирователя эталонных кодов 3 непосредственно, а второй через инвертор 8, выход первого коммут атора 7 подключен к первому вход

.второго коммутатора 9, второй вход кот срого соединен с выходом формировател

эталонных кодов 3, а третий вход ;подключен к выходу контролируемого блока 2, Управляющий вход второго коммутатора 9 соединен с выходом

блока управления 10. Бьпсод коммутатора 9 соединен с вторым входом блока сравнения 4,, выход которого через счетчик 1 соединен с индикатором 12,

Устройство работает следующим образом.

Блок синхронизации 1 вырабатывает тактовые и синхронизирующие им,пульсЫл которые поступают на форми рователи эталонных кодов 3 и- 5, на контролируемый блок 2 и на генератор

псевдослучайной последовательности 6 Формирователи эталонных кодов 3 и 5 вырабатывают две одинаковые кодовые последовательности нулей и единиц (эталонные коды могут формироваться с разньми частотами, что дает возможность проводить контроль при ускоренном воспроизведении, Генератор псевдослучайной последовательности 6 вырабатывает код, состоящий из заведомо известного количества единичных импульсов на определенное число элементов памяти, случайным образом распределенных в интервале цикла контроля, Псевдослу5136

5

0

5

0

5

0

5

0

5

чайная последовательность, вырабатываемая генератором псевдослучайной последовательности 6, поступает на управляющий вход- коммутатора 7, на первый вход кот.орого поступает код с формирователя эталонного кода 3 непосредственно, а на второй вход - через инвертор 8. Таким образом на выходе коммутатора 7 формируется эталонный код с заведомо известным числом искусственно введенных ошибок путем инвертирования отдельных разрядов кода.- Код с выхода коммутатора 7 поступает на первый вход коммутатора 9, на второй вход которого поступает код с формирователя эталонных кодов 3 непосредственно, а на третий вход - выходной- сигнал контролируемого блока. Блок управления 10 позволяет получать на выходе коммутатора 9 любой из трех его входных сигналов в зависимости от управляющего сигнала. Сигнал с выхода коммутатора 9 поступает на первый вход блока сравнений 4, на второй вход которого поступает эталонный код с выхода формирователя эталонных кодов 5. Полученные импульсы ошибок с выхода блока сравнения 4 поступают через счетчик

11 на J ндикaтop 12. ,

Самоконтроль устройства производится следующим образом. Блок управления 10 подключает на выход второго коммутатора 9 (на вход блока сравнения 4) сигнал с выхода коммутатора 7, имитирующий контролируемый блок с заранее известным числом ошибок. В случае исправности устройства контроля на индшсаторе 12 должно отобразиться заранее известное число ошибок. Затем на выход коммутатора 9 поступает сигнал, имитирующий полностью исправньш контролируемый блок (ошибки отсутствуют). В случае исправности устройства контроля на индикаторе 12 должно отображаться нулевое число ошибок. Затем в случае если устройство контроля исправно, блок управления 9 подключает на выход коммутатора 9 (на вход блока сравнения 4) выходной сигнал контролируемого блока 2. Таким образом, заключение, о годности контролируемого блока дается с учетом возможных неисправностей контролируемого блока, что значительно повышает достоверность контроля блоков памяти ,

3

Блок синхронизации устройства выполн.ен на микросхемах типа К134ИЕ2 , К134ИЕ5, К134КП8, К134И19, К134ЛБ1. Формирователи эталонных кодов выполнены на микросхемах типа К134ИР1, К134КП9, К134ТВ14. В качестве коммутаторов использовались ми- ,кросхемы К134КП8И К134КП9. В схеме сравнения использовались микросхемы типа I52ICA1, К521СА2, К133КП2, К133ИЕ5, К564КН2, и К133ЛА8. В качестве блока управления использован З-позиционный переключатель. Счетчик выполнен на микросхемах типа К134ИЕ2, к 134ТВ14, К134КП8, К149КТ1Б, 1514ИД1, К134ИД6. В качестве индикатора были использо- ваны цифровые индикаторы типа ЗЛС324А

I :

Устройство рассчитано на макси- мальное число контролируемых ошибок 10 , В режиме самоконтроля устройство имитирует контроль блока памяти, имеющего 500 ошибок. Проведение оперативного самоконтроля перед каждой Iпроверкой блока памяти позволило значительно увеличить достоверность контроля, так как исключило возможность влияния неисправностей контролируемого блока на заключение об исправности контролируемого блока,

Формула изобретения

Устройство для контроля блоков памяти, содержащее блок синхронизации, первый выход которого является первым контрольным выходом устройства.

10

I5I36Л

второй выход блока синхронизации соединен с первым формирователем эталонных кодов, выход которого является вторым контрольным выходом 5 устройства, и блок сравнения, отличающееся тем, что, с целью повьшения достоверности контроля, в устройство введены второй формирователь эталонных кодов, генератор псевдослучайной последовательности, инвертор, два коммутатора, блок управления, счетчик и индикатор, причем входы второго формирователя эталонных кодов и генера- 15 тора псевдослучайной последовательности соединены с соответствующими выходами блока синхронизации, выход генератора псевдослучайной последовательности подключен к управляюще- 20 му входу первого коммутатора, один из входов которого соединен с выходом первого формирователя э талонных кодов непосредственно, а другой - через инвертор, выход блока управ- 25 ленит подключен к управляющему входу второго коммутатора, один из входов которого соединен с выходом первого коммутатора, другой вход - с выходом первого формирователя эталонных 3Q кодов, третий вход второго коммутатора является контрольным входом устройства, первый вход блока сравнения соединен с выходом второго коммутатора, второй вход - с выходом второго формирователя эталонных кодов, вькод блока сравнения через счетчик соединен с индикатором.

5

ВНИИПИ Заказ 910/58 Тираж 44 Подписное Филиал ШШ Патент, г,Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Устройство для контроля блоков буферной памяти | 1984 |

|

SU1293761A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля аппарата магнитной записи | 1985 |

|

SU1269206A2 |

| Устройство для программного контроля | 1978 |

|

SU805316A1 |

| Устройство для контроля памяти | 1987 |

|

SU1587598A1 |

| Способ контроля логических устройств | 1989 |

|

SU1709256A1 |

| Устройство для контроля оборудования радиорелейных станций | 1984 |

|

SU1172037A1 |

Изобретение относится к области приборостроения и может быть исполь- 3овано для контроля цифровых блоков памяти. Цель изобретения - повышение достоверности контроля. Устройство содержит блок синхронизации, два формирователя эталонньрс кодов, блок сравнения, генератор псевдослучайной последовательности, два коммутатора, инвертор, блок управления, счетчик и индикатор. Устройство дасснь тано на максимальное число контролируемых ошибок 10 . В режиме самоконтроля устройство имитирует конт()оль блока памяти, имеющего 500 ошибок. Проведение оперативного самоконтроля перед каждой проверкой блока памяти позво- /лило значительно увеличить достоверность контроля, т.к. исключило . возможность влияния неисправностей контролирующего блока на заключение об исправности контролируемого блока. 1 ил. § (Л

| Устройство для контроля блоков оперативной памяти | 1979 |

|

SU888211A1 |

| Солесос | 1922 |

|

SU29A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU926725A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-02-28—Публикация

1984-01-26—Подача