(5i) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1410033A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957276A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| Устройство для ввода информации | 1987 |

|

SU1529208A1 |

| Устройство для контроля оперативной конвейерной памяти | 1989 |

|

SU1633463A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

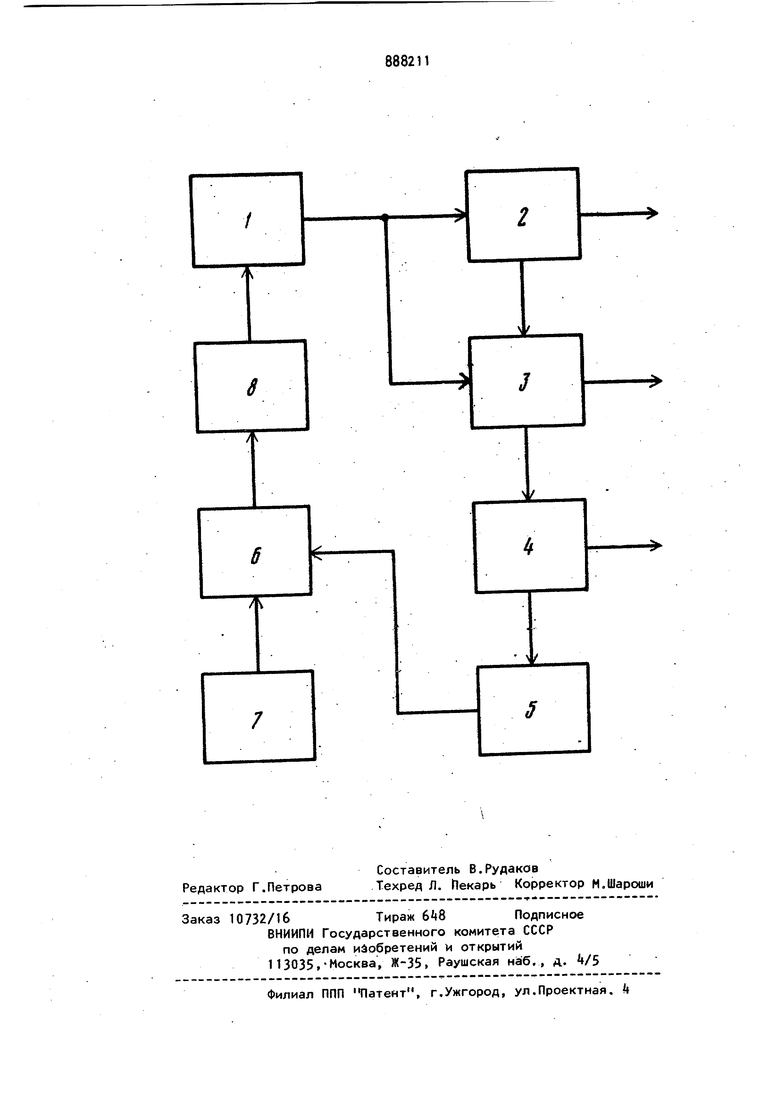

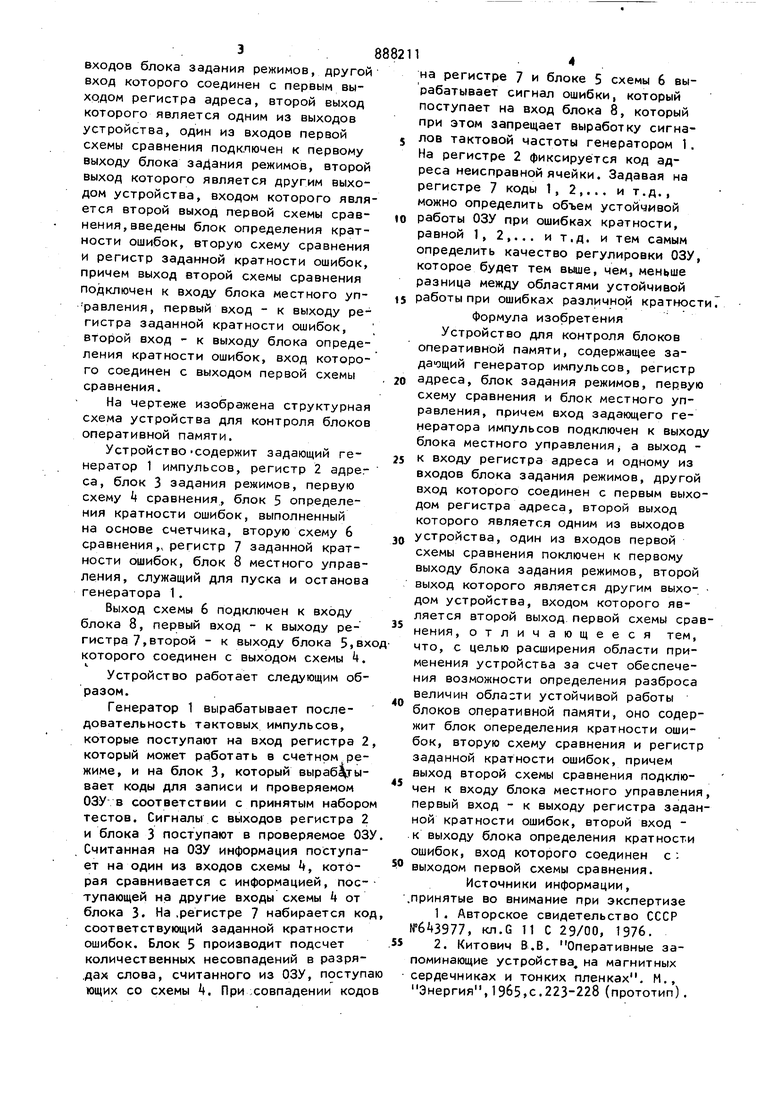

Изобретение относится к области запоминающих устройств. Известно устройство, которое содержит блок управления, счетчик адреса, схему сравнения, датчик контрольных кодов, регистр числа tl. Недостатком этого устройства явявляе тся возможность оценить качество регулировки оперативных запоминаю щих устройств (ОЗУ) в том смысле, чт на нем невозможно определить разброс величин области устойчивой работы отдельных разрядов и всего устройства в целом. Качество регулировки ОЗУ тем выше, чем меньше разница в облас тях устойчивой работы отдельных разрядов и устройства в целом. Наиболее близким техническим реше нием к изобретению является устройство для контроля ОЗУ, содержащее задающий генератор импульсов, генератор одиночных импульсов, генератор многократного обращения, схему останова, адресный регистр, схему задания режимов, схему сравнения, счетчик ошибок и схему растра 21 . В этом устройстве невозможно оценить качество-регулировки ОЗУ в вышеуказанном смысле, так как в нем происходит лишь фиксация ошибки без указания ее кратности. Это сужает область применения устройства. Целью изобретения является расширение области применения устройства замечет обеспечения возможности определения разброса величин области устойчивой работы блоков оперативной памяти. Поставленная цель дocтигaetcя тем, что в устройство для контроля блоков оперативной памяти, содержащее задающий генератор импульсов, регистр адреса, блок задания режимов, первую схему сравнения и блок местного управления, причем вход задающего генератора импульсов подключен к выходу блока местного управления, а выход к входу регистра адреса и одному ия 38 входов блока задания режимов, другой вход которого соединен с первым выхрдом регистра адреса, второй выход которого является одним из выходов устройства, один из входов первой схемы сравнения подключен к первому выходу блока задания режимов, второй выход которого является другим выходом устройства, входом которого является второй выход первой схемы сравнения, введены блок определения кратности ошибок, вторую схему сравнения и регистр заданной кратности ошибок, причем выход второй схемы сравнения подключен к входу блока местного управления, первый вход - к выходу регистра заданной кратности ошибок, второй вход - к выходу блока определения кратности ошибок, вход которого соединен с выходом первой схемы сравнения. На чертеже изображена структурная схема устройства для контроля блоков оперативной памяти. Устройство-содержит задающий генератор 1 импульсов, регистр 2 адре.са, блок 3 задания режимов, первую схему k сравнения, блок 5 определения кратности ошибок, выполненный на основе счетчика, вторую схему 6 сравнения , регистр 7 заданной кратности ошибок, блок 8 местного управления, служащий для пуска и останова генератора 1. Выход схемы 6 подключен к входу блока 8, первый вход - к выходу регистра 7,второй - к выходу блока 5,вх которого соединен с выходом схемы k. Устройство работает следующим образом. Генератор 1 вырабатывает последовательность тактовых импульсов, которые поступают на вход регистра 2 который может работать в c4etHpM.режиме, и на блок 3 который выраб тывает коды для записи и проверяемом ОЗУ в соответствии с принятым наборо тестов. Сигналы с выходов регистра 2 и блока 3 поступают в проверяемое ОЗ Считанная на ОЗУ информация поступает на один из входов схемы t, которая сравнивается с информацией, поступающей на другие входы схемы от блока 3. На .регистре 7 набирается ко соответствующий заданной кратности ошибок. Блок 5 производит подсчет количественных несовпадений в разря,дах слова, считанного из ОЗУ, поступ ющих со схемы k. При совпадении код на регистре 7 и блоке 5 схемы 6 вырабатывает сигнал ошибки, который поступает на вход блока 8, который при этом запрещает выработку сигнаов тактовой частоты генератором 1. На регистре 2 фиксируется код адреса неисправной ячейки. Задавая на регистре 7 коды 1, 2 ,. .. и т.д., можно определить объем устойчивой работы ОЗУ при ошибках кратности, равной 1, 2,... и т.д. и тем самым определить качество регулировки ОЗУ, которое будет тем выше, чем, меньше разница между областями устойчивой аботы при ошибках различной кратности. Формула изобретения Устройство для контроля блоков оперативной памяти, содержащее задающий генератор импульсов, регистр адреса, блок задания режимов, первую схему сравнения и блок местного управления, причем вход задающего генератора импульсов подключен к выходу блока местного управления, а выход к входу регистра адреса и одному из входов блока задания режимов, другой вход которого соединен с первым выходом регистра адреса, второй выход которого является одним из выходов устройства, один из входов первой схемы сравнения поключен к первому выходу блока задания режимов, второй выход которого является другим выхо- дом устройства, входом которого является второй выход.первой схемы сравнения, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности определения разброса величин области устойчивой работы блоков оперативной памяти, оно содержит блок опеределения кратности ошибок, вторую схему сравнения и регистр заданной кратности ошибок, причем выход второй схемы сравнения подключен к входу блока местного управления, первый вход - к выходу регистра заданной кратности ошибок, второй вход к выходу блока определения кратности ошибок, вход которого соединен с : выходом первой схемы сравнения. Источники информации, .принятые во внимание при экспертизе 1. Авторское свидетельство СССР №643977, кл.С 11 С 29/00, 1976. 2. Китович В.В. Оперативные запоминающие устройства, на магнитных сердечниках и тонких пленках. М., Энергия, 19б5,с.223-228 (прототип).

Авторы

Даты

1981-12-07—Публикация

1979-12-14—Подача