Фие.1

Изобретение относится к вычислительой технике, в частности к контролю запоинающих устройств, и может быть спользовано в серийном производстве и ри испытании запоминающих устройств.

Цель изобретения - повышение достоерности контроля памяти за счет обеспечеия дополнительных режимов контроля.

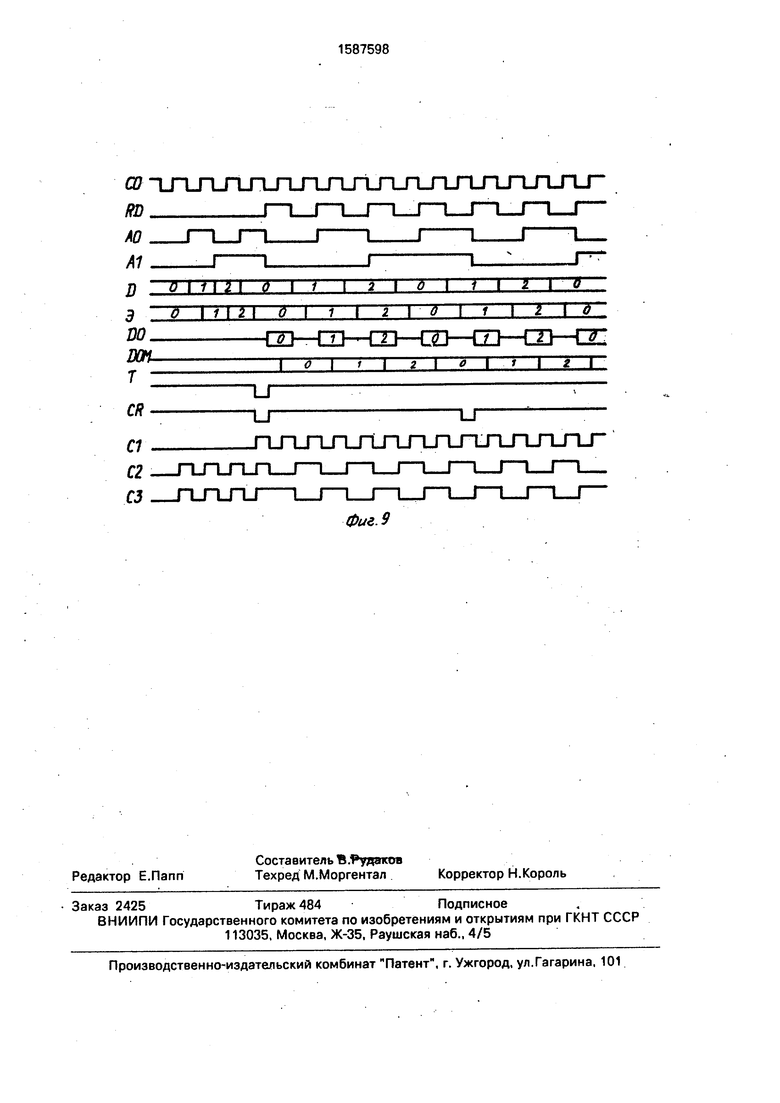

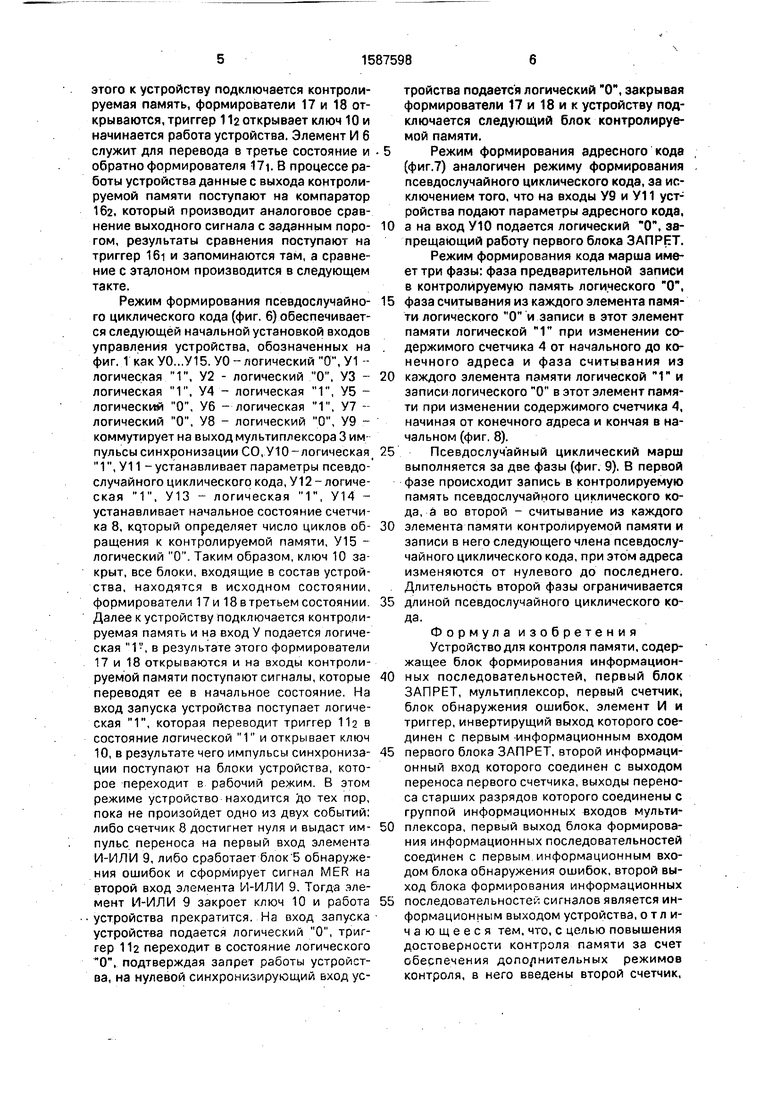

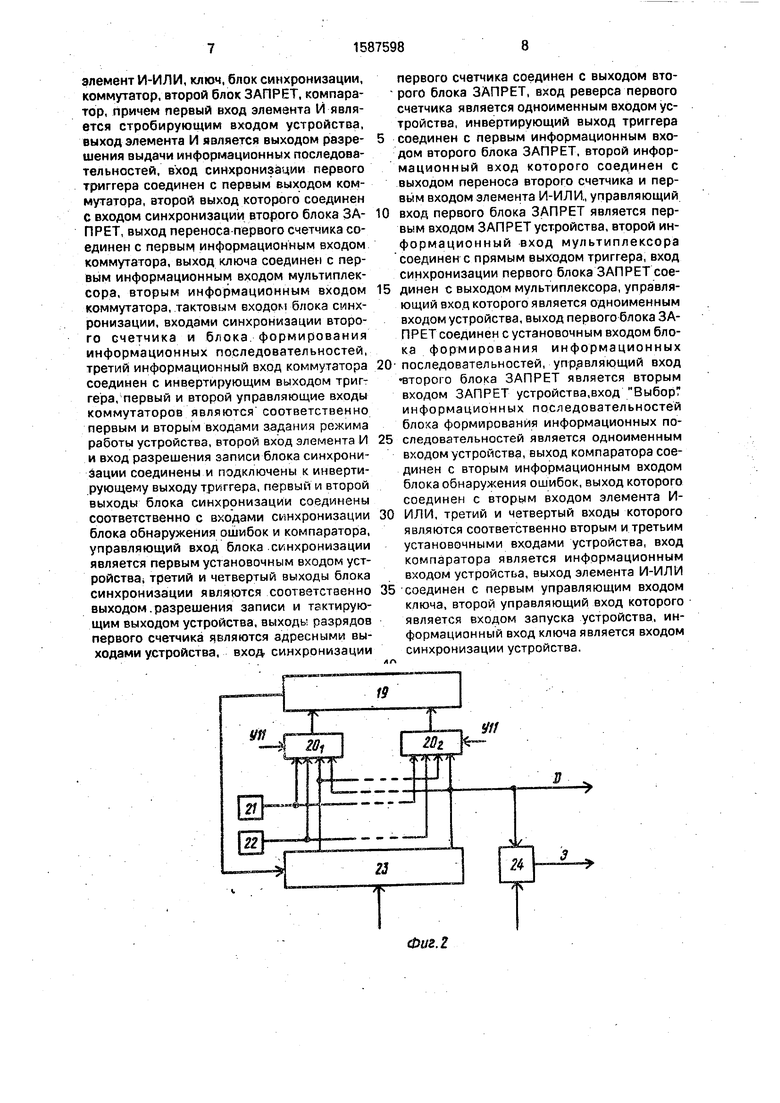

На фиг. 1 изображена структурная схеа устройства для контроля памяти; на фиг. -5 - структурные схемы блока формироваия информационных последовательностей фиг. 2), блока синхронизации (фиг. 3), комутатора (фиг. 4), формирователя (фиг. 5); на фиг. 6-9 - временные диаграммы работы устройства в режимах: псевдослучайный циклический код (фиг. 6), адресный код (фиг. 7), марш (фиг. 8) и псевдослучайный циклический марш (фиг. 9).

Устройство для контроля памяти (фиг. 1) содержит блок 1 формирования информационных последовательностей, первый блок ЗАПРЕТ 2, мультиплексор 3, первый счетчик 4 блок 5 обнаружения ошибок, элемент И 6, триггер 7, второй счетчик 8, элемент И-ИЛИ 9 ключ 10, состощий из ключевого элемента 111 и триггера 112. блок 12 синхронизации, коммутатор 13, второй блок ЗАПРЕТ 14. компаратор 15, состоящий из триггера 1б1 и

аналогового компаратора 1б2 и формирователи 171-173 и 18.

На фиг. 1 приняты следующие обозначения для входов устройства. УО - стробиру- ющий, У1 и У2 - соответственно первый и второй входы задания режима работы устройства, входы УЗ-Уб объединены и названы первым установочным входом, У7 - вход реверса, У8 - второй вход ЗАПРЕТ. У9 управляющий вход, УЮ - первый вход ЗАПРЕТ У11 - вход Выбор информационных последовательностей, У12 и У13 - соответственно второй и третий установочные входы, У14 - вход сброса, У15 - вход запуска. Блок.1 формирования информационных

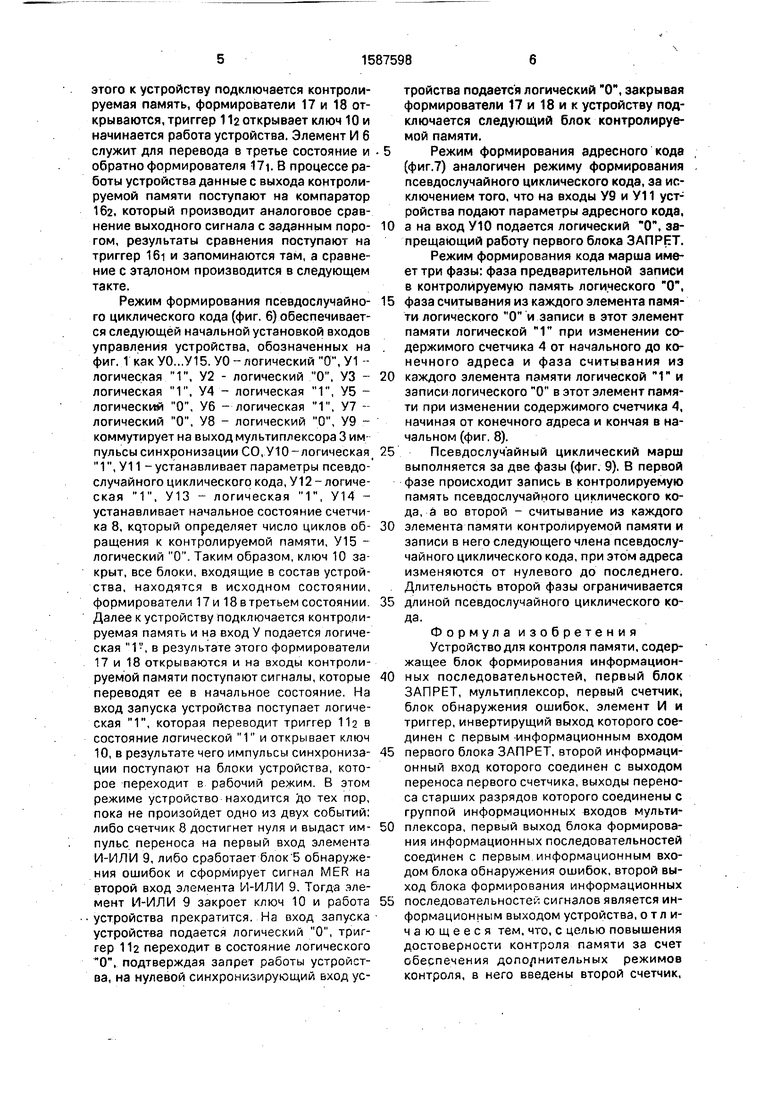

последовательностей (фиг. 2)содержит сумматор 19 по модулю два, коммутаторы 20 по числу входов сумматора, формирователь 21 логического О, формирователь 22 огиче- ской 1, регистр 23 сдвига и триггер 24.

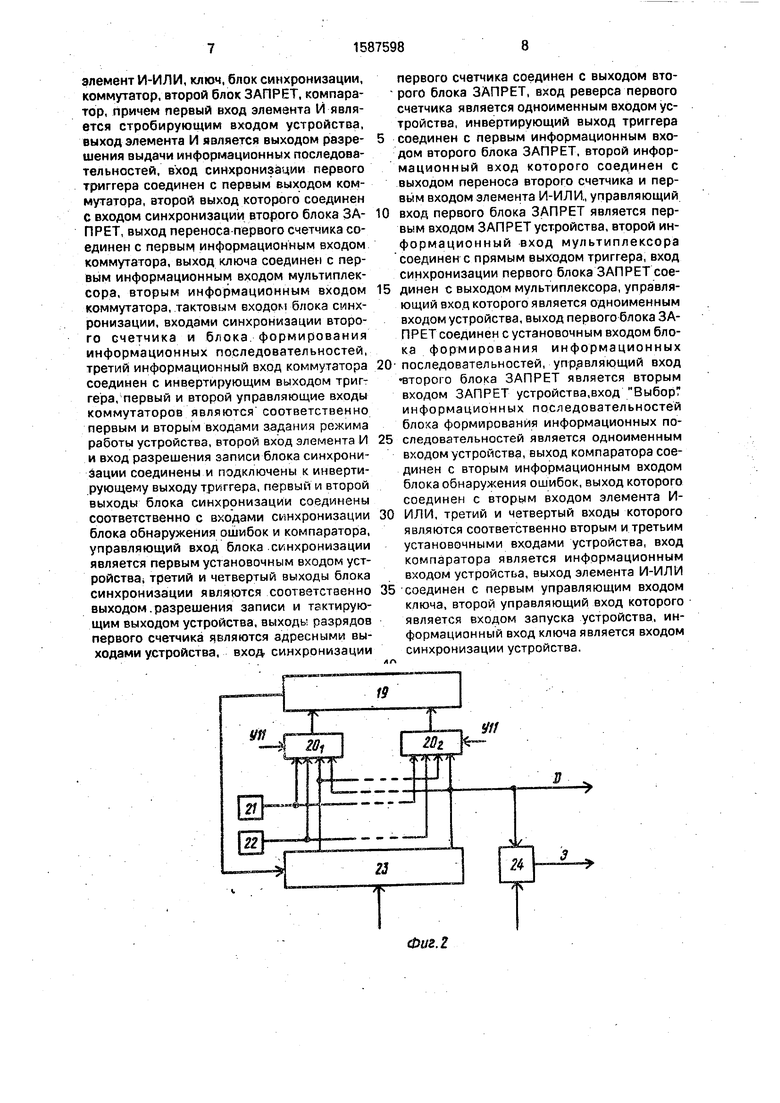

Блок синхронизации (фиг. 3) содержит с первого по шестой элементы И 25i-256, элемент И-НЕ 26, первый элемент И 27i второй элемент И 272, первый элемент И-НЕ 281 второй элемент И-НЕ 282, триггер 29, ; первый элемент ИСЮ1ЮЧАЮЩЕЕ и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

302

Коммутатор 13 (фиг. 4) содержит первый элемент И-ИЛИ 311, и второй элемент И- ИЛИ312.

5

10 15 20

.

В качестве компаратора 16 может быть использован триггер Шмитта.

Формирователь 17 (фиг, 5) содержит первый элемент И-НЕ 32i, второй элемент И-НЕ 322, первый усилитель 33i напряжения, второй усилитель ЗЗг. первый ключ 34i

и второй ключ 342.

Устройство работает следующим образом.

К предварительно установленным в третье состояние формирователям 17 и 18 подключены входы блока контролируемой памяти (не показан), выходы которого подключены к компаратору 162, счетчик 8 уста- новлен в начальное состояние, с которого он начинает счет в процессе работы устройства, а когда достигает нулевого состояния, формирует на своем выходе сигнал переноса. Этот сигнал вместе с выходным сигна- лом блока 5 поступает на элемент И-ИЛИ 9, на выходе которого формируется уровень, запирающий ключ 10, итем самым запрещающий дальнейшую работу устройства.

Перед началом работы устройства на управляющие входы необходимо подать соответствующие сигналы, которые устанавливают блоки устройства в требуемый режим, после этого на информационный вход триггера 112 подается уровень логиче- 0 ской 1-й ключ 10. открываясь, разрешает поступление синхроимпульсов на блоки устройства. Вследствие этого блок 1. блок ЗАПРЕТ 2 и мультиплексор 3 формируют информационную последовательность, ко- 5 торая через формирователь 17 поступает на информационные входы контролируемой памяти, а также эталонную последовательность с которой в блоке 5 сравниваются выходные данные, поступающие через ком- 0 паратор 15 с выходов контролируемой памяти Счетчик 4 совместно с коммутатором 1J и блоком ЗАПРЕТ 14 формирует адресную последозательнбсть, поступающую на формирователь 18. Триггер . 7 формирует сигнал 5 Запись-считывание. необходимый для работы устройства в режимах записи информации в контролируемую память, считывания данных из контролируемой памяти и сравнения их с эталоном. Блок U 50 синхронизации вырабатывает служебн ые сигналы: разрешения записи и тактовый, а также импульсы синхронизации для блока 5, триггера 1б1. Формирователи 17и 18выпол- няют функцию сопряжения устройства с 55 контролируемой памятью, формируя электрические сигналы в виде импульсов напряжения с заданной амплитудой и длительностью фронта и спада. Перед началом работы устройства формирователи 17 и 10 устанавливаются в третье состояние, после

того к устройству подключается контролиуемая память, формирователи 17 и 18 открываются, триггер 112 открывает ключ 10 и начинается работа устройства. Элемент И 6 лужит для перевода в третье состояние и обратно формирователя 17i. В процессе работы устройства данные с выхода контролируемой памяти поступают на компаратор 1б2, который производит аналоговое сравнение выходного сигнала с заданным порогом, результаты сравнения поступают на триггер 16i и запоминаются там, а сравнение с эталоном производится в следующем такте.

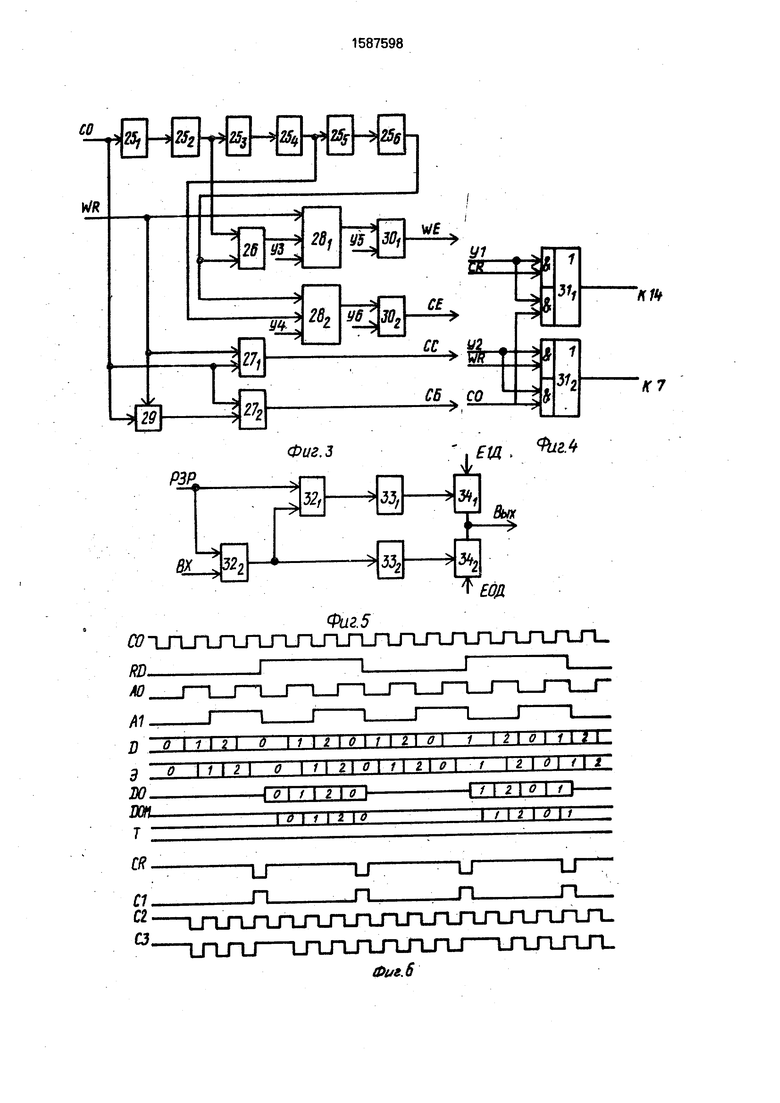

Режим формирования псевдослучайного циклического кода (фиг. 6) обеспечивается следующей начальной установкой входов управления устройства, обозначенных на фиг. 1 как УО...У15. УО - логический О, У1 - логическая 1, У2 - логический О, УЗ - логическая 1, У4 - логическая 1, У5 - логический О, У6 - логическая 1, У7 - логический О, У8 - логический О, У9 - коммутирует на выход мультиплексора 3 импульсы синхронизации СО,У10-логическая 1, У11 -устанавливает параметры псевдослучайного циклического кода, У12-логическая 1, У13 - логическая 1, У14 - устанавливает начальное состояние счетчика 8, крторый определяет число циклов обращения к контролируемой памяти, У15 - логический О. Таким образом, ключ 10 закрыт, все блоки, входящие в состав устройства, находятся в исходном состоянии, формирователи 17и 18 втретьем состоянии. Далее к устройству подключается контролируемая память и на вход У подается логическая 1-, в результате этого формирователи 17 и 18 открываются и на входы контролируемой памяти поступают сигналы, которые переводят ее в начальное состояние. На вход запуска устройства поступает логическая 1, которая переводит триггер 112 в состояние логической 1 и открывает ключ 10, в результате чего импульсы синхронизации поступают на блоки устройства, которое переходит в рабочий режим. В этом режиме устройство находится до тех пор, пока не произойдет одно из двух событий: либо счетчик 8 достигнет нуля и выдаст импульс переноса на первый вход элемента И-ИЛИ 9, либо сработает блок 5 обнаружения ошибок и сформирует сигнал MER на второй вход элемента И-ИЛИ 9. Тогда элемент И-ИЛИ 9 закроет ключ 10 и работа устройства прекратится. На вход запуска устройства подается логический О, триггер 112 переходит в состояние логического О, подтверждая запрет работы устройства, на нулевой синхронизирующий вход устройства подается логический О, закрывая формирователи 17 и 18 и к устройству подключается следующий блок контролируемой памяти.

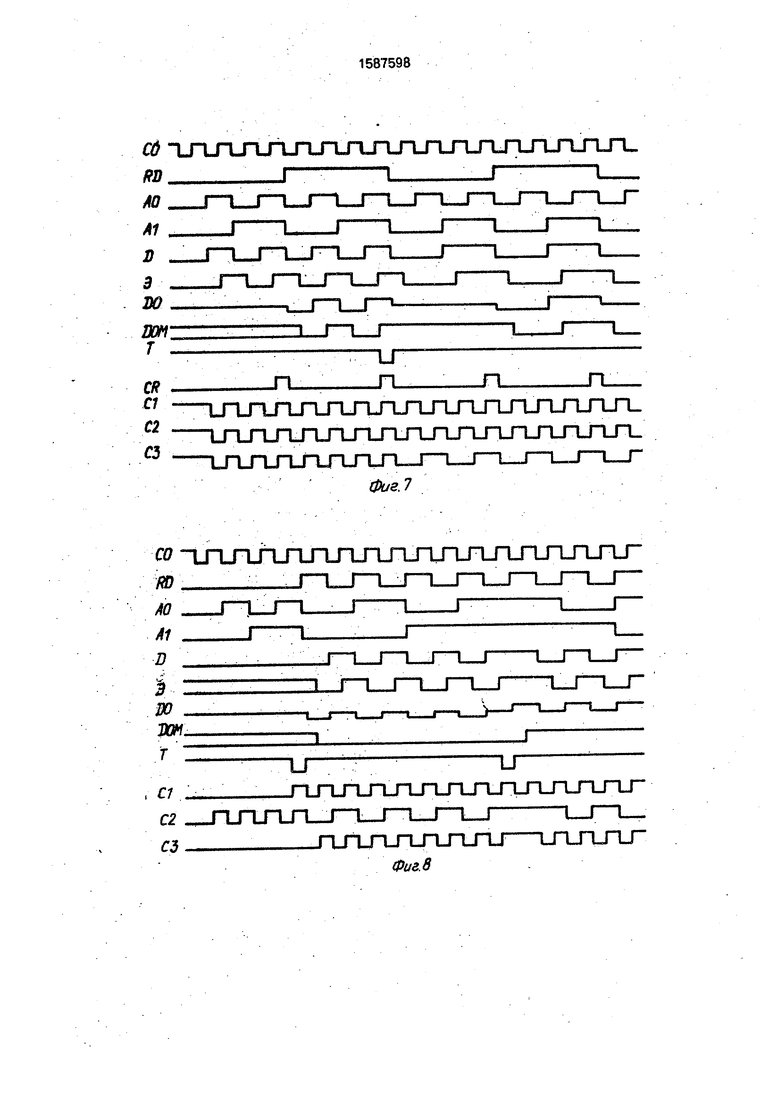

5 Режим формирования адресного кода (фиг.7) аналогичен режиму формирования псевдослучайного циклического кода, за исключением того, что на входы У9 и У11 устройства подают параметры адресного кода,

0 а на вход У10 подается логический О, запрещающий работу первого блока ЗАПРЕТ. Режим формирования кода марша имеет три фазы: фаза предварительной записи в контролируемую память логического О,

5 фаза считывания из каждого элемента памяти логического О и записи в этот элемент памяти логической 1 при изменении содержимого счетчика 4 от начального до конечного адреса и фаза считывания из

0 каждого элемента памяти логической 1 и записи логического О в этот элемент памяти при изменении содержимого счетчика 4, начиная от конечного адреса и кончая в начальном (фиг. 8).

5Псевдослучайный циклический марш

выполняется за две фазы (фиг. 9). В первой фазе происходит запись в контролируемую память псевдослучайного циклического кода, а во второй - считывание из каждого

0 элемента памяти контролируемой памяти и записи в него следующего члена псевдослучайного циклического кода, при этом адреса изменяются от нулевого до последнего. Длительность второй фазы ограничивается

5 длиной псевдослучайного циклического кода.

Формула изобретения Устройство для контроля памяти, содержащее блок формирования информацион0 ных последовательностей, первый блок ЗАПРЕТ, мультиплексор, первый счетчик, блок обнаружения ошибок, элемент И и триггер, инвертирущий выход которого соединен с первым -информационным входом

5 первого блока ЗАПРЕТ, второй информационный вход которого соединен с выходом переноса первого счетчика, выходы переноса старших разрядов которого соединены с группой информационных входов мульти0 плексора, первый выход блока формирования информационных последовательностей соед инен с первым информационным входом блока обнаружения ошибок, второй выход блока формирования информационных

5 последовательностей сигналов является информационным выходом устройства, отличающееся тем, что, с целью повышения достоверности контроля памяти за счет обеспечения допо/1нительных режимов контроля, в него введены второй счетчик.

элемент И-ИЛИ, ключ, блок синхронизации, коммутатор, второй блок ЗАПРЕТ, компаратор, причем первый вход элемента И является стробирующим входом устройства, выход элемента И является выходом разрешения выдачи информационных последовательностей, вход синхронизации первого триггера соединен с первым выходом коммутатора, второй выход которого соединен С входом синхронизации второго блока ЗАПРЕТ, выход переноса первого счетчика соединен с первым информационным входом коммутатора, выход ключа соединен с первым информационным входом мультиплексора, вторым информационным входом коммутатора, тактовым входом блока синхронизации, входами синхронизации второго счетчика и блока, формирования информационных последовательностей, третий информационный вход коммутатора соединен с инвертирующим выходом триггера, первый и второй управляющие входы коммутаторов являются соответственно первым и вторым входами задания режима работы устройства, второй вход элемента И и вход разрешения записи блока синхронизации соединены и подключены к инвертирующему выходу триггера, первый и второй выходы блока синхронизации соединены соответственно с входами синхронизации блока обнаружения ошибок и компаратора, управляющий вход блока синхронизации является первым установочным входом устройства; третий и четвертый выходы блока синхронизации являются соответственно выходом.разрешения записи и тактирующим выходом устройства, выходы разрядов первого счетчика являются адресными выходами устройства, вход, синхронизации

ервого счетчика соединен с выходом вто- ого блока ЗАПРЕТ, вход реверса первого четчика является одноименным входом усройства, инвертирующий выход триггера соединен с первым информационным входом второго блока ЗАПРЕТ, второй информационный вход которого соединен с выходом переноса второго счетчика и первым входом элемента И-ИЛИ., управляющий вход первого блока ЗАПРЕТ является первым входом ЗАПРЕТ устройства, второй информационный вход мультиплексора соединен с прямым выходом триггера, вход синхронизации первого блока ЗАПРЕТ сое- динен с выходом мультиплексора, управляющий вход которого является одноименным входом устройства, выход первого блока ЗАПРЕТ соединен с установочным входом блока формирования информационных последовательностей, упр авляющий вход второго блока ЗАПРЕТ является вторым входом ЗАПРЕТ устройства,вход Выбор информационных последовательностей блоха формирования информационных по- следовательностей является одноименным входом устройства, выход компаратора соединен с вторым информационным входом блока обнаружения ошибок, выход которого соединен с вторым входом элемента И- ИЛИ, третий и четвертый входы которого являются соответственно вторым итретьим установочными входами устройства, вход компаратора является информационным входом устройства, выход элемента И-ИЛИ соединен с первым управляющим входом ключа, второй управляющий вход которого является входом запуска устройства, информационный вход ключа является входом синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1987 |

|

SU1513525A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

Изобретение относится к вычислительной технике и может быть использовано для обеспечения контроля памяти в режиме считывания-модификации-записи при испытании запоминающих устройств. Цель изобретения - повышение достоверности контроля памяти за счет обеспечения дополнительных режимов контроля. Устройство содержит блок 1 формирования информационных последовательностей, блоки ЗАПРЕТ 2 и 14, мультиплексор 3, счетчики 4 и 8, блок 5 обнаружения ошибок, элемент И 6, элемент И-ИЛИ 9, триггер 7, ключ 10, блок 12 синхронизации, коммутатор 13, компаратор 15, формирователи 17 и 18. Устройство позволяет формировать следующие алгоритмы функционального контроля: адресный код, псевдослучайный циклический код, последовательная запись-считывание, марш, псевдослучайный циклический марш. 9 ил.

У/У

20i

20i

yii

fe-

fc k Л /

5

Фиг. 2

Фиг.з

вх .,

Фиг. 5

ЕШ.

гА

(.6

С TjTjijTjarijajijajTJ jn-n

IfD АО A1 D

CO nJTJTJXnJ JTJlJTJ JlJ RD

Фиг.7

О Tj JiJTJOJiJTnjiJiJTJTJTJ

RD АО

A1I П Г 11-Л

D Д I 1 Д 2 д I i О Э I И Л ( I I I I f I г 1 DOCZh-СГ

/m. r . I I г I 2 I

С/

иu

J-lJnjnjlJ4JnjnJlJTJlJTJT-rLr

Фиг. 9

| Устройство для контроля памяти | 1985 |

|

SU1367045A1 |

| Устройство для контроля памяти | 1987 |

|

SU1513525A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-08-23—Публикация

1987-12-03—Подача