Изобретение относится к технике передачи дискретной инф рмации и может быть использопано п пппаратуре сеансной сняяи ;uin iticijivinpoBainiH и ириема сигналов начала сообщения.

Целью изобретения яп.чяется расширение функциональных ночможностеГ устройства передачи за счет обеспечения приема сигналов адресной начальной синхронизации,

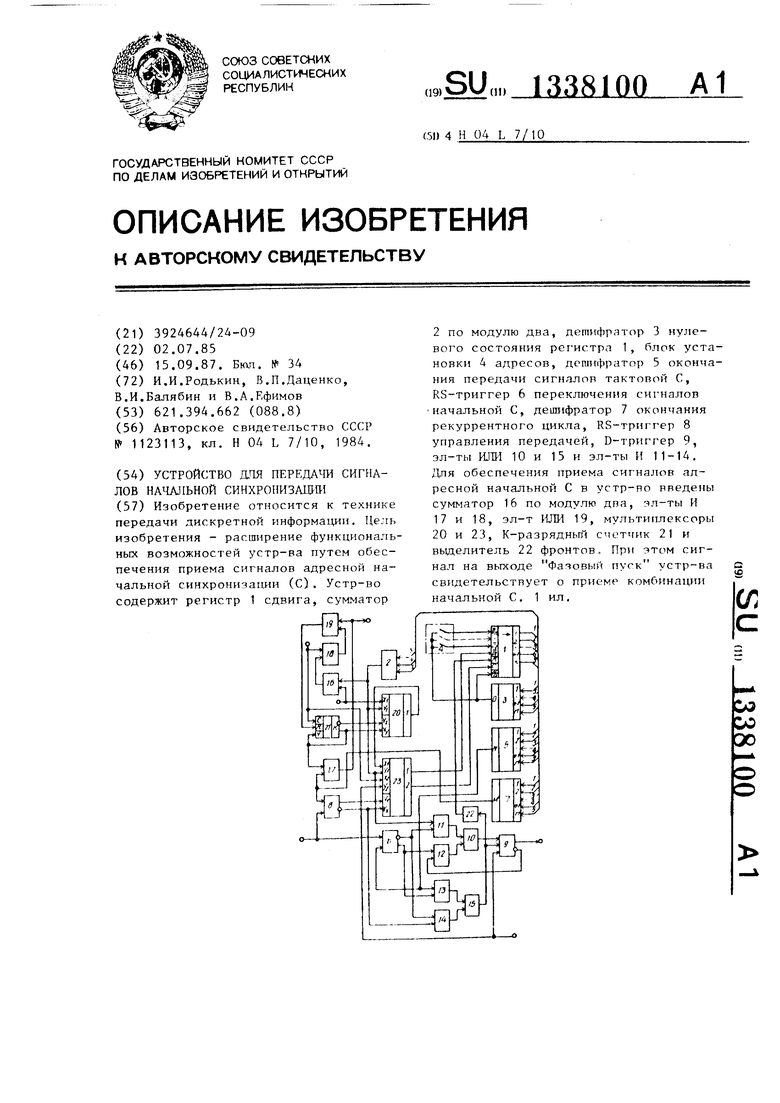

На чертеже пре;-(с.тавлена схема уст- poiicTHa для передачи спг на.чов начальной с.инхроничапии .

Устройство содержит регистр 1 сдвига, первый сумматор 2 по модулю два, деи1ифратор 3 нулевопт состояния регистра сдвига, Плок А установки адресов, дешифрато;) 5 окончания nepii- дачи сигна.ча тактовсп С11нхр знитации, KS-триггер 6 переключе1П я си1Л1алов начал{Л1о;1 синхрон}гчаг;ии, дешифратор 7 оконча}П1я рекурреи 1 гюго цикла, RS- триггер 8 управления передачей, D- триггер 9, nepBbiii элемент ШЖ 10, перв1 п 1 - четверть элеменгы И 11 - 1А, втор(тй э.чемент 11J11 15, второ) сумматор 16 по .)дyлк) два, тгчтый 17 и шестой 13 :1чеме)пы И, третий г)леIIJD1 19, первь мульт1П лексор 20, зо с входа Такт передачи устро 1ства.

мент

К-разрядвы счетчик 21, вь де;п1тель 22

фронтов, пторо мульт 1 лексор 23.

Устро и тво работает следут |им образом.

В исходном состоянии RS-триггер 3 управления 1ере.ачей т КЯ-тригч-ер 6 переки ючения с Ч1алов начальной син- хро 1изапи -1 н.чх(- ятся в нулевом состоянии, что мает на/1ич 1е на выходе 4ei4U ;v т.чемента И 14, которь Й через вторш г элемент ИЛИ 15 удерживает в псход)ом состоянии D- триггер 9 и че С з ны,те,г1ите; ь 22 фрон- ТС1В устанав.пинает в псходно1/ состоя- регчп тр 1 по R-входам.

При поступлении сиг нала на вход Пуск yc .TpoiicTBa RS-триггер 8 и RS-триггер (- устанавливаются по S- входам в единичное с-.остояние, разрешая раС)оту П-т|5И1 гера О п рет истра 1 . При этом за счет подачи сигнала с прямого выхода RS-триггера 6 на первый вход pToiioro т.чемента Н 12 обес 1ечивае гея связг D-входа D-триг- гера 9 со своим инверсным выходом через нервый элемент ИЛИ 10. D-Tpnr гер 9 начинает работать в режиме деления частоты тактовьпч. импульсов на два, обеспечивая формироватше на вы35

К)

45

50

55

При записи адреса в ,тр 1 прекр :цае гея де11 ифрация сигва.иа yj4eBoro с:с5стояния и осушеств.чяется переключ ние режима записи информации в регистр 1 с параллельного на последов те.1,ный за счет смень значе1П1я сигна .ча на p/s-BX(Mu; ре чп:тра 1. По ос;та- тактовь м мг ульсам Г)су1цествля- ется формпрование рекуррентно комби нации в соответстви с установл(нны- ми через nei iBi- сумматор 2 обратнь ми связями выходов разрядов р(МЧ1стра 1 с D-входом первого разряда 1)егистра

Дешифратор 5 формирует с 1гнал при образовании на выходах разрядов стра 1 рекуррентной комбинации, соот ветствующей окончан 1ю времени переда чи сигнала тактовой синхронизаци в виде точек с выхода D-тригг ера 9.

Сигнал с леи1 1фраторл 5 тупает на R-вход RS-триггера 6 и вход третьег о элемента И 13, устанав .чивая в исходное состояние R5-Tpiir- гер 6, D-триггер 9 и регистр 1 за счет образования сигнала на В1.1ходе третьего э: емента И 13 и второго эле мента ИЛИ 15 и сигнала на Bbixojie 22 фронтов. Установка KS- т; 1ггера 6 ,вает отк.( 1)

Х(5де Передача ycTpoiicTBa сиглшла начально синхро}П1чапии в точек.

Установка в нулевое С(5стояние jie- гистра 1 В1.1зывает появ-гичгие сигнала на выхолде дешифратора 3, который через блок 4 установки поступает на D-входы всех разрядов, кроме перво о P/S-ВХОД установки режима записи регистра 1.

Выходные сигналы с выхода RS-триг- гера 8 обеспечивают включе1П1е У-кана- лов второго мульт птлекс( ра 23. При

этом по первому каналу обеспечивается связь D-входа первого разряда регистра 1 с выходом первого сумматора 2, а по второму кавалу обеспечивается подача на Овход регистра 1 1мпульL OB с входа Такт передачп устро - ства.

По первому тактовому импульсу после с 1гнала Пуск в регистр 1 осуществляется параллельная запись адреса

путем подачи сигнала с выхода ратора 3 на P/S-BXC T установки режима и через блок 4 уста1говки на соответствующие D-входы регистра 1 и тактового импульса на С-вхо/ч 1)егпстра 1

5

)

5

0

5

При записи адреса в ,тр 1 прекра- :цае гея де11 ифрация сигва.иа yj4eBoro с:с5стояния и осушеств.чяется переключение режима записи информации в регистр 1 с параллельного на последова- те.1,ный за счет смень значе1П1я сигна- .ча на p/s-BX(Mu; ре чп:тра 1. По ос;та- тактовь м мг ульсам Г)су1цествля- ется формпрование рекуррентно комбинации в соответстви с установл(нны- ми через nei iBi- сумматор 2 обратнь ми связями выходов разрядов р(МЧ1стра 1 с D-входом первого разряда 1)егистра 1 .

Дешифратор 5 формирует с 1гнал при образовании на выходах разрядов стра 1 рекуррентной комбинации, соответствующей окончан 1ю времени передачи сигнала тактовой синхронизаци в виде точек с выхода D-тригг ера 9.

Сигнал с леи1 1фраторл 5 тупает на R-вход RS-триггера 6 и вход третьег о элемента И 13, устанав- .чивая в исходное состояние R5-Tpiir- гер 6, D-триггер 9 и регистр 1 за счет образования сигнала на В1.1ходе третьего э: емента И 13 и второго элемента ИЛИ 15 и сигнала на Bbixojie 22 фронтов. Установка KS- т; 1ггера 6 ,вает отк.( 1)-ч хо 1338

да D-тряггера 9 от собственпсич инверсного выхода за счет снятия сигнала с первого входа второго элемента И 12, соединенног о с выходом RS-тригтера 6, и подклкпшние его к выходу первого сумматора 2 за счет подачи сигнала с инверсного выхода RS-триггера 6 на BTopoi вход первого

20

25

элемента И 11. С поступлением очеред- IQ ема через inecToii элемент И 18 и TJU-- ного тактового импульса начинается процесс формирования рекуррентной последовательности с адреса, которьи вводится через блок 4 установки. Сигналы этой последовательности поступают на D-вход В-трип ера 9 и далее под действием тактовых импульсов передачи, поступаюгш х на С-вход D-триг- гера 9, на выход Передача устройства.

Процесс формирования рекуррентной последовательности осуществляется до появления на выходах регистра 1 ко- нечноР комбинации, при которой дешифратор 7 формирует сигнал, поступающий на R-вход RS-триггера 8. Установка RS-триггера 8 по R-входу приводит к окончанию передачи сигнала начальной синхронизации за счет установки в нулевое состояние по R-входу В-тригг-ера 9.

Установка RS-триггера 8 в нулевое состояние приводит к изменению значений сигналов управления второго мультиплексора 23 и включению Х-ка- налов этого т льтиплексора. При этом D-вход первог о разряда регистра 1 подключается к выходу первого мультиплексора 20 и С-вход - к входу Такт приема устройства.

Прием сигнала начальной синхронизации устройства начинается с поступления сиг налов на входы Прием и Такт приема. В исходном состоянии

тий элемент L lH 19 на установочный вход К-разрядного счегчика 21 но поступают и 13 счетчике 21 осуществляется счет этих импуттьсов, поступающих н;)

15 .

При наличии искажений элемент(М комбинации началЕ но11 гинхрониз.чпии яа выходе второго сумматора 16 формируются сиг-на.п,1, разрешающие прохождение импульсов с вхо;;а Тлкт приема устройства на R-вход К-ра ря;1Ного счетчика 21 для сброса резу 1ьтатов его счета. Если прием неискаженных элементов комбинации длится на протяжении К разрядов, формируется сигнал на прямом выхо;де FC-pn зря/тногч счетчика 21, KOTopiiiii тлпрепьче - дальи чИпи счет, поступая на V-вход. При -.-«том отключается Х-канал и no;;K:ii i4at гея

30 У-канал первого мультиплексора 20, обеспечивая отк.чючеилс )(1л,; jiep- вого разряда регистра 1 viT пхода Прием ycTpoi icTTui п ; --;и-. iK. ei o к выходу сумматора 2. С г1ч.1Ч) MCJMOH- та на выходе первог о суг-:магор;; 2 формируется автономная pcKyjijieH г. пос.чедовательнос ть . luipMiipi-jiiiHue пчтй последовательности -.суь ич-тнлнется до тех пор, пока на В1лло;;ах разрядов регистра 1 не ::ояр.г1ястся ксч1счн; я комбинация, которую (5бнаруж1гг )- ратор /. При этом на его выходе сформируется сигнал, который проходит через пятый элемент И 17 на выход

35

10

К-разрядный счетчик 21 своим вьгходным Фазовый пуск устроГ1С-|Л5а,

нулевым сигналом подключает Х-канал первого мультиплексора 20, соединяя D-вход первого рег истра 1 с входом Прием устройства. Первым тактовым импульсом приема, поступившим на С-вход регистра 1. осуществляется запись в него адреса и переключение режима записи с параллельного на пос- лел.овательный сигнал с выхода дешифратора 3. Остальными тактовыми им- пучьсами приема осуществляется формирование рекуррентной последовательности с учетом информации, поступающей с RXfv ia Прием устройства на D-вход

50

55

ввиду наличия сигнала на дру1 ONJ вхол,е элемента И 17, подаваемого с прямого выхода К-разрядно о счетчика 21. Этот же сигнал, поступая третиГг элемент ШБ1 19 на R-BXCVT К-11азрядног(1 счетчика 21, устанав.пипает его в нулевое состояние. Сигн,1,ч ira выходе Фазовый пуск устроиства свидетел.- ствует о приеме К омби)1лци11 нача. плю) синхронизации. При :vi4iM К-ра 1)яднь11Й счетчик 21 устанавливается в нулевое состояние, что обеспечивает полключе- ние Х-канала первогсч MN /HI ; ini/ifKccipa 20 и готовность ycTiioiu i :j,-i i-- пр иему

гк рвого разряд;) рсгис-ч рл 1. i- емая инфор мация во uTojioNt гVMNi.rt opi 16 сравнивлется с ;), pei-vp- рентнсм последоватьIIьиости, фор-ичруе- MOI1 в регистре I. В сиучпе полног-о совпадения с:игнал на гпчтрогр сумматора 16 все TJIU-NUI paiiCii . При этом импульсы с входа Так1 при

ема через inecToii элемент И 18 и TJU--

тий элемент L lH 19 на установочный вход К-разрядного счегчика 21 но поступают и 13 счетчике 21 осуществляется счет этих импуттьсов, поступающих н;)

.

При наличии искажений элемент(М комбинации началЕ но11 гинхрониз.чпии яа выходе второго сумматора 16 формируются сиг-на.п,1, разрешающие прохождение импульсов с вхо;;а Тлкт приема устройства на R-вход К-ра ря;1Ного счетчика 21 для сброса резу 1ьтатов его счета. Если прием неискаженных элементов комбинации длится на протяжении К разрядов, формируется сигнал на прямом выхо;де FC-pn зря/тногч счетчика 21, KOTopiiiii тлпрепьче - дальи чИпи счет, поступая на V-вход. При -.-«том отключается Х-канал и no;;K:ii i4at гея

У-канал первого мультиплексора 20, обеспечивая отк.чючеилс )(1л,; jiep- вого разряда регистра 1 viT пхода Прием ycTpoi icTTui п ; --;и-. iK. ei o к выходу сумматора 2. С г1ч.1Ч) MCJMOH- та на выходе первог о суг-:магор;; 2 формируется автономная pcKyjijieH г. пос.чедовательнос ть . luipMiipi-jiiiHue пчтй последовательности -.суь ич-тнлнется до тех пор, пока на В1лло;;ах разрядов регистра 1 не ::ояр.г1ястся ксч1счн; я комбинация, которую (5бнаруж1гг )- ратор /. При этом на его выходе сформируется сигнал, который проходит через пятый элемент И 17 на выход

Фазовый пуск устроГ1С-|Л5а,

50

55

ввиду наличия сигнала на дру1 ONJ вхол,е элемента И 17, подаваемого с прямого выхода К-разрядно о счетчика 21. Этот же сигнал, поступая третиГг элемент ШБ1 19 на R-BXCVT К-11азрядног счетчика 21, устанав.пипает его в нулевое состояние. Сигн,1,ч ira выходе Фазовый пуск устроиства свидетел.- ствует о приеме К омби)1лци11 нача. плю) синхронизации. При :vi4iM К-ра 1)яднь11Й счетчик 21 устанавливается в нулевое состояние, что обеспечивает полключе- ние Х-канала первогсч MN /HI ; ini/ifKccipa 20 и готовность ycTiioiu i :j,-i i-- пр иему

либо к передаче комбинации нача- П)Н011 синхронизации.

Формула из

обретения

Устройство для передачи сигналов начальной синхронизации, содержащее регистр сдвига, выходы разрядов которого подключены к входам первого сумматора по модулю два, дешифратора нулевого состояния регистра сдвига, выход которого через блок установки адресов подключен к всем D-входам регистра сдвига, кроме первого, дешифратора окончания передачи сигнала тактовой синхронизации, выход которого подключен к R-входу RS-триггера переключения сигналов начальной синхронизации, дешифратора окончания рекуррентного цикла, выход которого подключен к R-входу RS-триггера управления передачей, S-вход которого соединен с S-входом RS-триггера переключения сигналов начальной синхронизации и является входом сигнала Пуск устройства, прямой выход D-триггера является выходом Передача устройства, D-вход В-триг1-ера подключе к выходу первого элемента ИЛИ, два входа которого подключены соответственно к вьосодам первого и второго элементов И, первые входы которых подключены соответственно к инверсному и прямому выходам RS-триггера переключения сигналов начальной синхронизации и к первым входам четвертого и третьего элементов И, выходы которых подключены соответственно к пер45

вому и второму входам второго элемен- ,,,,) Ц, входу второго сумматора по модулю та ИЛИ, выход которого подключен к R--вxoдy D-триггера, инверсный выход которого подключен к второму входу второго элемента И, второй вход третьего элемента И подключен к выходу дешифратора окончания передачи сигнала тактовой синхронизации, второй вход четвертого элемента И подключен к инверсному выходу RS-триггера управления передачей, С-вход D-тригг ера является входом Такт передачи устройства, входы дешифраторов нулевого состояния регистра сдвига, окончания передачи сигнала тактовой синхрони- заш1и и окончания рекуррентног о цикла поразрядно объединены между собой и подключены к выходам соответствую- ВНИИПИ Заказ 4148/58

50

55

два и входу У-канала первого мультиплексора, вход Х-канала которог о является входом Прием устройства и подключен к другому входу второго сумматора по модулю два, выход которого подключен к второму входу шестого элемента И, выход которого подклю- че,н к другому входу третьего элемента ИЛИ, R-вход регистра сдвига через выделитель фронтов подключен к выходу второго элемента ИЛИ, входы управления второго мультиплексора подключены к инверсному и прямому выходам RS-триггера управления передачей, второй вход У-канала второго мультиплексора является входом Такт переустройства.

Подписное

дачи Тираж 638

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, А

5

0

5

0

35

щиу. разрядов рег истрл сднига, о т - л и ч а ю |ц е е с я тем, что, с целью расширения функциональных возможностей путем обеспечения приема сигналов адресной начал1 ной синхронизации, в него введены второй сумматор по модулю два, пятый п 1честой элементы И, третий элемент ИЛИ, К-разряд- ньй счетчик, выделитель фронтов, первый мультиплексор и втстрой мультиплексор, первый вход Х-канала которого подключен к выходу первого мультиплексора, входы управления которого подключены к инверсному и прямому выходам К-разрядного счетчика, R-вход которого подключен к выходу третьего элемента 1ШИ, один вход которого является выходом Фазовый пуск устройства и подключен к выходу пятого элемента И, один вход которого подключен к выходу дешифратора окончания рекуррентного цикла, а другой - к прямому выходу и V-входу К-разрядного счетчика, С-вход которого является входом Такт приема устройства, подключен к первому входу шестого элемента И и к второму входу Х-канала второго мультиплексора, первый вход которого подключен к D-входу первого разряда регистра сдвига, вход установки режима загшси которого подключен к вькоду дешифратора нулевого состояния рет истра сдвига, С-вход регистра сдвига подключен к второму выходу BTopoi o мультиплексора, первый вход У-канала которого подключен к выходу первого сумматора по модулю два, второму входу первог о элемента

45

,,,,) Ц, входу второго сумматора по модулю

50

55

два и входу У-канала первого мультиплексора, вход Х-канала которог о является входом Прием устройства и подключен к другому входу второго сумматора по модулю два, выход которого подключен к второму входу шестого элемента И, выход которого подклю- че,н к другому входу третьего элемента ИЛИ, R-вход регистра сдвига через выделитель фронтов подключен к выходу второго элемента ИЛИ, входы управления второго мультиплексора подключены к инверсному и прямому выходам RS-триггера управления передачей, второй вход У-канала второго мультиплексора является входом Такт переустройства.

Подписное

дачи ираж 638

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Устройство для передачи сигналов синхронизации | 1985 |

|

SU1241508A1 |

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Устройство для передачи сигналов начальной синхронизации | 1983 |

|

SU1123113A1 |

| Система передачи дискретной информации | 1985 |

|

SU1325719A1 |

| Устройство для приема сигналов начальной синхронизации | 1986 |

|

SU1427585A1 |

| Система передачи дискретной информации | 1986 |

|

SU1406806A1 |

| Устройство синхронизации с м-последовательностью | 1984 |

|

SU1218484A1 |

| Устройство для передачи сигналов начальной синхронизации | 1987 |

|

SU1533012A1 |

Изобретение относится к технике передачи дискретной информа1щи. Цель изобретения - расширение функциональных возможностей устр-ва путем обеспечения приема сигналов адресной начальной синхронизации (С). Устр-во содержит регистр 1 сдвига, сумматор 2 по модулю два, дешифратор 3 нулевого состояния рег истра 1 , блок установки 4 адресов, дешифратор 5 окончания передачи сигналов тактовой С, RS-триггер 6 переключения сигналов начальной С, дешифратор 7 окончания рекуррентного цикла, RS-триггер 8 управления передачей, D-триггер 9, эл-ты ИЛИ 10 и 15 и эл-ты И 11-14. Для обеспечения приема сигналов адресной начальной С в устр-но введены сумматор 16 по модулю два, эл-ты И 17 и 18, эл-т ИЛИ 19, мультиплексоры 20 и 23, К-разрядньй счетчик 21 и выделитель 22 фронтов,. При этом сигнал на выходе Фазовый пуск устр-ва свидетельствует о приеме комбинации начальной С, 1 ил. с (О (Л с

| Устройство для передачи сигналов начальной синхронизации | 1983 |

|

SU1123113A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-15—Публикация

1985-07-02—Подача