менй так, чтобы импульс на выходе элемента И 14 находился на середине 1-й половины интервала анализа, а импульс на выходе элемента И 15 - на середине 2-й половины этого интервала. Импульс на выходе делителя часИзобретение относится к телеграфной связи и может найти применение при построении моделей среднескорост- ных систем передачи дискретной ин- формации.

Цель изобретения - увеличение объема принимаемой информации. .

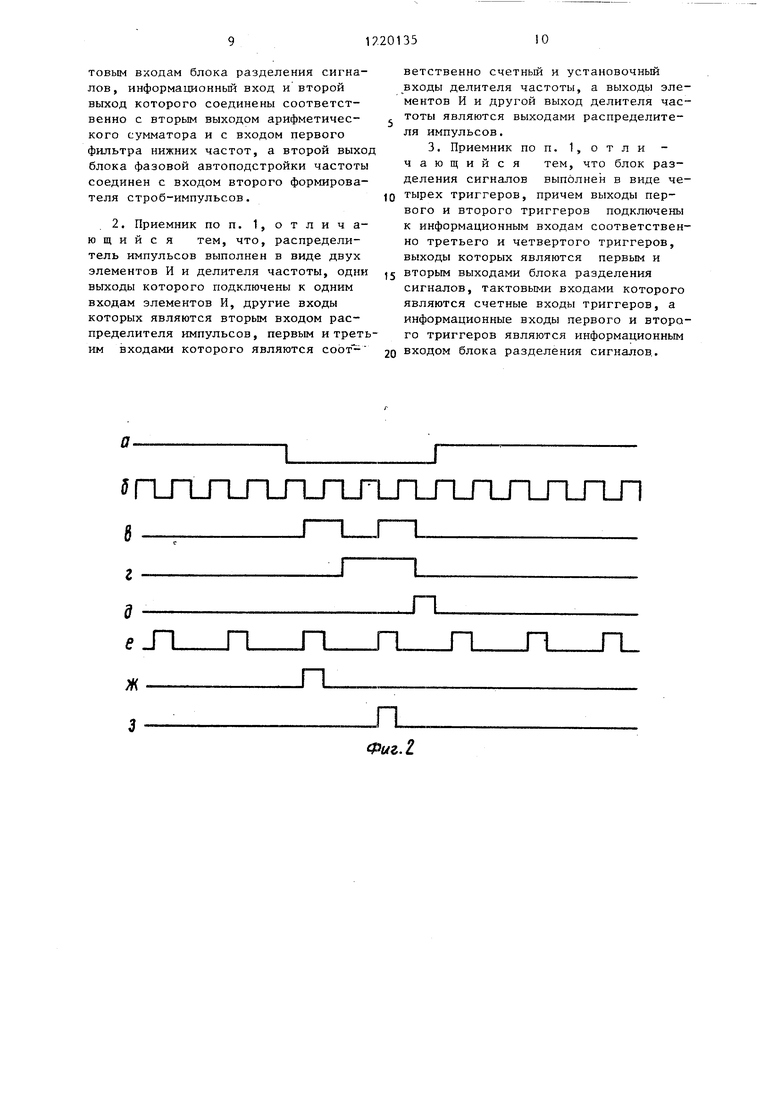

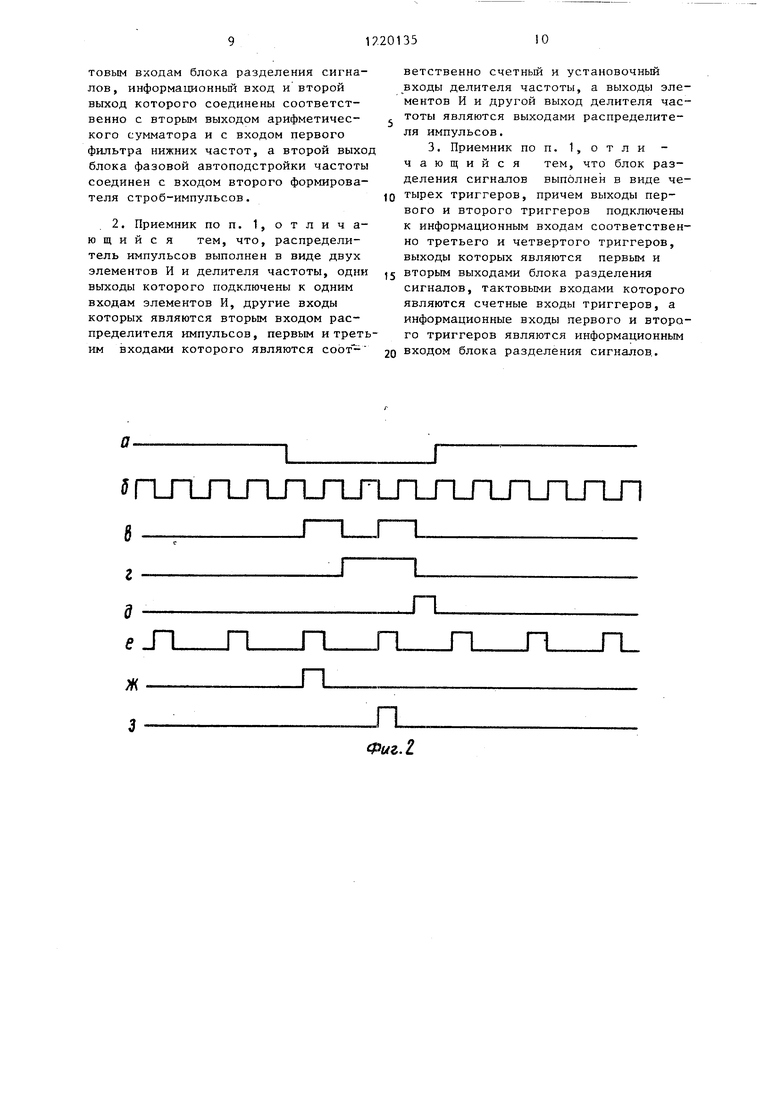

На фиг. 1 изображена структурно- электрическая схема устройства; на фиг. 2 - эпюры напряжений, поясняющие работу распределителя импульсов; на фиг. 3 - эпюры напряжений, поясняющие работу устройства в целом.

Приемник сигналов с двойной фазовой манипуляцией содержит полосовой фильтр 1, формирователь 2 импульсов, блок 3 фааовой автоподстройки частоты, элемент 4 задержки, арифметический сумматор 5, первый 6 и второй 7 формирователи строб-импульсов, распределитель 8 импульсов, блок 9 разделения сигналов, первый 10 и второй 11 фильтры нижних частот,первый выходной блок 12 сопряжения и второй выходной блок 13 сопряжения, причем распределитель 8 импульсов содержит два элемента И 14 и 15 и делитель 16 частоты, а блок 9 разделения сигналов содержит первый 17, второй 18, третий 19 и четвертый 20 триггеры.

Устройство работает следующим об- - разом.

Одновременное прохождение двух сообщений по каналу без распшрения спектра сигнала достигается за счет обеспечени;я способности принимать сигнал с фазовым уплотнением, т.е. за счет возможности различать четьфе варианта манипуляции фазы несущих колебаний. При этом во всех вариантах производится манипуляция фазы на 180°. По соображениям простоты реализации выбраны следующие варианты манипуля- ции: , , 270. Кажтоты 16 располагается в конце интер- вала анализа после импульсов на выходах элементов И 14, 15. Элементы И 14, 15 выполняют дешифрацию и стробирование 2-х состояний делителя частоты 16. 2 з.п. ф-лы. З-ил.

дьм вариант манипуляции фазы кодирует один из четырех возможных кодов, образуемых двумя двоичными сигналами, . каждый из которых можно рассматри- вать как отдельное сообщение, независимое от другого.

Обнаружение одного из вариантов манипуляции фазы несущих колебаний позволяет однозначно восстановить

по одной посьшке из двух независимых сообщений, передаваемых одновременно по каналу связи с обычной для него скоростью. При этом спектр канального сигнала не расширяется, так

как круговая частота манипуляции остается неизменной, а дополнительная информация вносится в сигнал за счет использования большего числа вариантов манипуляции фазы несущих

колебаний.

Колебания несущей частоты, вьще- ленные полосовым фильтром 1 из входного сигнала, преобразуются формиро-, вателем 2 импульсов в прямоугольные

импульсы. Они поступают на второй вход арифметического сумматора 5 непосредственно, а на первый вход - ерез элемент 4 задержки, сдвигающий х на половину периода колебаний несущей частоты. До тех пор, пока фаза несуи их колебаний не манипулирована, на первом выходе арифметического : сумматора 5 постоянно присутствует потенциал логической единицы, а на

втором выходе арифметического суматора 5 - потенциал логического нуля.

Если в колебаниях несущей частоты появ,гшется манипуляция фазы, то на

первом выходе арифметического суматора 5 устанавливается потенциал огического нуля на время, равное половине периода следования импульсов несущей частоты. Сигнал на вто3

ром выходе арифметического сумматор 5 в течение этого времени может быт различен, но полностью и однозначно определяется вариантом манипуляции колебаний несущей частоты.

Рассмотрение сигнала на втором выходе арифметического сумматора 5 в то время, как на первом выходе прсутствует потенциал логического нуля показывает, что его можно восприни- мать как последовательный двухразряный двоичный код, который для различных вариантов манипуляции имеет следующие значения: О - -180°- код 11 180°- 0°- код 00; 90°- 270°- код 10 270°- 90°- код 01.

Это позволяет отождествить код на втором выходе арифметического сумматора 5 с кодом, образованным одновременно передаваемьпчи элемен- тарными посьшками двух независимых сигналов. После этого устройство разделяет разряды этого кода в два отдельных канала. При этом один разряд кода выражает значение при- нятой элементарной посылки первого канала, а другой - второго канала.

Таким образом, для правильного разделения двух независимых сигналов, передаваемых по одному каналу путем фазового уплотнения, необходимо проанализировать структуру двоичного кода, появлякицегося на втором выходе арифметического сумматора 5. Это выполняет блок 9 разделения сигналов. Анализ проводится в течение интервала времени, пока на первом выходе арифметического сумматора 5 присутствует потенциал логического нуля.

Анализ заключается в следукяцем. Интервал анализа разбивается на две части. Сначала сигнал со второго выхода арифметического сумматора 5 заносится в первый триггер 17, а затем во второй триггер 18. После записи информации во второй триггер 18 последовательный двоичный код со второго выхода арифметического сумматора 5 оказывается преобразованны в параллельньш код, первый разряд которого хранится в первом триггере 17, а второй - во втором триггере 1 Но разряды этого кода формируются в разное время, т.е. когда в первый триггер 17 заносится первый разряд кода со второго выхода арифметическго сумматора 5, во втором триггере 18 еще хранится значение второго

5

о 5

5

0

5

0

5

0

135

разряда такого же кода, но от предыдущего момента манипуляции фазы несущих колебаний. Оно заменяется новым значением только после зане-- сения во второй триггер 18 нового кода. Эти моменты разнесены на четверть периода колебаний несущей частоты. Поэтому на выходе первого 17 и второго 18 триггеров сигналы, разделенные на два канала, имеют посто- янньш сдвиг по фазе на четверть периода колебаний несущей частоты. Чтобы устранить этот сдвиг, содержимое первого 17 и второго 18 триггеров параллельным кодом переписывается в третий 19 и четвертый 20 триггеры после того, как записывается информация во второй триггер 18. В результате на выходе блока 9 разделения сигналов элементарные посылки двух независимых сообщений оказываются строго синхронизированными по времени. Эта синхронность сохраняется и на выходе устройства.

Следовательно, для правильной работы устройства операции в блоке 9 разделения сигналов должны выполняться в строго определенные моменты времени. Они определяются распределителем 8 импульсов, формирующим тактовые импульсы для триггеров блока 9 разделения сигналов. Эти импульсы располагаются во времени так, чтобы импульс на выходе элемента И 14 находился на середине первой половины интервала анализа, а импульс на выходе элемента И 15 - на середине второй половины этого интервала. Импульс на выходе делителя 16 частоты располагается в самом конце интервала анализа после импульсов на выходах элементов И 14 и 15 (фиг. 2сх,д,ж,| ).

Эти импульсы формируются следующим образом. Из выходных сигналов блока 3 фазовой автоподстройки час- тоты формирователи 6 и 7 строб-импульсов формируют две последовательности импульсов, вид и взаимное расположение которых показаны на фиг. 2с и е . Первая из них поступает на вход делителя 16 частоты, состоящего из трех счетных триггеров, установочные входы которых соединены с первым выходом арифметического сумматора 5. До тех пор, пока нет манипуляции фазы несущих .колебаний, там присутствует постоянная логи- (ческая единица. Этот потенциал принудительно удерживает на выходах

триггеров потенциалы логического нуля (фиг. 26,г,о) и этим запрещает прохождение импульсов на выходы элементов И 14 и 15 (фиг. 2ж, i,).

В момент изменения фазы несущих колебаний на первом выходе арифметического сумматора 5 появляется потенциал логического нуля (фиг. .2 ) на время, равное половине периода несущих колебаний. Его можно рас- . сматривать как отрицательный импульс на первом выходе арифметического сумматора 5. Он расположен вполне определенным образом относительно последовательностей импульсов на выходах формирователей 6 и 7 строб- импульсов (фиг. 2а, S , е ). Такое расположение обеспечивается блоком 3 фазовой автоподстройки частоты, фазирующим свои выходные сигналы под колебания несущей частоты. Последовательности импульсов, сформированные из этих сигналов, тоже оказываются зафазированными под те же самые колебания.

При появлении импульса на первом выходе арифметического сумматора 5 принудительная установка снимается с триггеров делителя 16 частоты. Они начинают деление частоты первой последовательности импульсов (фиг.2с, &, г , ). После окончания четвертого импульса этой последовательности появляется задний фронт импульса на первом выходе арифметического сумматора 5 и триггеры делителя 16 частоты снова принудительно устанавливаются по установочным входам потенциалом логической единицы. За счет этого на выходе третьего триггера 19 делителя 16 частоты формируется узкий импульс (фиг. ).

Элементы И 14 и 15 выполняют дешифрацию и стробирование двух состояний делителя 16 частоты. При этом на их выходы проходят стробирующие импульсы в моменты, когда делитель 16 частоты оказьшается в дешифрируе™ мом состоянии. На выход элемента И 14 он проходит, когда на выходе первого триггера 17 делителя 16 частоты присутствует потенциал логической единицы, а на выходе второго 18 - потенциал логического нуля (фиг. 26, г, е ,ж). На выход элемента И 15 он проходит, когда на выходе второго триггера 18 делителя 16 частоты присутствует потенциал логической единицы (фиг. 26, г ,е ,3 ).

В реальных условиях, при наличии

помех, входной сигнал устройства поражен краевыми искажениями, что выражается в том, что прямоугольные импульсы, сформированные из колебаний несущей частоты, а также интервалы

между ними могут быть не равны половине номинального периода колебаний несущей частоты. Это приводит к тому, что на первом и втором выходах арифметического сумматора 5 появляются. ложные результаты арифметического суммирования в моменты прихода фронтов искаженных прямоугольных импульсов входного сигнала. Но зти ложные результаты не могут исказить

сигнал в блоке 9 разделения сигналов так как тактовые импульсы для триггеров этого блока формируются со смещением относительно искажающихся

фронтов. Это видно из фиг. 2а,тк, 1,

если учесть, что искаженные фронты импульсов входного сигнала совпали бы с фронтами или с серединой отрицательного импульса на фиг. 2а.

Смещение тактовых сигналов обеспечивает запись информации в триггере, когда на выходах арифметического сумматора 5 уже устанавливаются истинные результаты суммы и переноса. При этом появление ложных результатов в промежутках между моментами манипуляции фазы несущих колебаний не оказывает никакого влияния на работу устройства, т.ак как ложные сигналы на первом выходе арифметического

сумматора слишком узки для того, чтобы под их воздействием сформировались тактовые импульсы в распределителе 8 импульсов. Поэтому блок 9 разделения сигналов на них не реагирует.

На фиг. За начало временных диаграмм построено для случая, когда моменту манипуляции фазы предшествовал вариант манипуляции 180°- 0°. Поэтому на выходах всех триггеров 17 20 блока 9 разделения сигналов присутствует потенциал логического нуля (фиг, ). Это состояние сохраняется до нового момента манипуляции фазы колебаний несущей частоты, который производится по варианту .

В этот момент на первом выходе арифметического сумматора 5 уста:нав- ливается потенциал логического нуля

на время, равное половине периода колебаний несущей (фиг. За, 6 ). На втором его выходе на это же время устанавливается, потенциал логической единицы (фиг, Зо,г ). Этот потенциал блок 9 разделения сигналов рассматривает как последовательный двухразрядный код, отдельные разряды которого должны быть записаны в триггеры 17 и 18. Причем первый разряд записывается в первый триггер 17, а второй - во второй триггер 18. Для этого на информационные входы этих триггеров поступают регистрирующие строб-импульсы (фиг. Зк, л) соответственно с выходов элементов И 14 и 15, входящих в состав распределителя 8 им- . пульсов. Процесс формирования этих импульсов распределителем 8 импульсов .представляет собой дешифрацию со стробированием состояний делителя 16 частоты, входящего в состав распределителя 8 импyJгьcoв (фиг. 3 - /i) Для формирования требуются две последовательности импульсов (фиг.З.и формируемые из сигналов, снимаемых с выходов делителя частоты, входящего в блок 3 фазовой автоподстройки частоты. Для определенности на фиг. Зр показан вид сигнала с выхода последнего триггера делителя 16 частоты. Фазировка этого сигнала, например, взята такой, что фронты импульсов несущей частоты, под которые производится фазирование, совпадают с задними фронтами импульсов на фиг. ЗР, а период следования по общему правилу построения устройств фазовой автоподстройки частоты выбран равным минимальной длительности элемента входного сигнала. Эта длительность, которую можно рассматривать как элементарную посылку, равна четверти периода колебаний несущей частоты, что видно при рассмотрении фиг. За в моменты манипуляции по вариантам 90°- -270° и наоборот. Сравнение фиг. Зр и Зи показывает,что для формирования.последовательности импульсов, поступающих на вход делителя 16 частоты, необходимо использовать сигнал, снимаемый по крайней мере с одного из внутренних триггеров делителя частоты, входящего в блок 3 фазовой автоподстройки частоты.

Сформированные строб-импульсы совпадают с серединами соответственно первой и второй половин полупе- риода колебаний несущей (фиг. За ,к,л). Запись значений кода переноса в триггеры 17 и 18 блока 9 разделения сигналов происходит в момент начала строб-импульсов (фиг. За, м и Зл,н). После записи значения второго разряда кода переноса, содержимое первого и второго триггеров 17 и 18 переписьшается в третий и четвертый триггера 19 и 20 (фиг. Sj, о, и , м , ч ).

Сравнение состояния триггеров 17 - и 18 после очередной манипуляции фазы с кодами, обозначающими эти варианты, показьтает что при манипуляции 0°- 180°в оба триггера 17

и 18 записьшается логическая единица; при манипуляции 90 - 270 в первый триггер 17 записьгоается логическая единица, а во второй триггер 18 - логический ноль, при манипуляции 270°- 90° в первый триггер записывается логический ноль, а во второй триггер 19 - логическая единица.

Формула изобретения

1. Приемник сигналов с двойной фазовой манипуляцией, содержащий последовательно соединенные полосовой фильтр, формирователь импульсов, элемент задержки и арифметический сумматор , последовательно соединенные блок фазовой автоподстройки частоты и первый формирователь строб-импульсов, последовательно соединенные первый фильтр нижних частот и первый выходной блок сопряжения, причем выход формирователя импульсов подключен к входу блока фазовой автоподстройки частоты и к второму входу арифметического сумматора, отличающийся тем, что, с целью увеличения объема принимаемой информации, в него введены последовательно соединенные блок разделения сигналов, второй фильтр нижних частот и второй выходной блок сопряжения, последовательно соединенные второй формирователь строб-импульсов и распределитель импульсов, второй и третий входы которого соединены соответственно с выходом первого формирователя стробг импульсов и с первым вькодом арифметического сумматора, выходы распределителя импульсов подключены к тактовым входам блока разделения сигналов, информационньш вход и второй выход которого соединены соответственно с вторым выходом арифметического сумматора и с входом первого фильтра нижних частот, а второй выхо блока фазовой автоподстройки частоты соединен с входом второго формирователя строб-импульсов.

2. Приемник по п. 1, отличающийся тем, что, распределитель импульсов выполнен в виде двух элементов И и делителя частоты, одни выходы которого подключены к одним входам элементов И, другие входы которых являются вторым входом распределителя импульсов, первым и третьим входами которого являются RJ J JTnJHJlJT J-LTUT-JlTLn

ветственно счетный и установочный входы делителя частоты, а выходы элементов И и другой выход делителя частоты являются выходами распределителя импульсов.

3, Приемник по п. 1, о т л и чающийся тем, что блок разделения сигналов выполнен в виде тырех триггеров, причем выходы первого и второго триггеров подключены к информационным входам соответственно третьего и четвертого триггеров, выходы которых являются первым и

J5 вторым выходами блока разделения

сигналов, тактовыми входами которого являются счетные входы триггеров, а информационные входы первого и второго триггеров являются информационным

2Q входом блока разделения сигналов..

Фиг. I

27(90°

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник сигналов с двойной фазовой манипуляцией | 1985 |

|

SU1264370A2 |

| Приемник сигналов с двойной фазовой манипуляцией | 1986 |

|

SU1443198A1 |

| Приемник сигналов с трехкратной фазовой манипуляцией | 1989 |

|

SU1628219A1 |

| Устройство для приема фазоманипулированных сигналов | 1980 |

|

SU1062887A1 |

| Когерентный приемник частотно-манипулированных радиосигналов с непрерывной фазой | 1990 |

|

SU1716615A1 |

| Приемник сигналов офсетной фазовой манипуляции | 1987 |

|

SU1434559A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Устройство контроля параметров движения транспортного средства | 2019 |

|

RU2741668C1 |

Изобретение относится к области телеграфной связи. Цель изобретения - увеличение объема принимаемой информации. Одновременное прохождение 2-х сообщений по каналу без расшире. кия спектра сигнала достигается за счет обеспечения способности-принимать сигнал с фазовым уплотнением, т.е. за счет возможности различать 4 варианта манипуляции фазы несущих колебаний. Для правильного разделения 2-х независимых сигналов, передаваемых по одному каналу путем фазового уплотнения, надо проанализировать структуру двоичного кода, появляющегося на 2-м выходе арифметического сумматора 5. Это выполняет блок разделения сигналов (БРС) 9. Для правильной работы устройства операции в БРС 9 должны вьтолняться в строго определенные моменты времени. Они определяются распределителем импульсов 8, формирующим тактовые импульсы для триггеров 17-20 БРС 9. Эти импульсы располагаются во вре± (Л

| ЗаездныЙ A.M | |||

| и др | |||

| Фазоразност- ная модуляция н ее применение для передачи дискретной информации.-М. | |||

| Связь, 1967, с | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Устройство для приема фазоманипулированных сигналов | 1980 |

|

SU1062887A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-03-23—Публикация

1983-12-22—Подача