1

Изобретение относится к специализированной вычислительной технике, предназначено для получения динамических характеристик исследуемых систем и может найти применение при анализе и синтезе технических, биологических и гибридных систем Под динамическими характеристиками исследуемых систем понимается набор ядер Винера , которьй однозначно и полностью описывает поведение системы, позволяет построить модель, адекватную реальному объекту с наперед заданной точностью. Наиболее широкое распространение получил взаимокорреляционный метод вычисления таких характеристик, который предполагает, что на вход системы при проведении эксперимента поступал идеальный белый гауссовский шум Однако создание такого тестирующего процесса невозможно, поэтому на практике используется входной сигнал, отличный от белого шума, что приводит к ошибкам в определении динамических характеристик.

Целью изобретения является повышение точности вычисления динамических характеристик систем

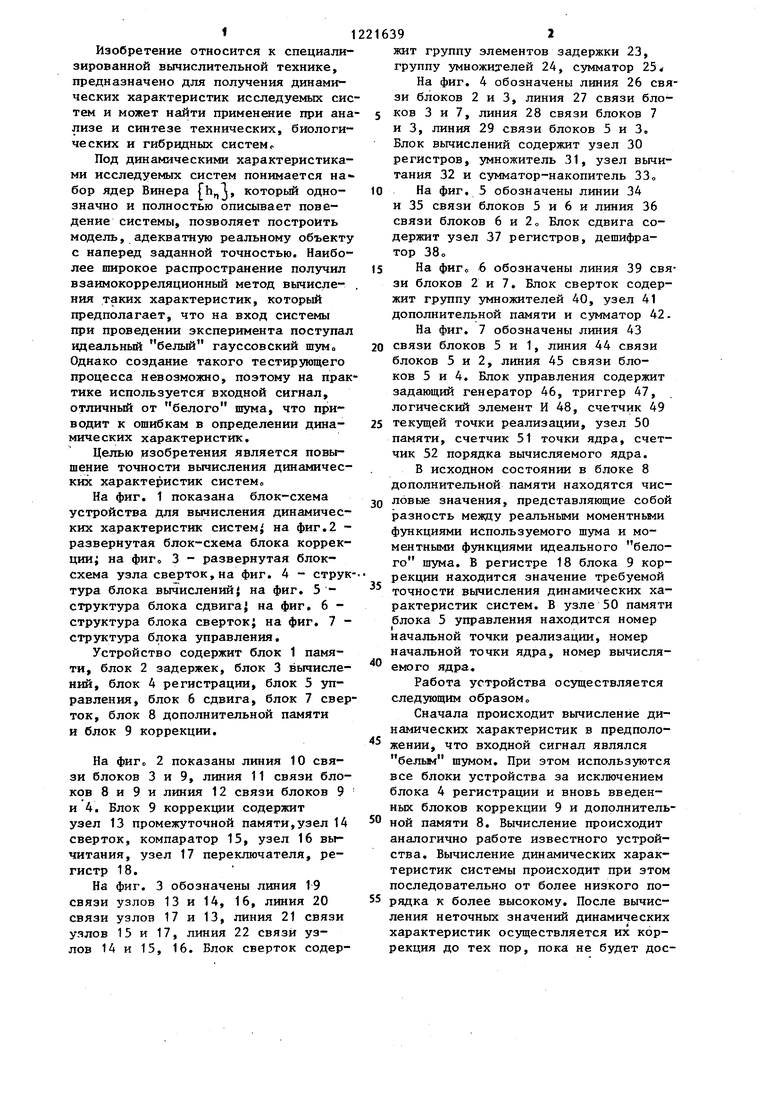

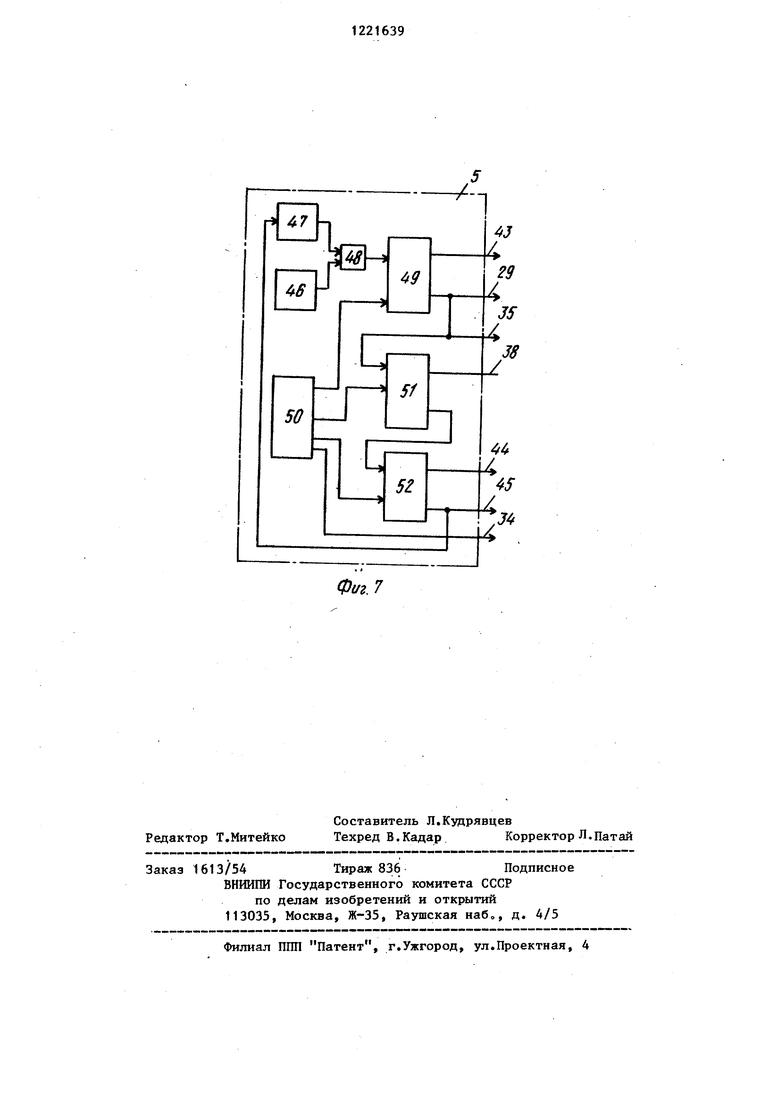

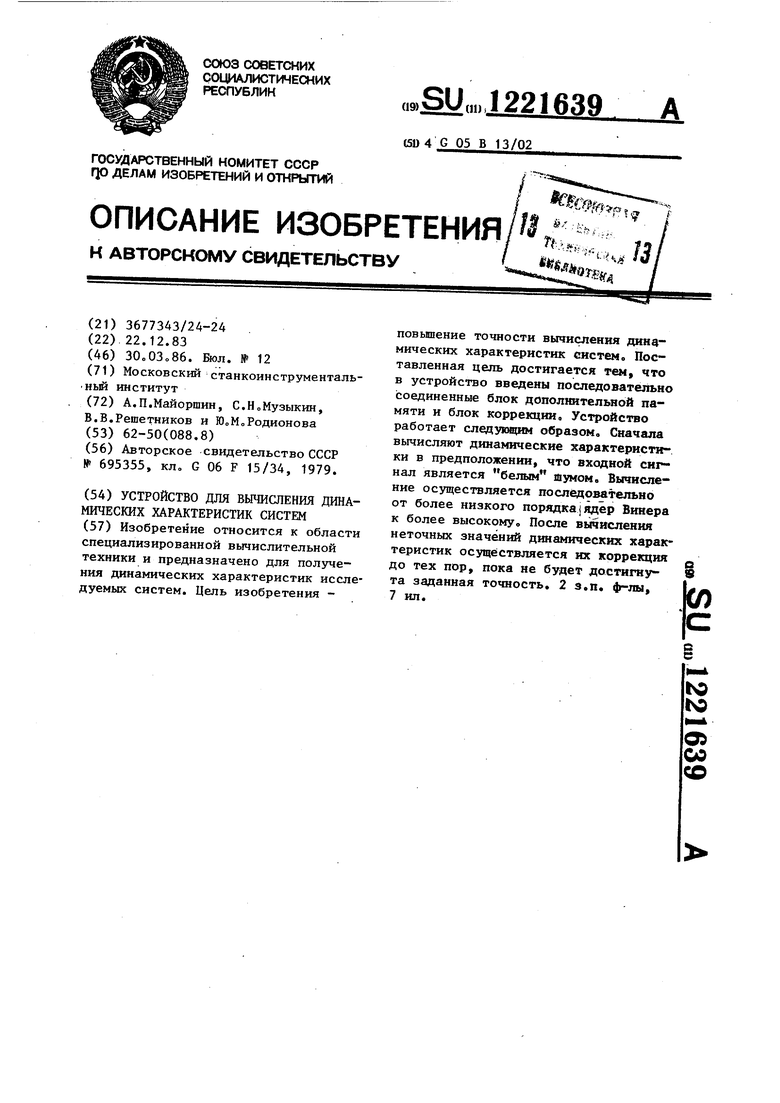

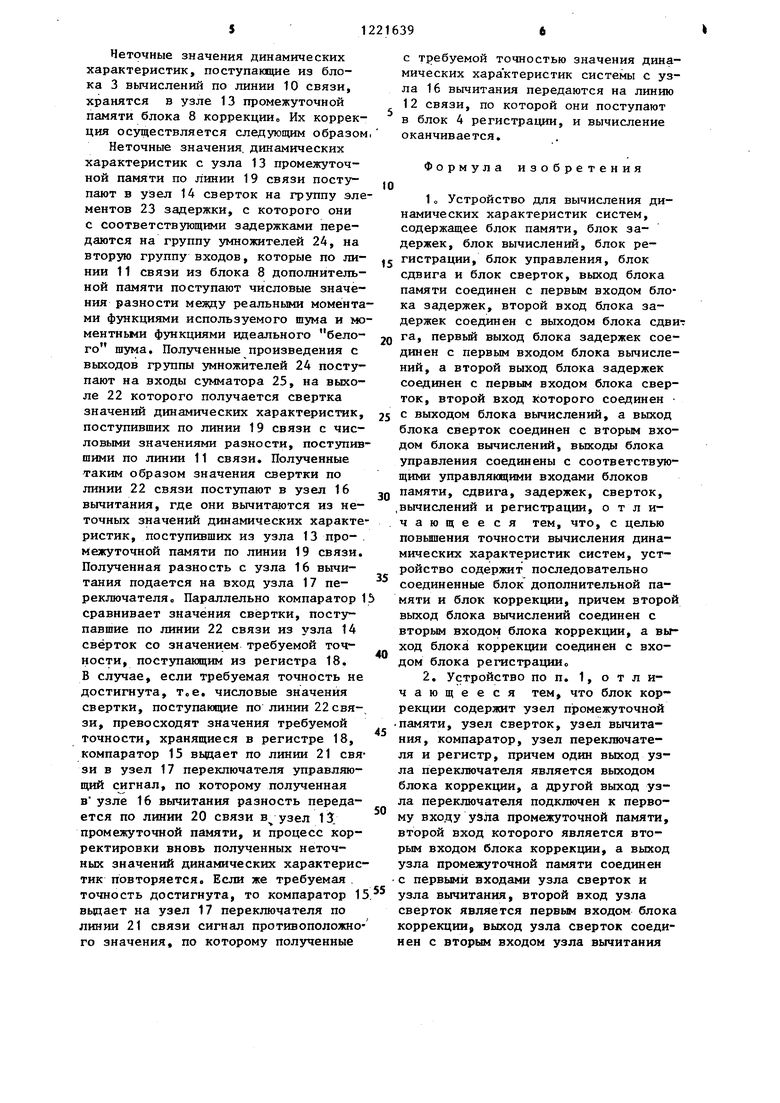

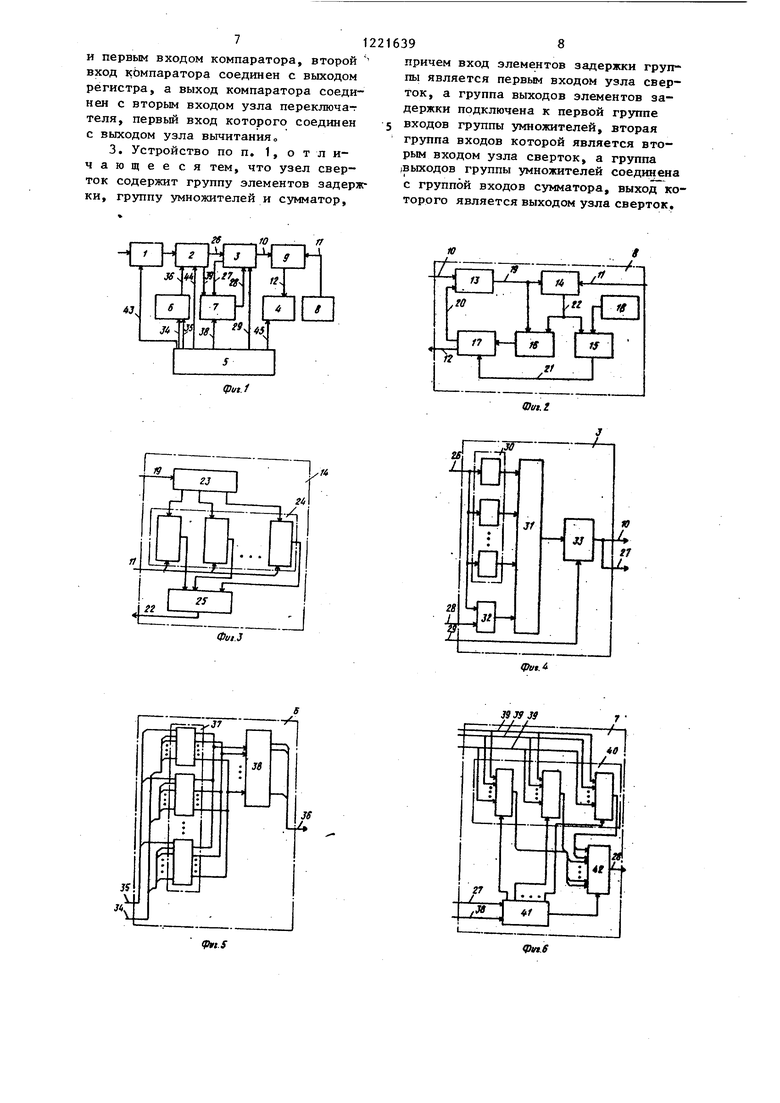

На фиг. 1 показана блок-схема устройства для вычисления динамических характеристик систем на фиг.2 - развернутая блок-схема блока коррекции; на фиго 3 - развернутая блок- схема узла сверток, на фиг. 4 - структура блока вычислений} на фиг. 5 - структура блока сдвигаJ на фиг. 6 - структура блока сверток; на фиг. 7 - структура блока управления.

Устройство содержит блок 1 памяти, блок 2 задержек, блок 3 вычислений, блок 4 регистрации, блок 5 управления, блок 6 сдвига, блок 7 сверток, блок 8 дополнительной памяти и блок 9 коррекции.

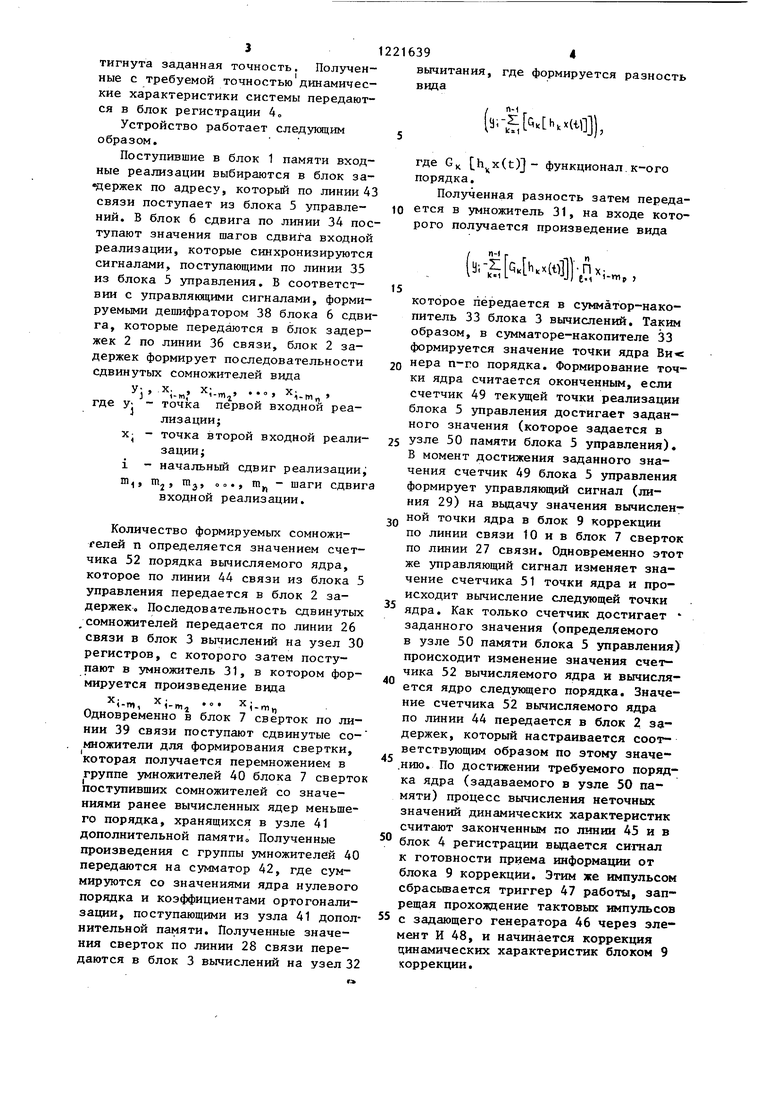

На фиго 2 показаны линия 10 связи блоков 3 и 9, линия 11 связи блоков 8 и 9 и линия 12 связи блоков 9 и 4. Блок 9 коррекции содержит узел 13 промежуточной памяти,узел 14 сверток, компаратор 15, узел 16 вычитания, узел 17 переключателя, регистр 18.

На фиг. 3 обозначены линия 19 связи узлов 13 и 14, 16, линия 20 связи узлов 17 и 13, линия 21 связи узлов 15 и 17, линия 22 связи узлов 14 и 15, 16. Блок сверток содер216392

жит группу элементов задержки 23, группу умножителей 24, сумматор 25

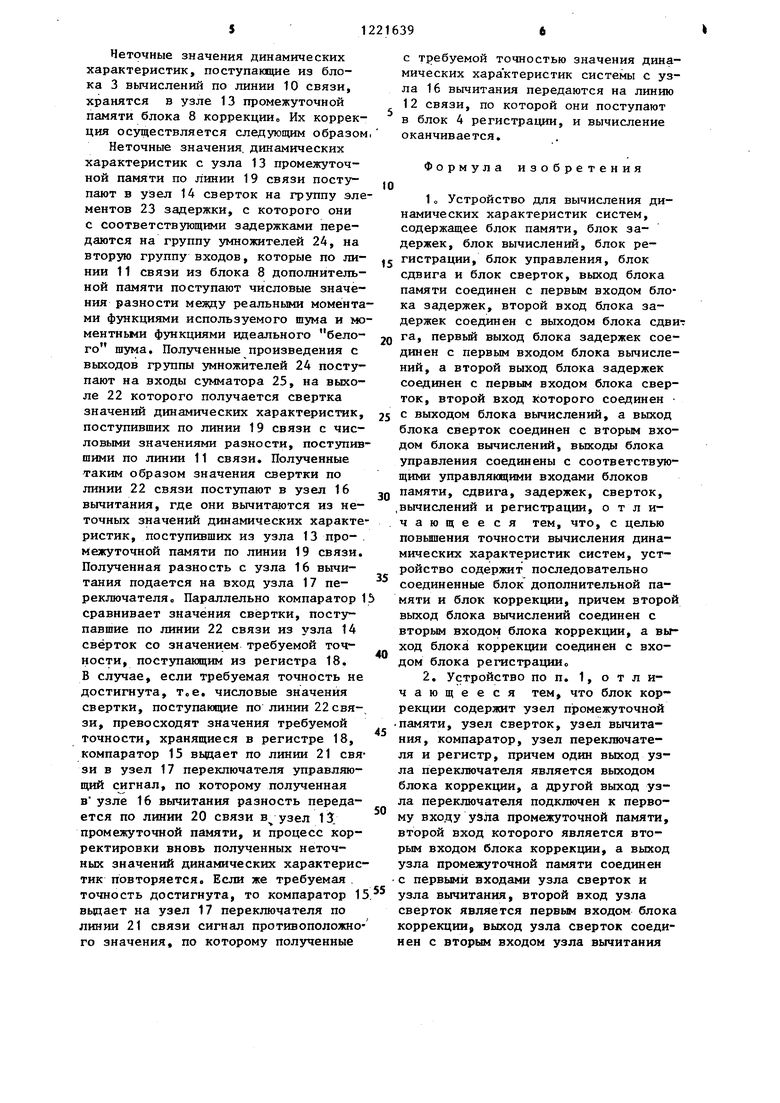

На фиг. 4 обозначены линия 26 связи блоков 2 и 3, линия 27 связи бло- 5 °в 3 и 7, линия 28 связи блоков 7 и 3, линия 29 связи блоков 5 и 3, Блок вычислений содержит узел 30 регистров, умножитель 31, узел вычитания 32 и сумматор-накопитель 33,

10 На фиг. 5 обозначены линии 34 и 35 связи блоков 5 и 6 и линия 36 связи блоков 6 и 2о Блок сдвига содержит узел 37 регистров, дешифратор 38 о

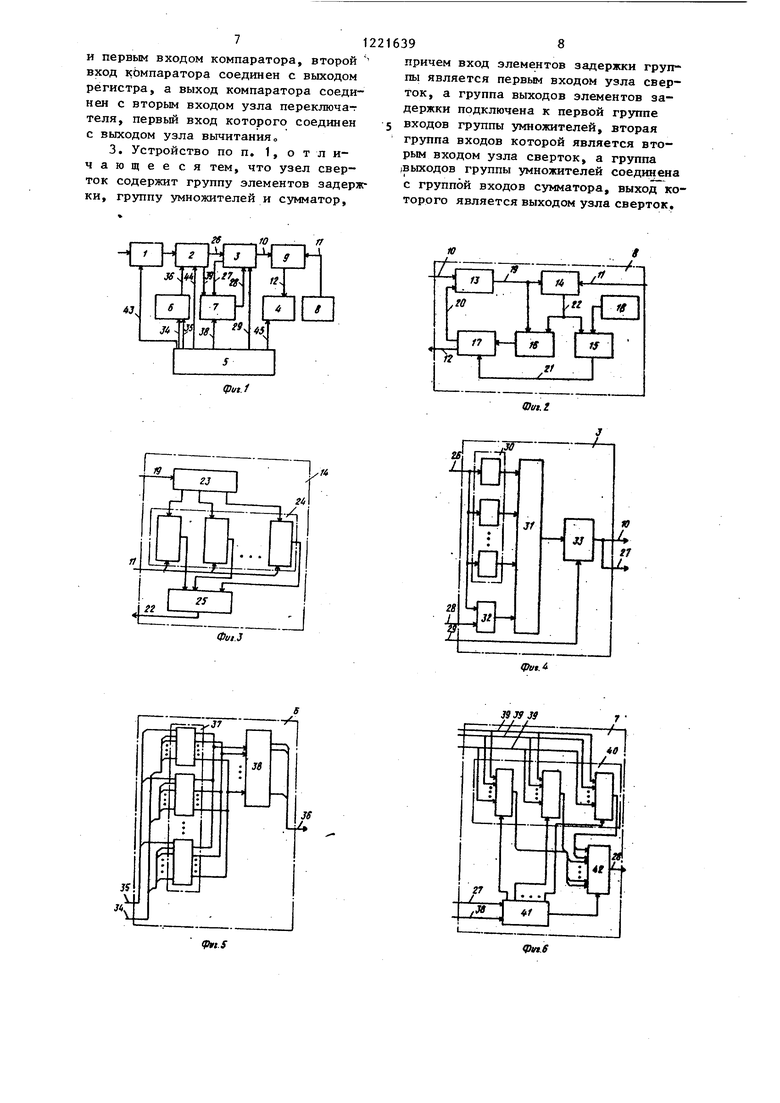

15 На фиго 6 обозначены линия 39 связи блоков 2 и 7. Блок сверток содержит группу умножителей 40, узел 41 дополнительной памяти и сумматор 42- На фиг. 7 обозначены линия 43

20 связи блоков 5 и 1, линия 44 связи блоков 5 и 2, линия 45 связи блоков 5 и 4. Блок управления содержит задающий генератор 46, триггер 47, логический элемент И 48, счетчик 49

25 текущей точки реализации, узел 50 памяти, счетчик 51 точки ядра, счетчик 52 порядка вычисляемого ядра. В исходном состоянии в блоке 8 дополнительной памяти находятся чис-

30 ловые значения, представляющие собой разность между реальными моментньми функциями используемого шума и мо- ментными функциями идеального белого шума. В регистре 18 блока 9 коррекции находится значение требуемой точности вычисления динамических характеристик систем. В узле 50 памяти блока 5 управления находится номер начальной точки реализации, номер начальной точки ядра, номер вычисляемого ядра.

Работа устройства осуществляется следующим образомо

Сначала происходит вычисление динамических характеристик в предполо жении, что входной сигнал являлся белым шумом. При этом используются все блоки устройства за исключением блока 4 регистрации и вновь введенных блоков коррекции 9 и дополнитель50 ной памяти 8. Вычисление происходит аналогично работе известного устройства. Вычисление динамических характеристик системы происходит при этом последовательно от более низкого по55 рядка к более высокому. После вычисления неточных значений динамических характеристик осуществляется их коррекция до тех пор, пока не будет дос35

40

тигнута заданная точность. Полученные с требуемой точностью динамические характеристики системы передаются в блок регистрации 4

Устройство работает следующим образом.

Поступившие в блок 1 памяти входные реализации выбираются в блок за- «держек по адресу, которьй по линии 43 связи поступает из блока 5 управлений. В блок 6 сдвига по линии 34 поступают значения шагов сдвига входной реализации, которые синхронизируются сигналами, поступающими по линии 35 из блока 5 управления. В соответствии с управляюцими сигналами, формируемыми дешифратором 38 блока 6 сдвига, которые передаются в блок задержек 2 по линии 36 связи, блок 2 задержек формирует последовательности сдвинутых сомножителей вида

J

X. ,

t-m,

i-m первой входной реаде у- - точка

лизации;

х- - точка второй входной реализации ; i - начальный сдвиг реализации

m

га.

2 00.,

ВХОДНОЙ реализации.

га - шаги сдвига

Количество формируемых сомножителей п определяется значением счетчика 52 порядка вычисляемого ядра, которое по линии 44 связи из блока 5 управления передается в блок 2 задержек. Последовательность сдвинутых /сомножителей передается по линии 26 связи в блок 3 вычислений на узел 30 регистров, с которого затем поступают в умножитель 31, в котором формируется произведение вица

(-т, i-rtii i-m Одновременно в блок 7 сверток по линии 39 связи поступают сдвинутые со- множители для формирования свертки, которая получается перемножением в группе умножителей 40 блока 7 сверток ПОСТ5Т1ИВШИХ сомножителей со значениями ранее вычисленных ядер меньшего порядка, хранящихся в узле 41 дополнительной памяти. Полученные произведения с группы умножителей 40 передаются на сумматор 42, где суммируются со значениями ядра нулевого порядка и коэффициентами ортогонали- зации, поступающими из узла 41 дополнительной памяти. Полученные значения сверток по линии 28 связи передаются в блок 3 вычислений на узел 32

вычитания, где формируется разность вида

пч

(.h,.(ii),

где G (t)J - функционал.к-ого порядка.

Полученная разность затем переда- ется в умножитель 31, на входе которого получается произведение вида

(li;-| Q.h.x(t)}.nxi.

,

15

которое передается в сумматор-накопитель 33 блока 3 вычислений. Таким образом, в сумматоре-накопителе 33 формируется значение точки ядра Ви нера п-го порядка. Формирование точки ядра считается оконченным, если счетчик 49 текущей точки реализации блока 5 зшравления достигает заданного значения (которое задается в узле 50 памяти блока 5 управления), В момент достижения заданного значения счетчик 49 блока 5 управления формирует управляющий сигнал (линия 29) на вьщачу значения вычисленной точки ядра в блок 9 коррекции по линии связи 10 и в блок 7 сверток по линии 27 связи. Одновременно этот же управляющий сигнал изменяет значение счетчика 51 точки ядра и происходит вычисление следующей точки ядра. Как только счетчик достигает заданного значения (определяемого в узле 50 памяти блока 5 управления) происходит изменение значения счетчика 52 вычисляемого ядра и вычисляется ядро следующего порядка. Значение счетчика 52 вычисляемого ядра по линии 44 передается в блок 2 задержек, который настраивается соответствующим образом по этому значе- .нию. По достижении требуемого порядка ядра (задаваемого в узле 50 памяти) процесс вычисления неточных значений динамических характеристик считают законченным по линии 45 и в блок 4 регистрации задается сигнал к готовности приема информации от блока 9 коррекции. Этим же импульсом сбрасьшается триггер 47 работы, запрещая прохоядение тактовых импульсов с задающего генератора 46 через элемент И 48, и начинается коррекция динамических характеристик блоком 9 коррекции.

Неточные значения динамических характеристик, поступакщие из блока 3 вычислений по линии 10 связи, хранятся в узле 13 промежуточной памяти блока 8 коррекциио Их коррек- ция осуществляется следующим образом

Неточные значения, динамических характеристик с узла 13 промежуточной памяти по линии 19 связи посту- пают в узел 14 сверток на группу элементов 23 задержки, с которого они с соответствующими задержками передаются на группу умножителей 24, на вторую группу входов, которые по ли- НИИ 11 связи из блока 8 дополнительной памяти поступают числовые значения разности между реальными моментами функциями используемого шума и мо ментньми фзшкциями идеального бело- го шума. Полученные произведения с выходов группы умножителей 24 поступают на входы сумматора 25, на выхо- ле 22 которого получается свертка значений динамических характеристик, поступивших по линии 19 связи с числовыми значениями разности, поступившими по линии 11 связи Полученные таким образом значения свертки по линии 22 связи поступают в узел 16 вычитания, где они вычитаются из неточных значений динамических характеристик, поступивших из узла 13 промежуточной памяти по линии 19 связи. Полученная разность с узла 16 вычитания подается на вход узла 17 пе- реключателяо Параллельно компаратор 1 сравнивает значения свёртки, поступавшие по линии 22 связи из узла 14 свёрток со значением требуемой точности, поступающим из регистра 18. В случае, если требуемая точность не достигнута, т.е. числовые значения свертки, поступающие по линии 22 связи, превосходят значения требуемой точности, хранящиеся в регистре 18, компаратор 15 выдает по линии 21 связи в узел 17 переключателя управляющий сигнал, по которому полученная в узле 16 вычитания разность передается по линии 20 связи в узел 13 промежуточной памяти, и процесс корректировки вновь полученных неточных значений динамических характеристик повторяется. Если же требуемая . точность достигнута, то компаратор 15 вьщает на узел 17 переключателя по линии 21 связи сигнал противоположного значения, по которому полученные

. .- j., 25 -

0

5

0

с требуемой точностью значения динамических хара ктеристик системы с узла 16 вычитания передаются на линию 12 связи, по которой они поступают в блок 4 регистрации, и вычисление оканчивается.

Формула изобретения

1 о Устройство для вычисления динамических характеристик систем, содержащее блок памяти, блок задержек, блок вычислений, блок регистрации, блок управления, блок сдвига и блок сверток, выход блока памяти соединен с первым входом блока задержек, второй вход блока задержек соедршен с выходом блока сдви-: га, первый выход блока задержек соединен с первым входом блока вычислений, а второй выход блока задержек соединен с первым входом блока сверток, второй вход которого соединен с выходом блока вычислений, а выход блока сверток соединен с вторым входом блока вычислений, выходы блока управления соединены с соответствующими управляющими входами блоков памяти, сдвига, задержек, сверток, вычислений и регистрации, отличающееся тем, что, с целью повьшения точности вычисления динамических характеристик систем, устройство содержит последовательно соединенные блок дополнительной памяти и блок коррекции, причем второй выход блока вычислений соединен с вторым входом блока коррекции, а выход блока коррекции соединен с входом блока регистрации

2. Устройство по п. 1, отличающееся тем, что блок коррекции содержит узел промежуточной памяти, узел сверток, узел вьгаита- ния, компаратор, узел переключателя и регистр, причем один выход узла переключателя является выходом блока коррекции, а другой выход узла переключателя подключен к первому входу уэла промежуточной памяти, второй вход которого является вторым входом блока коррекции, а выход узла промежуточной памяти соединен с первыми входами узла сверток и узла вычитания, второй вход узла сверток является первым входом блока коррекции, выход узла сверток соединен с вторым входом узла вычитания

и первым входом компаратора, второй вход компаратора соединен с выходом регистра, а выход компаратора соединен с вторым входом узла переключа-г теля, первый вход которого соединен с выходом узла вычитания

3. Устройство по п. 1, отличающееся тем, что узел сверток содержит группу элементов задержки, группу умножителей и сумматор.

причем вход элементов задержки группы является первым входом узла сверток, а группа выходов элементов задержки подключена к первой группе входов группы умножителей, вторая группа входов которой является вторым входом узла сверток, а группа выходов группы умножителей соединена с группой входов сумматора, выход которого является выходом узла сверток.

-.«

п

фиг.1

Фп.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Обучающее устройство | 1984 |

|

SU1244699A1 |

| Устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей | 1986 |

|

SU1325516A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| СПОСОБ ПРИЕМА МНОГОЛУЧЕВОГО СИГНАЛА, СПОСОБ ПОИСКА И СПОСОБ ФОРМИРОВАНИЯ МЯГКИХ РЕШЕНИЙ ПРИ ПРИЕМЕ МНОГОЛУЧЕВОГО СИГНАЛА И УСТРОЙСТВА, ИХ РЕАЛИЗУЮЩИЕ | 2003 |

|

RU2251802C1 |

| Система полунатурного моделирования динамических систем | 1982 |

|

SU1121681A1 |

| ДИСКРЕТНАЯ СИСТЕМА ОЦЕНИВАНИЯ | 2007 |

|

RU2398258C2 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| Устройство для вычисления спектра сигналов | 1989 |

|

SU1667102A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

Изобретение относится к области специализированной вычислительной техники и предназначено для ния динамических характеристик исследуемых систем. Цель изобретения повьипение точности вычисления динамических характеристик системе Поставленная цепь достигается тем, что в устройство введены последовательно соединенные блок дополнительной памяти и блок коррекции. Устройство работает следующим образом. Сначала вычисляют динамические характеристики в предположении, что входной сигнал является бельм шумом. Вычисление осуществляется последовательно от более низкого порядка{ядер Винера к более высокому. После вычисления неточных значений дииамических харак теристик осуществляется их коррекция до тех пор, пока не будет достигнута заданная точность. 2 з.п. ф-лы, 7 ил. СО 1C N9 Од 00 со

п.«

3S

39JS 39

tpn.S

ф1П.6

4J

Фаг. 7

| Авторское свидетельство СССР № 695355, кло G 06 F 15/34, 1979. |

Авторы

Даты

1986-03-30—Публикация

1983-12-22—Подача