112

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования аналоговых величин в цифровые.

Цель изобретения - повышение быстродействия аналого-цифрового преобразователя.

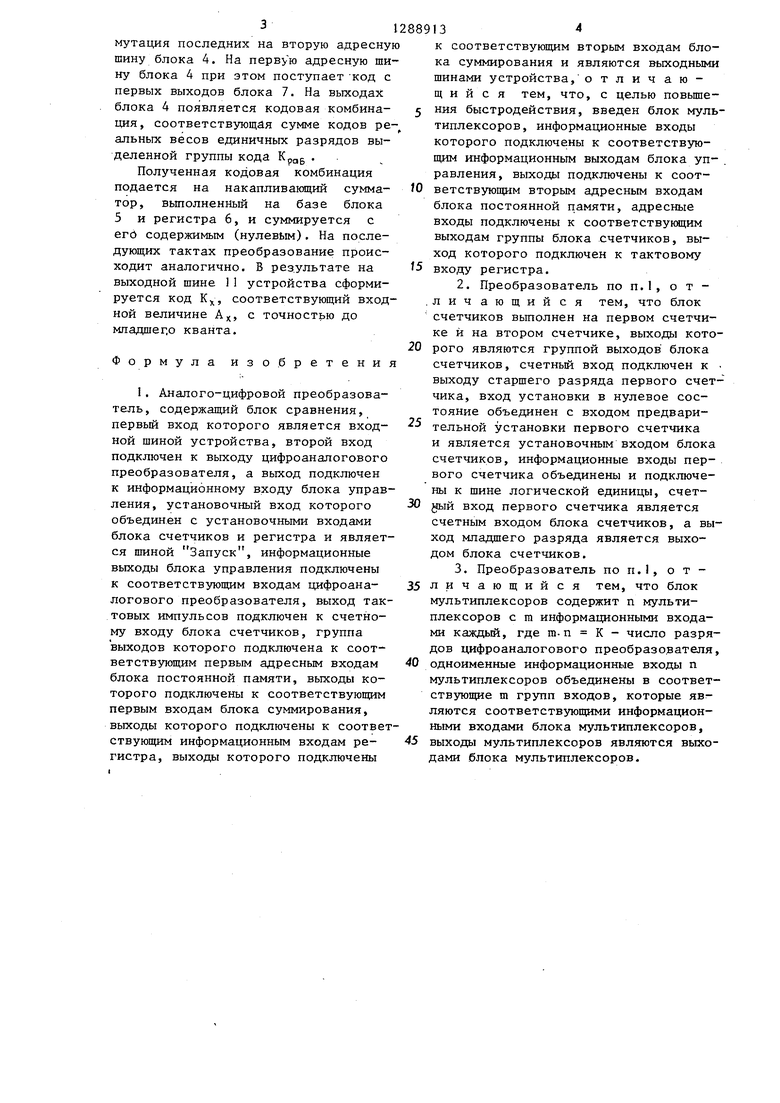

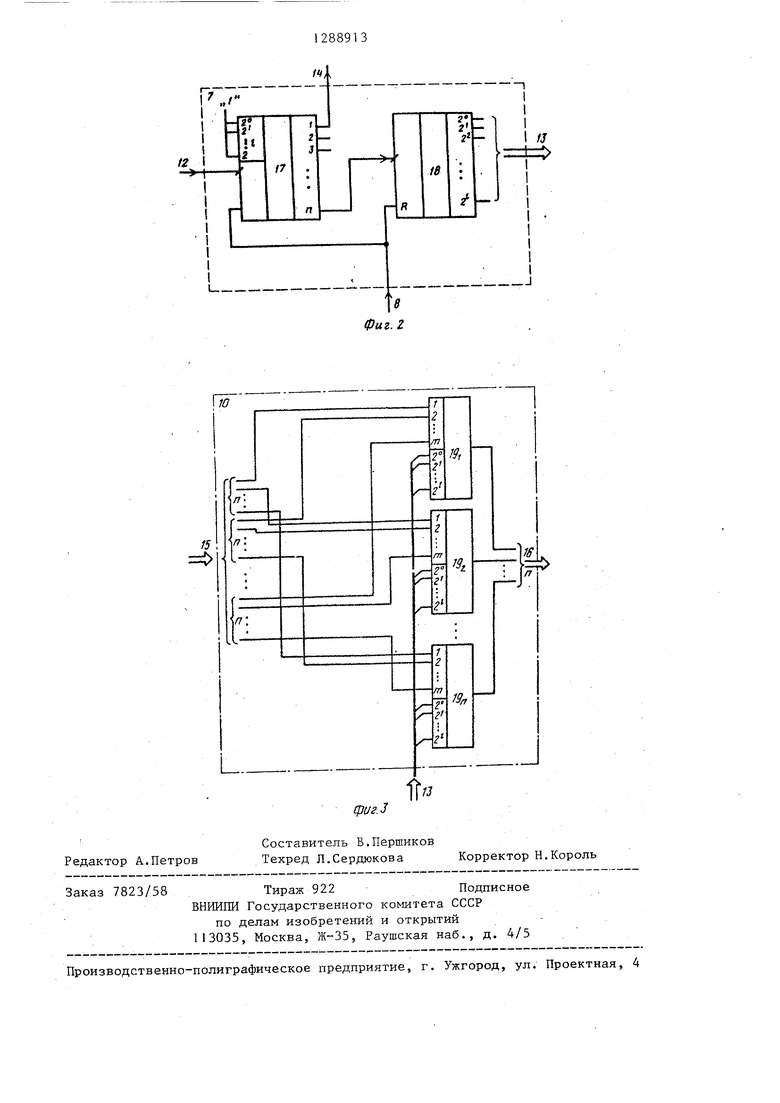

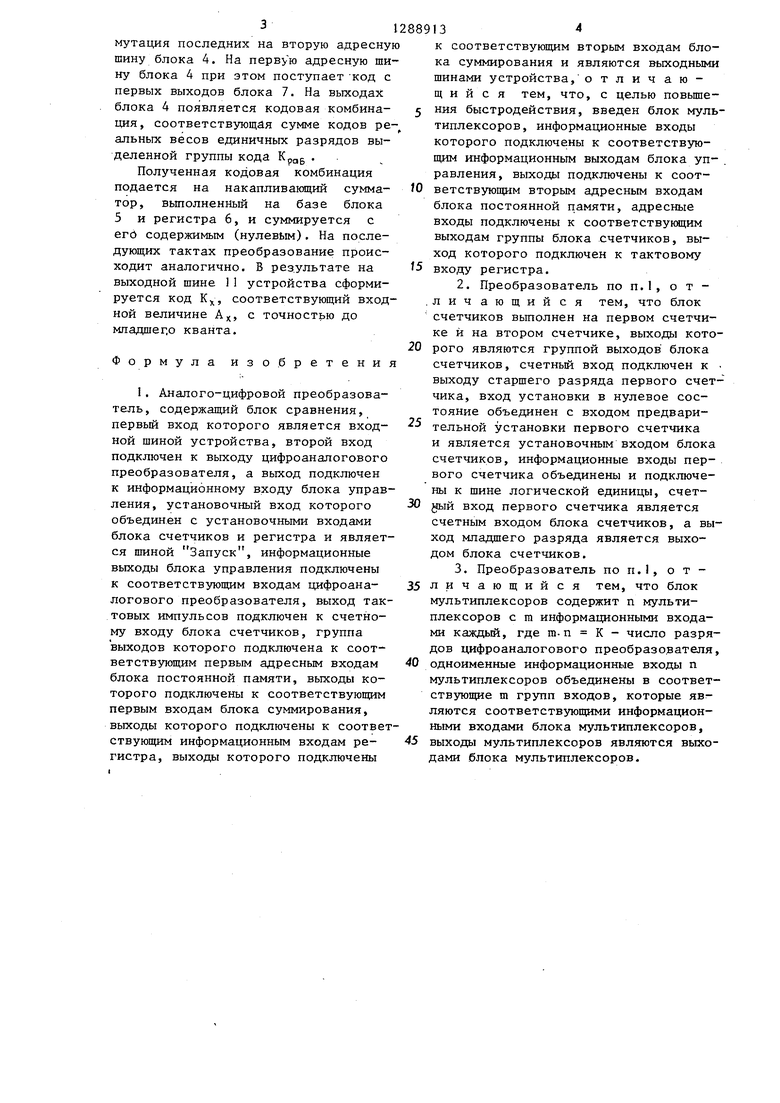

На. фиг.1 приведена функциональная схема аналого-цифрового преобразова- теля; на фиг.2 - функциональная схема блока счетчиков; на фиг.З - функциональная схема блока мультиплексоров.

Аналого-цифровой преобразователь (фиг.1) содержит блок 1 сравнения, цифроаналоговый преобразователь 2 (ЦАП), блок 3 управления, блок 4 постоянной памяти, блок 5 суммирования, регистр 6, блок 7 счетчиков, шину 8 Запуск, входную шину 9, блок 10 мультиплексоров, выходные шины 11.

Блок 7 счетчиков содержит счетный вход 12, группу выходов 13 и выход 14. Блок 10 мультиплексоров содержит информационные входы 15 и выходы 16. Блок 7 счетчиков (фиг.2) выполнен на первом счетчике 17 и втором счетчике 18. Блок 10 мультиплексоров (фиг.З) выполнен на и мультиплексорах 19 ( - 19f|. ЦАП 2 должен быть выполнен на основе избыточного измерительного кода (ИИК).

Любое действительное число в ИИК можно представить в виде

N Z: а;..

где а;6 о,1j - двоичная цифра в i-M разряде кода; oi - вес 1-го разряда кода, причем 2,

06

Одним из избыточных измерительных кодов является код Фибоначчи.

Предлагаемое устройство функционирует в режиме аналого-цифрового преобразователя по методу поразрядного кодирования и осуществляет два преоб- разования: аналог - рабочий код (Кра) и рабочий код (Крд,) - двоичный код (Kj). .

В результате первого преобразования происходит компенсация входного аналогового сигнала Ag компенсирующим сигналом А ЦАП 2 и формирование кода Kpgg. В результате второго преобразования для получения требуемой

0

5

0

-

132

точности происходит коррекция кода КpQg путем его преобразования в двоичный код К.

Осуществляют групповую обработку разрядов при коррекции кода Кр . Для этого при изготовлении устройства определяются коды реальных значений весов разрядов ЦАП 2, ток и коды, соответствующие некоторым суммам кодов реальных значений весов разрядов. Причем разряды ЦАП 2 разбиваются на m группы по п разрядов таким образом, чтобы

к

m --- ,

где К - количество разрядов ЦАП 2.

При этом анализируется 2 возйож- ных комбинаций для каждой группы разрядов . Данные комбинации определяются как суммы кодов реальных весов единичных разрядов каждой группы и записываются в БПП4.

Устройство работает следующим образом.

По шине 8 Запуск поступает импульс запуска, устанавливающий блок З управления в исходное состояние, обнуляющий регистр 6, второй счетчик 18 в блоке 7 и устанавливающий первый счетчик 17 в блоке 7 в состоянии п.

В процессе преобразования входного аналогового сигнала А в выходной код К производится уравновешивание АХ выходным компенсирующим сигналом ЦАП 2 . Процесс уравновешивания производится блоком 3 управления последовательно от старших разрядов к младшим по методу поразрядного кодирования. При этом на каждом i-м Такте на выходе ЦАП 2 формируется аналоговый сигнал А ,; .

С помощью блока 1 сравнения производится сравнение А с А,,- . Выходной сигнал Y блока 1 сравнения удовлетворяет следующему условию:

i

1, О,

если А А. ;

если

f-

55

С помощью блока 1, ЦАП 2 и блока 3 на информационных выходах последнего формируются разряды кода Kpgg. Причем, на (п + 1)-м такте аналого- цифрового преобразователя после того, как на выходе блока 3 сформируется п разрядов кода Крд, происходит ком

мутация последних на вторую адресную шину блока 4. На первую адресную шину блока 4 при этом поступает код с первых выходов блока 7. На выходах блока 4 появляется кодовая комбинация , соответствующая сумме кодов реальньгх весов единичных разрядов выделенной группы кода КраБ .

Полученная кодовая комбинация подается на накапливающий сумматор, вьшолненный на базе блока 5 и регистра 6, и суммируется с егб содержимым (нулевым). На последующих тактах преобразование происходит аналогично. В результате на выходной шине 11 устройства сформируется код К, соответствующий входной величине А, с точностью до мпадшег.о кванта.

Формула изо.бретения

1

Аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого является входной шиной устройства, второй вход подключен к выходу цифроаналогового преобразователя, а выход подключен к информационному входу блока управления, установочный вход которого объединен с установочными входами блока счетчиков и регистра и является шиной Запуск, информационные выходы блока управления подключены к соответствующим входам цифроаналогового преобразователя, выход тактовых импульсов подключен к счетному входу блока счетчиков, группа выходов которого подключена к соответствующим первым адресным входам блока постоянной памяти, выходы которого подключены к соответствующим первым входам блока суммирования, выходы которого подключены к соотвествующим информационным входам регистра, выходы которого подключены

5

0

к соответствующим вторым входам блока суммирования и являются выходными шинами устройства, отличающийся тем, что, с целью повьш1е- 5 ния быстродействия, введен блок мультиплексоров, информационные входы которого подключены к соответствующим информационным выходам блока уп- . равления, выходы подключены к соот- ветствующим вторым адресным входам блока постоянной памяти, адресные входы подключены к соответствующим выходам группы блока счетчиков, выход которого подключен к тактовому входу регистра.

2.Преобразователь по п.1, о т - личающийся тем, что блок счетчиков вьтолнен на первом счетчике и на втором счетчике, выходы которого являются группой выходов блока счетчиков, счетньй вход подключен к выходу старшего разряда первого счетчика, вход установки в нулевое состояние объединен с входом предварительной установки первого счетчика

и является установочным входом блока счетчиков, информационные входы первого счетчика объединены и подключены к шине логической единицы, счет- ый вход первого счетчика является счетным входом блока счетчиков, а выход младшего разряда является выходом блока счетчиков.

3.Преобразователь по п.1, о т - 5 личающийся тем, что блок

мультиплексоров содержит п мультиплексоров с m информационными входами каждый, где т-п К - число разрядов цифроаналогового преобразователя,

0 одноименные информационные входы п мультиплексоров объединены в соответствующие m групп входов, которые являются соответствуюш ими информационными входами блока мультиплексоров,

5 выходы мультиплексоров являются выходами блока мультиплексоров.

5

0

Редактор А.Петров

Составитель В.Першиков Техред Л.Сердюкова

Заказ 7823/58Тираж 922Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий - 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг.З

1Т

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство преобразования информации | 1978 |

|

SU769730A1 |

Изобретение относится к области измерительной и вычислительной техники и может быть использовано для преобразования аналоговых величин в цифровые. Аналого-цифровой преобразователь содержит блок 1 сравнения, цифроаналоговый преобразова- тель 2, блок 3 управления, блок 4 постоянной памяти, блок 5 суммирования, регистр 6, блок 7 счетчиков, шину 8 запуск, входную шину 9, блок 10 мультиплексоров, выходные шины 11. Введенный блок 10 мультиплексоров обеспечивает последовательно-параллельное преобразование избыточного измерительного кода, получаемого на информационных выходах блока управления, в выходной двоичный код, что обеспечивает повышение д быстродействия аналого-.цифрового пре- образователя. 2 з.п. ф-лы, 3 нл. (Л (Pl/2.f

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-07—Публикация

1985-07-08—Подача